# NXP AN11208 Cortex-M0 Application note

http://www.manuallib.com/nxp/an11208-cortex-m0-application-note.html

This application note describes the IEC60335 Class B certified library for the NXP ARM Cortex-M0 family members. All tests implemented and the library usage are described in detail.

ManualLib.com collects and classifies the global product instrunction manuals to help users access anytime and anywhere, helping users make better use of products.

http://www.manuallib.com

AN11208 NXP LPC Cortex-M0 IEC60335 Class B library Rev. 1.1 – 22 January 2014

**Application note**

## **Document information**

| Info     | Content                                                                                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | NXP ARM Cortex-M0, IEC60335 Class B, VDE, LPC1100, LPC1200                                                                                                                            |

| Abstract | This application note describes the IEC60335 Class B certified library for the NXP ARM Cortex-M0 family members. All tests implemented and the library usage are described in detail. |

#### Cortex-M0 IEC60335 Class B library

#### **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 1.1 | 20140122 | Minor edits.     |

| 1   | 20120601 | Initial version. |

## **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

AN11208 Application note All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 2 of 76

## 1. Introduction

Modern day home appliances require a certain level of protection in order to avoid hazardous situations if the appliance fails. Since 2007, home appliances must comply with the IEC60335 standard. Home appliance manufacturers therefore need to ensure that the requirements are met.

This document describes the IEC60335 standard requirements with respect to software for microcontrollers and the implementation of these requirements. NXP has developed a software library for the NXP ARM Cortex-M0 family, based on these requirements; this document discusses the tests and the usage of these tests in detail.

#### ATTENTION!

The usage of this library does not make a certified application of your project. It is still necessary to have the complete application software certified.

This library should not be changed, and it should be used as explained. Otherwise, a new certification for the changed parts will be necessary.

The library is usable, as-is, for **all** NXP ARM Cortex-M0 products, including those not specifically mentioned in this application note.

## 1.1 How to read this application note

This application note is a guide in using and implementing the library functions provided. It will first discuss the requirements the IEC60335 standard sets, and then briefly discuss the products the library is developed for.

The main part of the document describes how the Class B tests are done and how it can and should be implemented. Details on the tested peripherals are given in the last chapter.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 3 of 76

## 2. IEC60335 Class B

The IEC60335 standard specifies design enhancements for home appliance manufacturers that design appliances with electronic controls and controls using software with respect to safe and reliable operation. This standard requires inclusion of features that will avoid or at least minimize the change of hazardous situations when the appliance fails.

Referring to IEC60730, this deals with standard various assets of safety and reliability precautions required to be taken for all home appliances. Annex H of the IEC60730 standard software and hardware requirements are defined to be taken in order to comply with this standard.

## 2.1 Software classification

Within the IEC60730 Annex H, details for testing and diagnostic implementation in microcontroller software are classified as A, B or C.

- Class A: Control functions which are not intended to be relied upon for the safety of the equipment.

- Class **B**: Control functions intended to prevent unsafe operation of the controlled equipment.

- Class **C**: Control functions which are intended to prevent special hazards (e.g. explosion of the controlled equipment such as burner controls).

The majority of home appliances, like white goods (refrigerator, dishwasher, cooker etc.) and personal appliances (electrical tooth brush, shaver etc.), require the Class B level of precautions.

IEC60370 Class B specifies that measures must be taken to avoid software related faults and errors in data and segments of the software that are safety related. Periodic monitoring of the system therefore is required.

## 2.2 Class B components

Table H.11.12.7 of IEC60730 Annex H specifies the components to be tested and monitored during operation of the controller. <u>Table 1</u> shows a summary of table H.11.12.7.

Table 1. IEC60335 Class B tests as defined by IEC60730 Annex H

| Test<br>number        | Component                                               | Fault/error                                                                         | In<br>library      |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|

| 1.1.                  | CPU registers                                           | Stuck at                                                                            | YES                |

| 1.3.                  | Program Counter                                         | Stuck at                                                                            | YES                |

| 2.                    | Interrupt handling and execution                        | No interrupt or too frequent interrupt                                              | YES                |

| 3.                    | Clock                                                   | Wrong frequency (for quartz<br>synchronized clock: harmonics/<br>subharmonics only) | YES <sup>[1]</sup> |

| 4.1.                  | Invariable memory                                       | All single bit faults                                                               | YES                |

| 4.2.                  | Variable memory                                         | DC Fault                                                                            | YES                |

| 4.3.                  | Addressing (relevant to variable and invariable memory) | Stuck at                                                                            | YES                |

| 5.1. <sup>[2]</sup>   | Internal data path                                      | Stuck at                                                                            | NO                 |

| 5.2. <sup>[2]</sup>   | Addressing                                              | Wrong address                                                                       | NO                 |

| 6.                    | External communications                                 | Hamming distance 3                                                                  | NO                 |

| 6.3.                  | Timing                                                  | Wrong point in time and sequence                                                    | NO                 |

| 7. <sup>[3]</sup>     | Input/output periphery                                  | Fault conditions specified in H.27                                                  | NO                 |

| 7.2.1. <sup>[3]</sup> | A/D and D/A converters                                  | Fault conditions specified in H.27                                                  | NO                 |

| 7.2.2. <sup>[3]</sup> | Analog multiplexer                                      | Wrong addressing                                                                    | NO                 |

|                       |                                                         |                                                                                     | NO                 |

[1] Only applicable of the NXP ARM Cortex-M0 family members with RTC domain.

[2] Only when using external memory.

[3] Production plausibility check.

AN11208

## 3. NXP ARM Cortex-M0 microcontrollers

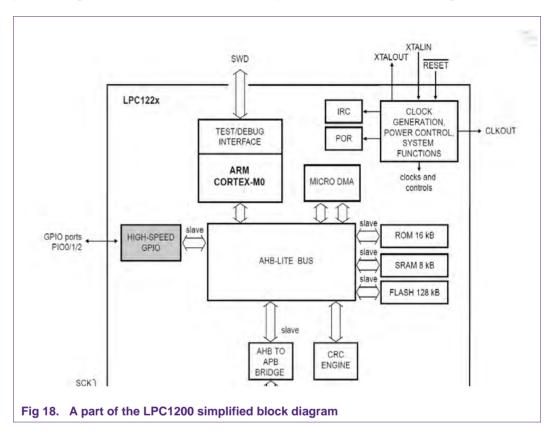

This chapter gives a general description of the NXP ARM Cortex-M0 family members for which the IEC60335 Class B self-test libraries are written.

## 3.1 The NXP ARM Cortex-M0 microcontrollers

The NXP LPC1100(L) is the world's first Cortex-M0 based microcontroller series. It offers users a cost-effective, very easy-to-use 32-bit MCU which is code- and tool-compatible with other NXP ARM-based MCU products. With 32-bit performance and multiple power modes including very low, deep sleep power, the LPC1100(L) series offers industry-leading energy efficiency, greatly extending battery life. The LPC1100(L) series sets new benchmarks in performance efficiency with dramatically improved code density enabling longer battery life and lower system costs.

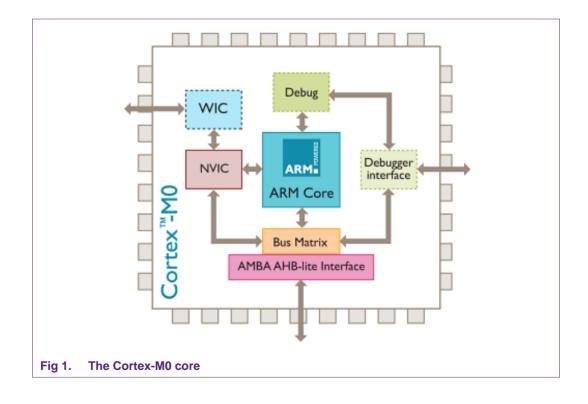

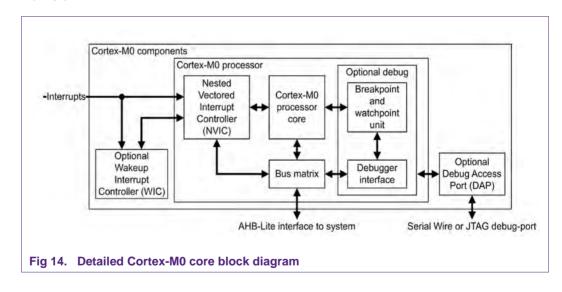

## 3.1.1 The ARM Cortex-M0 core

The ARM Cortex-M0 processor is the smallest, lowest-power and most energy-efficient ARM processor available. The exceptionally small silicon area, low power, and minimal code footprint of the processor achieves 32-bit performance at an 8-bit price point, bypassing the step to 16-bit devices.

The Cortex-M0 processor promises substantial savings in system cost while retaining tool and binary compatibility with feature-rich processors such as the Cortex-M0 processor. It consumes as little as 85 microwatts/MHz (0.085 milliwatts) in an area of typically under 12 K gates, enabling the creation of ultra low-power analog and mixed signal devices.

The Cortex-M0 processor is built on a highly area and power optimized 32-bit processor core, with a 3-stage pipeline von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0 processor implements the ARMv6-M architecture, which is based on the 16-bit Thumb instruction set and includes Thumb-2 technology. This provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

The Cortex-M0 processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- Includes a non-maskable interrupt (NMI). The NMI is not implemented on the LPC111x/LPC11Cxx.

- Provides zero jitter interrupt option.

- Provides four interrupt priority levels.

The tight integration of the processor core and NVIC provides fast execution of interrupt service routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes that include a Deep-sleep function that enables the entire device to be rapidly powered down.

## 3.2 Product options

The NXP Cortex-M0 product portfolio is growing rapidly. Discover the latest ARM Cortex-M0 processors on our website:

http://www.nxp.com/products/microcontrollers/cortex\_m0\_m0/

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 7 of 76

## 4. IEC60335 Class B library

The chapter gives an overview about the functionality of the various functions and illustrates how the functions are implemented. It gives you knowledge about the library and helps with understanding the self-test philosophy. Please note by changing any library functionality it need to be re-certified again. If a special part needs to be modified, then there will be an explicit description and explanation.

## 4.1 POST and BIST

POST (Pre Operation System Test) means the testing as part of the start-up procedure. These tests are destroyable, i.e., the data contents are not restored after executing the test. Also, in this state of application, there are normally no interrupts active.

Note, at start-up all tests must be executed: CPU registers, PC, RAM and ROM. For this reason special POST functions are available. The POST testing is developed such that it reduces test time and therefore is monolithic and destroyable.

For runtime testing or Build-In System Test (Build-In System Test), the test functions are non-destructible. To avoid system failures in time critical applications, these test are not monolithic. Functions are implemented for testing the variable and non-variable in smaller blocks.

The POST routines for testing the CPU registers, the variable memory (RAM) and invariable memory (Flash) are available as separate modules, and should be run in sequence at system startup (after reset).

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 8 of 76

## 4.2 CPU Register Test (1.1)

## 4.2.1 Test description

As described in <u>Chapter 5.1</u> the ARM Cortex-M0 core has a number of registers used during program execution. Nineteen of these registers are read/write.

Since these registers are all used during program execution in the various core operation modes, they are tested for stuck-at faults and direct coupling faults.

These tests are to be executed as POST and BIST. POST testing is a destroyable test, so the CPU registers are not retained. Since the POST CPU register tests don't retain register data, it is mandatory to execute this test prior any other application or system initialisation. Preferably execute this test prior to branch to main.

CPU BIST testing isn't destroyable, so all data is restored after testing. To decrease test time and therefore CPU resources, the CPU register BIST testing is divided into five separate tests. The first three test the general purpose registers, the fourth tests the stack pointer. To prevent the system from crashing, all interrupts and exceptions are disabled while running this part of the CPU register BIST. The fifth and last BIST test will test the other special registers.

Both BIST and POST use the same test methodology when testing the registers. First, a pattern is stored in the register, then read back and compared. Then, the inverse of that pattern is stored in the register, read and compared.

#### 4.2.1.1 Failure

If a failure in the POST testing occurs, a function hook has been implemented. The user has the option to handle a failing CPU POST test by implementing the \_\_CPUpostTestFailureHook function.

The basic pattern used for the CPU register tests is the following:

- Normal: 0xAAAA.AAAA

- Inverted: 0x5555.55555

AN11208 Application note

## 4.2.2 Test usage

This chapter describes the files used and summarizes all function calls used in CPU register POST and BIST testing.

The tests are developed in assembly code since for POST the CPU registers need to be tested before branching to the main routine. The C environment (stack, initialised variables, and zero initialised variables) is not available at the time the POST test needs to be performed. Additionally, the CPU register test POST does not require usage of memory.

The BIST tests are developed in assembly code because most of the registers of the core are not directly accessible from C code.

#### 4.2.2.1 IEC60335\_B\_CPUregTest.h

| File name               | Function prototyping                                       |  |  |

|-------------------------|------------------------------------------------------------|--|--|

| IEC60335_B_CPUregTest.h | <pre>type_testResult IEC60335_CPUregTest_BIST(void);</pre> |  |  |

|                         | <pre>extern void _CPUregTestLOW(void);</pre>               |  |  |

|                         | <pre>extern void _CPUregTestMID(void);</pre>               |  |  |

|                         | <pre>extern void _CPUregTestHIGH(void);</pre>              |  |  |

|                         | <pre>extern void _CPUregTestSP(void);</pre>                |  |  |

|                         | <pre>extern void _CPUregTestSPEC(void);</pre>              |  |  |

|                         | Type definition                                            |  |  |

|                         | IEC60335_CPUreg_struct                                     |  |  |

|                         |                                                            |  |  |

This header file contains all function prototypes and the structure type definition used during the CPU BIST register tests. It therefore enables the C source files to call the Assembly source routines for the BIST test.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014

#### 4.2.2.2 IEC60335\_B\_CPUregTest.c

| File name               | Function prototyping                                       |

|-------------------------|------------------------------------------------------------|

| IEC60335_B_CPUregTest.c | <pre>type_testResult IEC60335_CPUregTest_BIST (void)</pre> |

This file is responsible for the full CPU BIST test routine definition.

#### Function:

type\_testResult IEC60335\_CPUregTest\_BIST

#### Purpose:

The type\_testResult IEC60335\_CPUregTest\_BIST (void) function executes the full BIST test. After this test is executed, the CPUregTestBIST\_struct contains the full pass/fail indication, testPassed. The testState will also be updated, which indicates the passing tests according to Table 3.

#### **Return value:**

IEC60335\_testPassed

IEC60335\_testFailed

#### Important file or function notifications:

- The full IEC60335\_CPUregTest\_BIST may only be executed in thread mode since the test performs checking of the SP register, which cannot be modified while the core is executing in handler mode (during an exception).

- Test pass/fail available through function return and also available in the testPassed member of the CPUregTestBIST structure.

AN11208

### 4.2.2.3 IEC60335\_B\_CPUregTestBIST\_nnn.asm

| File name                                         | Function prototyping                   |

|---------------------------------------------------|----------------------------------------|

| IEC60335_B_CPUregTestBIST_nnn <sup>[1]</sup> .asm | <pre>void _CPUregTestLOW(void);</pre>  |

|                                                   | <pre>void _CPUregTestMID(void);</pre>  |

|                                                   | <pre>void _CPUregTestHIGH(void);</pre> |

|                                                   | <pre>void _CPUregTestSP(void);</pre>   |

|                                                   | <pre>void _CPUregTestSPEC(void);</pre> |

[1] The nnn in the .asm file names must be replaced by a compiler indicator.

gnu = GNU GCC compiler

$\verb|arm = \mathsf{ARM} \ \mathsf{Realview} \ \mathsf{compiler}|$

iar = IAR EWARM compiler

This file contains all routines for testing the CPU registers during program execution and it gives the user access to the required functions used by the CPU register BIST testing.

The registers tested by the test functions are:

| Table 2. | CPU register BIST functions |

|----------|-----------------------------|

|----------|-----------------------------|

| Test function name | Register tested              |

|--------------------|------------------------------|

| _CPUregTestLOW     | R0 - R7                      |

| _CPUregTestMID     | R4 – R10                     |

| _CPUregTestHIGH    | R8 – R12                     |

| _CPUregTestSP      | R13, stackpointer (MSP, PSP) |

| _CPUregTestSPEC    | LR, APSR, PRIMASK,           |

After each individual test the test structure is updated and therefore contains the latest test values. Each test will reset the testPassed structure member and write the new pass or fail status. The testState member will also be updated after each test with the status of all passing tested registers.

#### Important file or function notifications:

- The \_CPUregTestSP can be performed only in thread mode, since it requires modification of the CONTROL register. As per ARM CPU specification, all direct writes to the CONTROL register are ignored whilst in handler mode, so this function cannot be used within a handler routine. All other functions can be executed also in handler mode (within an ISR exception).

- After test execution, the passing tests will be given a PASS bit in the CPUregTestBIST\_struct testState member according to Table 3.

- After test execution, and all containing tests pass, CPUregTestBIST\_struct testPassed will be set to IEC60335\_testPassed = 1.

| AN11208     |      |

|-------------|------|

| Application | note |

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014

### 4.2.2.4 IEC60335\_B\_CPUregTestPOST\_nnn.asm

| File name                                                                  | Function prototyping                   |

|----------------------------------------------------------------------------|----------------------------------------|

| IEC60335_B_CPUregTestPOST_nnn <sup>[1]</sup> .asm                          | <pre>void _CPUregTestPOST(void);</pre> |

| [1] The nnn in the .asm file names must be repla<br>gnu = GNU GCC compiler | aced by a compiler indicator.          |

| arm = ARM Realview compiler                                                |                                        |

iar = IAR EWARM compiler

This file contains the POST testing routing of the complete set of CPU registers. It gives the user access to the CPU register POST.

The routine is made available by means of the \_CPUregTestPOST assembly label.

#### Important file or function notifications:

- The CPUregTestPOST function must be executed prior to the branch to main. It should also execute in Privileged Thread mode.

- After test execution, and all included tests pass, the variable type\_testResult

CPUregTestPOSTStatus will be set to IEC60335\_testPassed = 1

- The variable CPUregTestPOSTStatus needs to be defined but can be located in any software module which is part of the application code, as long as its scope is made visible (so it cannot be declared as a C *static* variable). This status variable should preferably be defined in a dedicated module, which the user could place in a specific section of the device RAM memory, according to its application requirements.

- The variable CPUregTestPOSTStatus needs to be defined as being "not initialised", to prevent its value being changed by the application initialisation code before reaching *main*, so that the POST test result is preserved.

- In case of failure during test execution, the variable type\_testResult CPUregTestPOSTStatus will be set to IEC60335\_testPassed = 0

- The variable CPUregTestPOSTStatus is defined as a C language enumerative value. This implies the compiler might choose to represent the value with a single byte of data; in this case, the module including the CPUregTestPOSTStatus variable shall be compiled with the appropriate compiler specific option so that a 4 byte value is used to define enumerative values. As an alternative, the return value can be stored in an unsigned integer variable, which is also guaranteed to be 4 byte size.

- In case of failure, the CPUregTestPOST will behave in two possible ways:

- (default) The CPU will be kept in a safe state, executing an infinite loop.

- This behavior can be overridden by the user application, by re-defining the function \_CPUpostTestFailureHook in an assembly module included within the application code

- (application specific) The function CPUpostTestFailureHook is an optional assembly function, located in a module included in the user application.

This allows the system to perform different or additional recovery actions than the one described in point 1 above.

| AN11208          | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|------------------|----------------------------------------------------------------------------|---------------------------------------|

| Application note | Rev. 1.1 — 22 January 2014                                                 | 13 of 76                              |

## 4.2.2.5 CPU register test numbers

During the BIST testing the testState member of the test structure is updated with the passing tests. <u>Table 3</u> depicts the tested register and its corresponding bit value found in the testState.

#### Table 3. CPU register test table

| -           |                       | <b>B</b>              |             |

|-------------|-----------------------|-----------------------|-------------|

| Test number | Hexadecimal bit value | Register              | Bits tested |

| 0           | 0x0000 0001           | R0                    | 31:0        |

| 1           | 0x0000 0002           | R1                    | 31:0        |

| 2           | 0x0000 0004           | R2                    | 31:0        |

| 3           | 0x0000 0008           | R3                    | 31:0        |

| 4           | 0x0000 0010           | R4                    | 31:0        |

| 5           | 0x0000 0020           | R5                    | 31:0        |

| 6           | 0x0000 0040           | R6                    | 31:0        |

| 7           | 0x0000 0080           | R7                    | 31:0        |

| 8           | 0x0000 0100           | R8                    | 31:0        |

| 9           | 0x0000 0200           | R9                    | 31:0        |

| 10          | 0x0000 0400           | R10                   | 31:0        |

| 11          | 0x0000 0800           | R11                   | 31:0        |

| 12          | 0x0000 1000           | R12                   | 31:0        |

| 13          | 0x0000 2000           | R13 (default SP, MSP) | 31:2        |

| 14          | 0x0000 4000           | R13 (alternative SP)  | 31:2        |

| 15          | 0x0000 8000           | R14 (LR)              | 31:0        |

| 16          | 0x0001 0000           | APSR                  | 31:27       |

| 17          | 0x0002 0000           | PRIMASK               | 0           |

|             |                       |                       |             |

## 4.3 Program Counter (PC) Test (1.3)

## 4.3.1 Test description

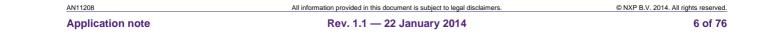

The Program Counter test checks whether the PC is able to branch throughout the whole program and data memory space. To test the branching, dummy functions are allocated throughout the whole used program and data memory space as depicted in Fig 2.

The allocation of the PC dummy test functions are placed accordingly by use of sections defined in the linker file.

The PC test routines call the dummy functions and check the returned value. Each dummy function returns a unique value. Thereby it is possible to check if the PC has jumped to the correct address.

Note that an enabled memory protection unit may trigger an exception when dummy functions are executable code areas that are protected.

| A N14 | 1200 |

|-------|------|

| ANI   | 1200 |

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 In principle, the test results always show as okay, because a defective program counter results in program crashes in any way.

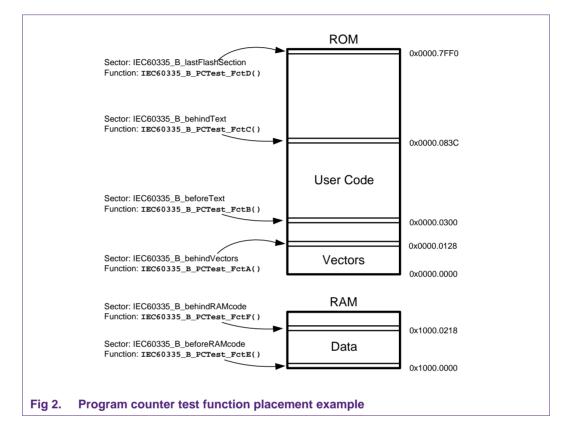

There are two different implementations available for this test: BIST and POST. The POST will check each dummy function at once. This is implemented by a loop. The BIST will only test one dummy function per call. All functions will be called after each other like a ring buffer.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 16 of 76

### 4.3.2 Test usage

This chapter describes the usage of the PC POST and BIST.

#### 4.3.2.1 IEC60335\_B\_ProgramCounterTest.h

| File name                       | Function prototyping                                     |  |

|---------------------------------|----------------------------------------------------------|--|

| IEC60335_B_ProgramCounterTest.h | <pre>type_testResult IEC60335_B_PCTest_POST(void);</pre> |  |

|                                 | <pre>type_testResult IEC60335_B_PCTest_BIST(void);</pre> |  |

This header file contains all function prototypes used during the PC tests.

#### 4.3.2.2 IEC60335\_B\_ProgramCounterTest.c

| File name                       | Definitions                                             |

|---------------------------------|---------------------------------------------------------|

| IEC60335_B_ProgramCounterTest.c | $RET_FCT_A = 1$                                         |

|                                 | $RET_FCT_B = 2$                                         |

|                                 | $RET_FCT_C = 3$                                         |

|                                 | $RET_FCT_D = 5$                                         |

|                                 | $RET_FCT_E = 7$                                         |

|                                 | RET_FCT_F = 11                                          |

|                                 | Global variable                                         |

|                                 | <b>UINT32</b> IEC60335_B_PCTest_lastFctTested           |

|                                 | Functions                                               |

|                                 | <pre>type_testResult IEC60335_B_PCTest_POST(void)</pre> |

|                                 | <pre>type_testResult IEC60335_B_PCTest_BIST(void)</pre> |

The PC test should be done pre-operation (POST) and during program execution (BIST). The PC POST and BIST functions are to be called in the corresponding state of the controller.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. **Rev. 1.1 — 22 January 2014**

#### **Function:**

type\_testResult IEC60335\_B\_PCTest\_POST(void)

#### **Purpose:**

This function should be executed prior running the main application. It will call the test functions throughout the program and data memory and check the return value against the expected value.

#### **Return value:**

IEC60335\_testPassed IEC60335 testFailed

#### **Function:**

type\_testResult IEC60335\_B\_PCTest\_BIST(void)

#### **Purpose:**

The PC BIST function IEC60335\_B\_PCTest\_BIST(void) executes at every call one PC test, saves the current executed test and returns a PASS/FAIL. It will automatically run through all six tests.

#### **Return value:**

IEC60335\_testPassed IEC60335 testFailed

AN11208

All information provided in this document is subject to legal disclaimers.

**Application note**

Rev. 1.1 — 22 January 2014

© NXP B.V. 2014. All rights reserved. 18 of 76

## 4.4 Interrupt Handling and Execution Test (2)

## 4.4.1 Test description

The test for interrupt handling and execution is application dependent. In this test, the library delivers some templates to enable the users testing the functionality in an abstract way.

The interrupts will be checked with the aid of counter variables. The different interrupts, which are observed by counter mechanisms, should have individual up-counting values instead of simply adding one.

To check the interrupts, the counter value has to be checked cyclically in a known equidistant time and compared to boundaries estimated by the user. A timer interrupt service handler should solve this.

The interrupt check routine first checks the interrupt configuration for the type of interrupt. The test usage details are described in <u>chapter 4.4.2</u>

| AN11208          | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|------------------|----------------------------------------------------------------------------|---------------------------------------|

| Application note | Rev. 1.1 — 22 January 2014                                                 | 19 of 76                              |

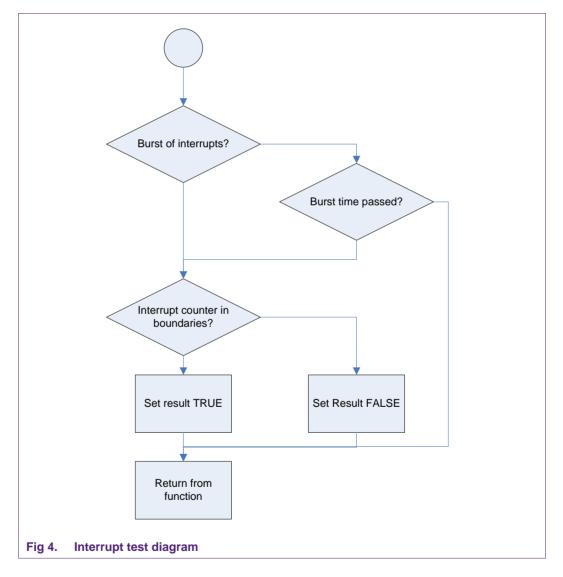

If the interrupt that needs to be checked is a burst of interrupts, the routine will check if the time to wait for all interrupts has elapsed. If the time has passed, it will check the interrupt count to be within the boundaries. If not, the check function will return directly, without setting any Result.

If the interrupt to check is not a burst of interrupts, the routine will check the interrupt counter to be within the boundary directly.

#### 4.4.2 Test usage

#### 4.4.2.1 IEC60335\_B\_Interrupts.h

| File name               | Type definition                                                                                                                        |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_Interrupts.h | type_InterruptTest                                                                                                                     |

|                         | Function prototyping                                                                                                                   |

|                         | <pre>void IEC60335_InitInterruptTest ( type_InterruptTest *pIRQ, UINT32 lowerBound, UINT32 upperBound, UINT32 individualValue );</pre> |

|                         | <pre>void IEC60335_InterruptOcurred ( type_InterruptTest *pIRQ );</pre>                                                                |

|                         | <pre>type_testResult IEC60335_InterruptCheck ( type_InterruptTest *pIRQ );</pre>                                                       |

[1] See the detailed type description in <u>Table 4</u>.

The IEC60335\_B\_Interrupts header file contains the function prototypes of the interrupt testing. A type defined structure contains all variables needed for interrupt testing.

AN11208

#### Cortex-M0 IEC60335 Class B library

| Member name                   | Description                                                      |

|-------------------------------|------------------------------------------------------------------|

| UINT32 count                  | The counter variable                                             |

| UINT32 lower                  | The estimated minimum count value of the interrupt concurrencies |

| UINT32 upper                  | The estimated maximum count value of the interrupt concurrencies |

| <b>UINT32</b> individualValue | The individual up-counting value                                 |

| BOOL CountOverflow            | Counter overflow bit                                             |

| BOOL cyclic                   |                                                                  |

| UINT32 minTime                | The time count that has to be waited, before the check is done   |

#### Table 4. Type\_InterruptTest type description

#### 4.4.2.2 IEC60335\_B\_Interrupts.c

| File name               | Function                                                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_Interrupts.c | <pre>void IEC60335_InitInterruptTest ( type_InterruptTest *pIRQ, UINT32 lowerBound, UINT32 upperBound, UINT32 individualValue )</pre> |

|                         | <pre>void IEC60335_InterruptOcurred ( type_InterruptTest *pIRQ )</pre>                                                                |

|                         | <b>type_testResult</b> IEC60335_InterruptCheck<br>(<br><b>type_InterruptTest</b> *pIRQ<br>)                                           |

This file contains the functions needed for the Interrupt testing.

AN11208

#### **Function:**

```

void IEC60335_InitInterruptTest

(

type_InterruptTest *pIRQ,

UINT32 lowerBound,

UINT32 upperBound,

UINT32 individualValue

```

)

#### Purpose:

The IEC60335\_InitInterruptTest function initialises the interrupt test structure. This function must be called prior to any interrupt initialisations.

#### Input variables:

type\_InterruptTest \*pIRQ

This structure pointer is used to set the default values to the interrupt test structure members during the interrupt test initialisation.

#### UINT32 lowerBound

The estimated minimum count value of the interrupt concurrencies.

#### UINT32 upperBound

The estimated maximum count value of the interrupt concurrencies.

#### UINT32 individualValue

The internal individual up-counting value.

#### **Return value:**

None

#### **Function:**

```

void IEC60335_InterruptOcurred

(

type_InterruptTest *pIRQ

)

```

#### **Purpose:**

This function must be called from any interrupt service handler which has to be tested.

#### Input variables:

type\_InterruptTest \*pIRQ Pointer to the interrupt test structure.

#### **Return value:**

None

#### **Function:**

type\_testResult IEC60335\_InterruptCheck

(

type\_InterruptTest \*pIRQ

)

## Purpose:

This function should be called periodically and it will do a 'quantity of interrupts' check for the interrupt under test.

#### Input variables:

type\_InterruptTest \*pIRQ Pointer to the interrupt test structure.

#### **Return value:**

IEC60335\_testPassed IEC60335\_testFailed

AN11208 Application note

## 4.5 Clock System Test (3)

# This chapter is only applicable for the NXP Cortex-M0 family members with an RTC.

## 4.5.1 Test description

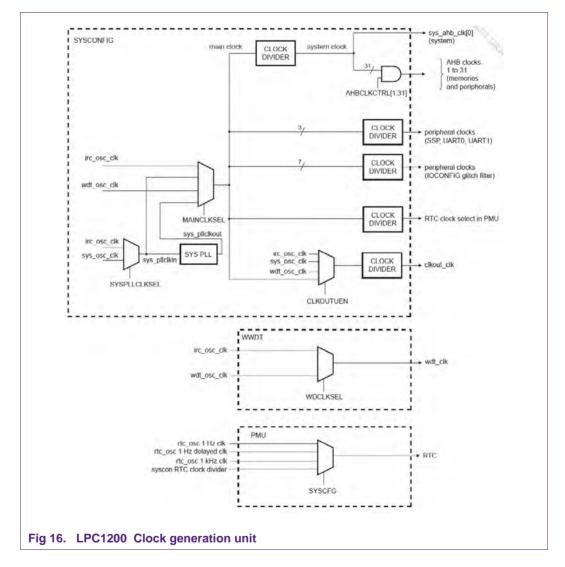

This test is intended to check the CPU clock source and frequency. This requires a second independent clock source. For a part of the NXP ARM Cortex-M0 family, the only possibility to get interrupts triggered, sourced by an independent clock, is to use the RTC peripheral.

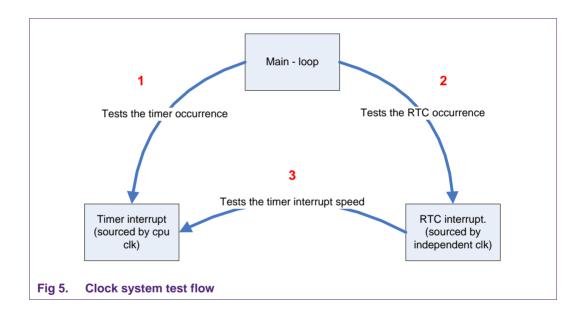

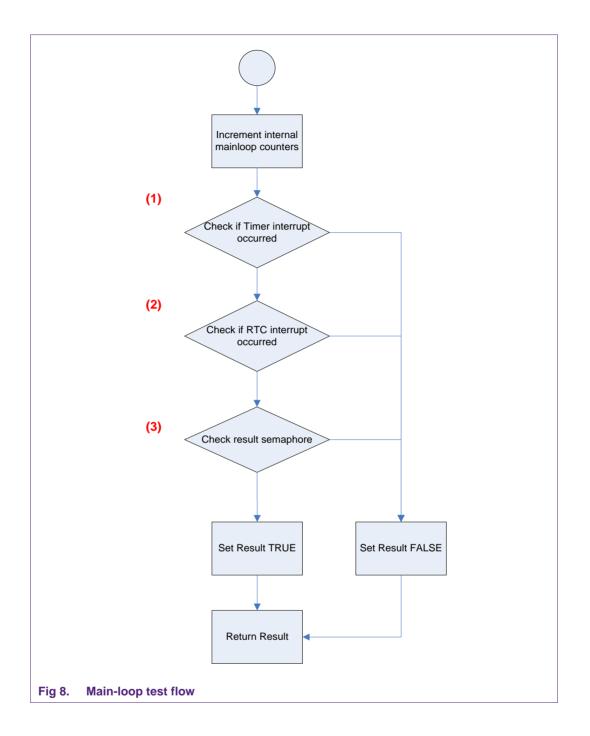

Three test functions are implemented; the first one is cyclically called from the main loop of the user application.

As depicted in the Fig 5, the main loop function checks both the timer and RTC interrupt occurrence functions. If one or both of them are missing within a rough time frame, which has to be estimated empirically, the function will return failed as result. This function also checks the result of the timer check, which is performed by the RTC function.

The second function is intended to be called from a timer interrupt service handler. This Timer needs to have the same clock source as the CPU.

The last function is intended to be called from the RTC interrupt service handler. This function is intended to check the frequency of the timer interrupts.

Application note

AN11208

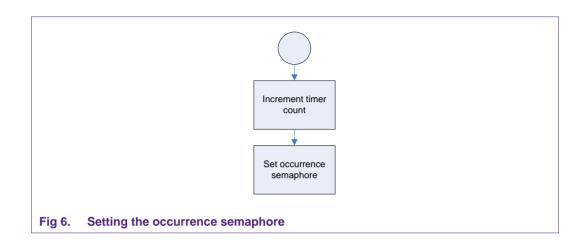

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 24 of 76 The timer simply counts how often the timer interrupt has occurred. This value is then checked by the RTC function. Additionally, it sets the occurrence semaphore, which is used for occurrence recognition inside of the main function. See <u>Fig 6</u>.

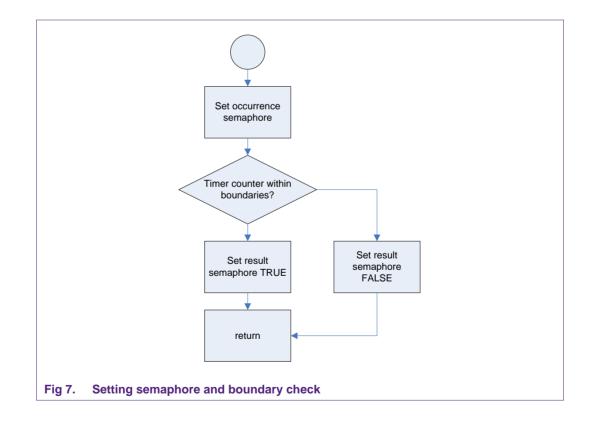

The RTC function also sets an occurrence semaphore, to be tested from the main function. Then it checks the timer counter variable to be within the estimated boundaries. The result of this check is stored into a result semaphore.

| 1208           | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|----------------|----------------------------------------------------------------------------|---------------------------------------|

| plication note | Rev. 1.1 — 22 January 2014                                                 | 25 of 76                              |

| plication note | Rev. 1.1 — 22 January 2014                                                 | :                                     |

## Cortex-M0 IEC60335 Class B library

AN11208

This Manual:http://www.manuallib.com/nxp/an11208-cortex-m0-application-note.html

## 4.5.2 Test usage

#### 4.5.2.1 IEC60335\_B\_ClockTest.h

| File name              | Function prototyping                                                                                                                        |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_ClockTest.h | <pre>void IEC60335_initClockTest ( UINT32 timerOccThreshold, UINT32 rtcOccThreshold, UINT32 timerLowerBound, UINT32 timerUpperBound )</pre> |

|                        | <pre>type_testResult IEC60335_Clocktest_MainLoopHandler(void)</pre>                                                                         |

|                        | <pre>void IEC60335_Clocktest_TimerIntHandler(void)</pre>                                                                                    |

|                        | <pre>void IEC60335_Clocktest_RTCHandler(void)</pre>                                                                                         |

The IEC60335\_B\_ClockTest.h file contains all prototypes needed for the ClockTest.

#### 4.5.2.2 IEC60335\_B\_ClockTest.c

| File name              | Type definition                                                                                                                             |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_ClockTest.c | type_ClockTest <sup>[1]</sup>                                                                                                               |

|                        | Functions                                                                                                                                   |

|                        | <pre>void IEC60335_resetClockTest(void)</pre>                                                                                               |

|                        | <pre>void IEC60335_initClockTest ( UINT32 timerOccThreshold, UINT32 rtcOccThreshold, UINT32 timerLowerBound, UINT32 timerUpperBound )</pre> |

|                        | <pre>type_testResult IEC60335_Clocktest_MainLoopHandler(void)</pre>                                                                         |

|                        | <pre>void IEC60335_Clocktest_TimerIntHandler(void)</pre>                                                                                    |

|                        | <pre>type_testResult IEC60335_Clocktest_MainLoopHandler(void)</pre>                                                                         |

|                        | <pre>void IEC60335_Clocktest_RTCHandler(void)</pre>                                                                                         |

[1] Structure members described in <u>Table 5</u>

AN11208

Application note

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 27 of 76

#### Cortex-M0 IEC60335 Class B library

#### Table 5.type\_ClockTest structure

| Member name                    | Description                                                                                               |

|--------------------------------|-----------------------------------------------------------------------------------------------------------|

| UINT32 timerTestThreshold      | Used in the mainloop function, defines the number of calls to start occurrence test                       |

| <b>UINT32</b> rtcTestThreshold | Used in the mainloop function, defines the number of calls to start occurrence test                       |

| UINT32 rtcOccCounter           | Counter variable for the mainloop, if value reached the defined threshold, the occurrence test is started |

| UINT32 timerOccCounter         | Counter variable for the mainloop, if value reached the defined threshold, the occurrence test is started |

| BOOL timerOccured              | This bool will be set in the timer function, and is reset during occurrence test                          |

| BOOL rtcOccured                | This bool will be set in the rtc function, and is reset during occurrence test                            |

| UINT32 timerCounter            | The counter Variable, to test the timer to be within its boundaries                                       |

| UINT32 timerBoundLower         | The estimated minimum count of cycle occurrences (Threshold for timer test).                              |

| UINT32 timerBoundUpper         | The estimated maximum count of cycle occurrences (Threshold for timer test).                              |

| BOOL timerOutOfBounds          | Within this bool, the rtc timer test signals the error state to the main function                         |

| BOOL timerCounterOverflow      | Reflects, if the TimerCounter overflows due to an error                                                   |

## **Function:**

void IEC60335\_resetClockTest(void)

### Purpose:

The IEC60335\_resetClockTest function clears and resets all used Clock Test variables

#### **Return value:**

None

AN11208 Application note All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 28 of 76

#### Cortex-M0 IEC60335 Class B library

#### **Function:**

```

void IEC60335_initClockTest

(

UINT32 timerOccThreshold,

UINT32 rtcOccThreshold,

UINT32 timerLowerBound,

UINT32 timerUpperBound

)

```

#### **Purpose:**

This function initiates the various variables used during the Clock Test.

#### Input variables:

UINT32 timerOccThreshold

The timerOccThreshold variable initiates the threshold value that defines the number of calls that started the timer occurrence test.

#### UINT32 rtcOccThreshold

The rtcOccThreshold variable initiates the threshold value that defines the number of calls that started the RTC occurrence test.

#### UINT32 timerLowerBound

This variable sets the lower bound value of the number of timer or RTC test occurrences.

#### UINT32 timerUpperBound

This variable sets the upper bound value of the number of timer or RTC test occurrences.

#### **Return value:**

None

AN11208 Application note

#### **Function:**

type\_testResult IEC60335\_Clocktest\_MainLoopHandler(void)

#### **Purpose:**

This function represents the part of the IEC60335 Class B clock test that must be executed within the main loop.

This function tests the following criteria:

- The clock test timer interrupts were triggered

- The clock test RTC interrupt was triggered

- In any of the two interrupts an error was detected.

#### Return value:

IEC60335\_testPassed IEC60335\_testFailed

#### Important function notifications:

- This function must be called once inside the main loop.

- For this function, it is necessary to estimate the count of how often this function could be called. This is important to find valid threshold values, which are used to test timer and RTC interrupt occurrence.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014

#### **Function:**

void IEC60335\_Clocktest\_TimerIntHandler(void)

#### **Purpose:**

This function is intended to use as timer interrupt service handler or to be called once inside the timer interrupt service handler.

#### **Return value:**

None

#### Function:

```

void IEC60335_Clocktest_RTCHandler(void)

```

#### Purpose:

This function should be called inside the custom RTC interrupt service handler. It can't be used as service handler by itself, because of the return value that has to be evaluated after the call.

This function tests the timer-time-frame, in this case the CPU frequency.

Also, this function checks if the main loop function was called.

#### **Return value:**

None

AN11208

## 4.6 Invariable memory Test (4.1)

## 4.6.1 Test description:

The invariable memory must be checked for single bit faults. During POST testing the complete Flash memory where the user application is located gets tested.

During BIST testing it is advisable to test the Flash memory in smaller segments to prevent the CPU from being blocked.

#### 4.6.1.1 Multiple Input Signature Register

The NXP Cortex-M0 based devices within the LPC11x family have an integrated flash module that incorporates a 128-bit signature generator, called the Multiple Input Signature Register (MISR).

This MISR can be used for generating a signature of the used safety critical memory region.

Since this module is integrated in the flash module, it generates a signature faster than when implemented in software, decreasing the time required for the test.

A signature can be generated for any part of the Flash contents. The address range to be used for the signature generation is defined by writing the start address to the FMSSTART register and the stop address to the FMSSTOP register.

The flash address should first be aligned with a flash word (128 bits) in the array; this is done by right - shifting the start and stop address by 4.

```

/* align flash address to refer the flash word in the array */

startAddr = (startAddr >> 4) & 0x0001ffff;

length = ((startAddr + length) >> 4) & 0x0001ffff;

/* write start address of the flash contents to the register*/

LPC_FMC->FMSSTART = startAddr;

/* write stop address of the flash contents to the register, start generating

the signature*/

LPC_FMC->FMSSTOP = length | MISR_START;

```

The signature generation is started by writing '1' to the MISR\_START bit (17) in the FMSSTOP register.

Since the MISR is implemented in hardware, it is much faster than doing the same MISR check in software. The time that the signature generation takes is proportional to the address range for which the signature is generated.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 32 of 76

#### 4.6.1.2 Signature generation time

A safe estimation for the duration of the signature generation is:

$$T_{MISR} = \operatorname{int}\left(\frac{60ns}{T_{cclk}} + 3\right) \times \left(FMSSTOP - FMSSTART + 1\right)$$

(1)

with Tcclk the core clock. See the device user manual for more information on the clock system.

After completion of the hardware MISR the 128 bits signature can be read from the FMSW0...FMSW3 registers.

#### 4.6.1.3 Signature verification

The signatures generated by the hardware MISR must be verified and equal to the reference signatures. The algorithm for deriving the reference signatures is illustrated in the pseudo code below.

```

Sign word0 = 0

Sign word1 = 0

Sign_word2 = 0

Sign_word3 = 0

FOR address = FMSTART TO FMSTOP

nextSign_word0 = flashWord_word0 XOR (Sign_word0>>1) XOR (Sign_word1<<31)</pre>

nextSign_word1 = flashWord_word1 XOR (Sign_word1>>1) XOR (Sign_word2<<31)</pre>

nextSign_word2 = flashWord_word2 XOR (Sign_word2>>1) XOR (Sign_word3<<31)</pre>

nextSign_word3 = flashWord_word3 XOR (Sign_word3>>1)

XOR (Sign_word0 AND 1<<29) << 2

XOR (Sign_word0 AND 1<<27) << 4

XOR (Sign_word0 AND 1<<2) << 29

XOR (Sign_word0 AND 1<<0) << 31

Sign_word0 = nextSign0

Sign_word1 = nextSign1

Sign_word2 = nextSign2

Sign_word3 = nextSign3

}

```

#### Important notification:

The hardware MISR signature generator is *blocking* for the Flash, this means no flash read or write access is possible during signature generation. The MISR Code should run from SRAM. It is therefore advisable to make sure while using the hardware MISR the flash will not be accessed.

#### 4.6.1.4 CRC generator

The NXP Cortex-M0 based devices within the LPC12x family have a Cyclic Redundancy Check (CRC) module integrated. The CRC generator with programmable polynomial settings supports several CRC standards commonly used.

The following features are supported:

- Three common polynomials: CRC-CCITT, CRC-16, and CRC-32.

- CRC-CCITT: x16 + x12 + x5 + 1

- CRC-16: x16 + x15 + x2 + 1

| AN11208          | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|------------------|----------------------------------------------------------------------------|---------------------------------------|

| Application note | Rev. 1.1 — 22 January 2014                                                 | 33 of 76                              |

- CRC-32: x32 + x26 + x23 + x22 + x16 + x12 + x11 + x10 + x8 + x7 + x5 + x4 + x2 + x + 1

- Bit order reverse and 1's complement programmable setting for input data and CRC sum

- Programmable seed number setting.

- Accept any size of data width per write: 8, 16 or 32-bit.

The CRC module can be used for generating a signature of the used safety critical memory region.

Since this module is integrated in the device, it generates a signature faster than when implemented in software, decreasing the time required for the test. A signature can be generated for any part of the Flash contents.

The device can be programmed for supporting a specific standard by using the following setups:

CRC-CCITT set-up

Polynomial =  $x_{16} + x_{12} + x_5 + 1$ Seed Value = 0xFFFFBit order reverse for data input: NO 1's complement for data input: NO Bit order reverse for CRC sum: NO 1's complement for CRC sum: NO CRC\_MODE = 0x0000 0000CRC\_SEED = 0x0000 FFFF

CRC-16 set-up

Polynomial =  $x_{16} + x_{15} + x_2 + 1$ Seed Value = 0x0000Bit order reverse for data input: YES 1's complement for data input: NO Bit order reverse for CRC sum: YES 1's complement for CRC sum: NO CRC\_MODE =  $0x0000\ 0015$ CRC\_SEED =  $0x0000\ 0000$

CRC-32 set-up

Polynomial = x32+ x26 + x23 + x22 + x16 + x12 + x11 + x10 + x8 + x7 + x5 + x4 + x2 + x + 1 Seed Value = 0xFFFF FFFF Bit order reverse for data input: YES 1's complement for data input: NO Bit order reverse for CRC sum: YES 1's complement for CRC sum: YES CRC\_MODE = 0x0000 0036 CRC\_SEED = 0xFFFF FFFF

After configuring the CRC engine by programming the parameters above in the MODE and SEED registers, the data over which the signature needs to be calculated can be fed sequentially to its WR\_DATA input register. The resulting CRC signature can be read out from the read only SUM register

#### 4.6.1.5 Critical content

If there is a stored critical constant periodically used in critical calculations, then it is necessary to check this variable before every usage.

| AN11208          | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|------------------|----------------------------------------------------------------------------|---------------------------------------|

| Application note | Rev. 1.1 — 22 January 2014                                                 | 34 of 76                              |

Refer to <u>chapter 4.8</u> Secure Data storage.

#### 4.6.1.6 Usage notes

There are the following possible definitions for the flash signature options:

LPC111x: MISR\_FLASH\_CRC LPC12x: CCITT\_FLASH\_CRC, CRC16\_FLASH\_CRC, CRC32\_FLASH\_CRC

All of them are referenced within the LPC1xxx\_TargetConfig.c file.

The values of the signatures depend on the compiler and linker version number, and may need to be updated from the default values provided within the example application. The computed values will also be different whenever any modifications are made inside the application code.

To determine the signature, either:

• Run the test application once, to find out the actual signature, then substitute the actual value into the appropriate #define directive.

For convenience, place a breakpoint at the routine check loop labels (\_misr\_hw\_sigcheck, \_crc16\_verify, \_crc32\_verify) within the file IEC60335\_B\_FlashTestxxx.s, then copy the computed values back in the signature definition;

- Calculate the signature automatically, and patch it in the desired location, by using the build tools (if supported) or;

- Use a custom script to patch the image before it gets burned in flash.

AN11208

# 4.6.2 Test usage

This chapter explains how the invariable testing is implemented and can be used.

4.6.2.1 IEC60335\_B\_FlashTest.h

| File name              | Function prototyping                                                                                                           |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_FlashTest.h | <pre>void StartHardSignatureGen ( UINT32 startAddr, UINT32 length, FlashSign_t *ResultSign );</pre>                            |

|                        | <pre>void StartSoftSignatureGen ( UINT32 startAddr, UINT32 length, FlashSign_t *ResultSign );</pre>                            |

|                        | <pre>type_testResult IEC60335_FLASHtest_BIST ( UINT32 startAddr, UINT32 length, FlashSign_t *TestSign, UINT8 selectHS );</pre> |

|                        | <pre>type_testResult IEC60335_testSignatures ( FlashSign_t *sign1, FlashSign_t *sign2 );</pre>                                 |

|                        | Type definition                                                                                                                |

|                        | <pre>FlashSign_t Crc32Sig_t; Crc16Sig_t; CcittSig_t;</pre>                                                                     |

|                        | Definitions                                                                                                                    |

|                        | FLASH_HARD_SIGN = 1                                                                                                            |

|                        | FLASH_SOFT_SIGN = 2<br>MISR_START = (1<<17)                                                                                    |

|                        | $MISR_SIARI = (1<17)$<br>EOM = (0x01<<2)                                                                                       |

### **Functions:**

All functions are described in detail in chapter 4.6.2.2

### **Type definitions:**

A type FlashSign\_t is defined; this type contains four UINT32 variables named word0...word3. These four words represent the 128 bits used for the hardware and software 128-bit signature generation.

The types Crc32Sig\_t, Crc16Sig\_t, CcittSig\_t define the type of signature used with the LPC12x devices for the various algorithms supported by the CRC engine. Crc32Sig is a UINT32 type, whereas Crc16Sig\_t and CcittSig\_t are UINT16 variables.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 36 of 76

### **Definitions:**

The various flash sizes (32, 64, 128, 256 or 512 kB) available on the NXP Cortex-M0 family are defined within the file IEC60335\_B\_Config.h (described in 4.8.3), as a convenience to the user for determining the ranges of flash which can be tested within the application.

The actual flash size for the chosen device can be specified in the definition of symbol FLASH\_SIZE within the target specific configuration header file included by IEC60335\_B\_Config.h file.

There are two defines which differentiate between the hardware or software generation, used by the IEC60335\_FLASHtest\_BIST function.

FLASH\_HARD\_SIGN indicates the usage of the hardware signature generator, and FLASH\_SOFT\_SIGN the software signature generator, on the LPC11x (using the MISR).

MISR\_START is the hardware MISR start bit in the FMC FMSSTOP register.

EOM is the END OF MISR status in the FMC STATUS register.

AN11208

**Application note**

All information provided in this document is subject to legal disclaimers. **Rev. 1.1 — 22 January 2014**  © NXP B.V. 2014. All rights reserved. 37 of 76

# Cortex-M0 IEC60335 Class B library

### 4.6.2.2 IEC60335\_B\_FlashTest.c

| File name              | Function prototyping                                                                                                               |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| IEC60335_B_FlashTest.c | <pre>void StartHardSignatureGen ( UINT32 startAddr, UINT32 length, FlashSign_t *ResultSign );</pre>                                |

|                        | <pre>void StartSoftSignatureGen ( UINT32 startAddr, UINT32 length, FlashSign_t *ResultSign );</pre>                                |

|                        | <pre>type_testResult IEC60335_FLASHtestMISR_BIST ( UINT32 startAddr, UINT32 length, FlashSign_t *TestSign, UINT8 selectHS );</pre> |

|                        | <pre>type_testResult IEC60335_testMISRSignatures ( FlashSign_t *sign1, FlashSign_t *sign2 );</pre>                                 |

|                        | Structure definitions                                                                                                              |

|                        | FlashSign_t IEC60335_Flash_Sign_BIST                                                                                               |

AN11208

All information provided in this document is subject to legal disclaimers.

**Application note**

### Cortex-M0 IEC60335 Class B library

### Function:

void StartHardSignatureGen

(

UINT32 startAddr,

UINT32 length,

FlashSign\_t \*ResultSign

);

### **Purpose:**

This function starts the execution of the hardware signature generation. It will do the signature generation from the start address (startAddr) with a length (length). After completion the signature will be copied to the location the pResultSign pointer points to.

### Input variables:

UINT32 startAddr

This variable is the starting address of where the signature generation will start.

### UINT32 length

The length variable is the region size to be used for the signature generation.

### FlashSign\_t \*pResultSign

The result after generation completion will be put in the pointed location by the pResultSign pointer.

### **Return value:**

None

### Important notification:

This function is BLOCKING. It blocks all access to the flash memory. It is advisable to make sure no flash memory needs to be accessed during the execution of this function. The time required for this function is explained in the test description chapter.

|  | AN1 | 1208 |

|--|-----|------|

|--|-----|------|

**Application note**

All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 39 of 76

```

void StartSoftSignatureGen

(

UINT32 startAddr,

UINT32 length,

FlashSign_t *ResultSign

);

```

### Purpose:

This function starts the execution of the software signature generation. It will do the signature generation from the start address (startAddr) with a length (length).

The algorithm explained in the test description chapter is used for generation of the software signature.

This function can be used for the reference signature with which the hardware generated signature must be equal to.

After completion the signature will be copied to the location the  ${\tt pResultSign}$  pointer points to.

### Input variables:

**UINT32** startAddr

This variable is the starting address of where the signature generation will start.

### UINT32 length

The length variable is the region size used for the signature generation.

### FlashSign\_t \*pResultSign

The result after generation completion will be put in the pointed location by the pResultSign pointer.

### **Return value:**

None

AN11208 Application note

```

type_testResult IEC60335_FLASHtestMISR_BIST

(

UINT32 startAddr,

UINT32 length,

FlashSign_t *TestSign,

UINT8 selectHS

);

```

### Purpose:

This is the general IEC60335 Flash test function for BIST on the LPC11x. It must periodically be executed for testing the safety critical region. The start address and region length is passed as well as the reference signature to which the newly generated signature must match.

The user can select whether the hardware or software generator will be used during Flash BIST.

The comparison of the reference signature and the generated signature is integrated in this function and therefore it will return a pass or fail for this test.

### Input variables:

**UINT32** startAddr

This variable is the starting address of where the signature generation will start.

UINT32 length

The length variable is the region size used for the signature generation.

FlashSign\_t \*TestSign

Pointer to the reference signature.

UINT8 selectHS

Hardware or software signature generation selection byte, FLASH\_HARD\_SIGN or FLASH\_SOFT\_SIGN should be used.

### **Return value:**

IEC60335\_testPassed IEC60335\_testFailed

AN11208 Application note All information provided in this document is subject to legal disclaimers. Rev. 1.1 — 22 January 2014 © NXP B.V. 2014. All rights reserved. 41 of 76

```

type_testResult IEC60335_testMISRSignatures

(

FlashSign_t *sign1,

FlashSign_t *sign2

);

```

### **Purpose:**

This function compares two signatures generated using the MISR algorithm on the LPC11x and returns a pass or fail if equal or not.

### Input variables:

FlashSign\_t \*sign1 Pointer to the first signature to be tested.

FlashSign\_t \*sign2 Pointer to the second signature to be tested.

### **Return value:**

IEC60335\_testPassed IEC60335\_testFailed

AN11208

All information provided in this document is subject to legal disclaimers.

**Application note**

© NXP B.V. 2014. All rights reserved. 42 of 76

| File name                                       | Function prototyping     |

|-------------------------------------------------|--------------------------|

| IEC60335_B_FLASHTestPOST_nnn.asm <sup>[1]</sup> | _FLASHTestPOST           |

|                                                 | Included Definitions     |

|                                                 | SELECTED_CRC_TYPE        |

|                                                 | IEC60335_BOTTOM_ROM_POST |

|                                                 | IEC60335_TOP_ROM_POST    |

|                                                 | CRC_MODE_ADDR            |

|                                                 | CRC_SEED_ADDR            |

|                                                 | CRC_SUM_ADDR             |

|                                                 | CRC_WR_DATA_ADDR         |

|                                                 | FMSSTART_ADDR            |

|                                                 | FMSSTOP_ADDR             |

|                                                 | FMSW0_ADDR               |

|                                                 | FMSW1_ADDR               |

|                                                 | FMSW2_ADDR               |

|                                                 | FMSW3_ADDR               |

|                                                 | FMSTAT_ADDR              |

|                                                 | FMSTATCLR_ADDR           |

|                                                 | CRC_SIGNATURE_ADDR       |

|                                                 | MISR_SIGNATURE_ADDR      |

### 4.6.2.3 IEC60335\_B\_FLASHTestPOST\_nnn.asm

[1] The nnn in the .asm file names must be replaced by a compiler indicator.

gnu = GNU GCC compiler

arm = ARM Realview compiler

iar = IAR EWARM compiler

This file contains the POST testing routing of the used non volatile (flash) memory image used by the application. It gives the user access to the Flash POST.

The routine is made available by means of the \_FLASHTestPOST assembly label.

To configure the POST test, the user needs to define which type of signature test needs to be performed at startup. The options are:

- CRC16\_ALGO, CRC32\_ALGO, CCITT\_ALGO (usable on the LPC12x targets)

- MISRHW\_ALGO (usable on the LPC11x targets)

The particular algorithm choice is defined by the symbol SELECTED\_CRC\_TYPE and is specified in a target specific configuration header file (example:

LPC1227\_TargetConfig.h), which the user needs to include within the global library IEC60335\_B\_Config.h file (explained in more detail in <u>section 4.8.3</u>).

The actual range of memory being tested is determined by the symbols included from the target specific configuration header file. These symbols are called IEC60335\_BOTTOM\_ROM\_POST and IEC60335\_TOP\_ROM\_POST.

Note: these might be automatically determined by means of the symbols exported by the tool chain used for generating (compiling, assembling, linking) the application code, as shown in the example applications provided with the library.

| AN11208          | All information provided in this document is subject to legal disclaimers. | © NXP B.V. 2014. All rights reserved. |

|------------------|----------------------------------------------------------------------------|---------------------------------------|

| Application note | Rev. 1.1 — 22 January 2014                                                 | 43 of 76                              |

The memory address where the reference signature is stored is specified by the macros called CRC\_SIGNATURE\_ADDR (used for a CRC type signature) or MISR\_SIGNATURE\_ADDR (used for a MISR type signature).

These also both need to be specified within the target specific configuration header file.

Note: these symbols might be automatically determined by means of the symbols determined and exported by the tool chain used for generating (compiling, assembling, linking) the application code, as shown in the example applications provided by the library. In the examples, the signature is located on the next 128 bit boundary just after the end of the application image. This will leave the rest of the Flash memory available for application specific use (which might be verified with BIST tests at runtime).

The POST test will compute the signature on the actual Flash contents, and compare it with the reference signature located at address CRC\_SIGNATURE\_ADDR / MISR\_SIGNATURE\_ADDR.

CRC\_MODE\_ADDR, CRC\_SEED\_ADDR, CRC\_SUM\_ADDR, CRC\_WR\_DATA\_ADDR are macros which include in the IEC60335\_B\_FLASHTestPOST\_nnn.asm assembly module the register addresses specific to the CRC engine available in the LPC12xx family of devices.

Note: the actual values (register addresses) of these macros are predefined within the IEC60335\_B\_Config.h file, and apply to the current LPC12xx family of devices. The user has the option to override those values if needed. This ensures compatibility of the library for future devices in which the actual address assignment might be different than the ones available at the time the library is released.

FMSSTART\_ADDR, FMSSTOP\_ADDR, FMSW0\_ADDR, FMSW1\_ADDR, FMSW2\_ADDR, FMSW3\_ADDR, FMSTAT\_ADDR, FMSTATCLR\_ADDR are macros which include in the assembly module IEC60335\_B\_FLASHTestPOST\_nnn.asm the register addresses which are specific to the MISR engine available in the LPC11xx family of devices.

Note: the actual values (register addresses) of these macros are predefined within the IEC60335\_B\_Config.h file, and apply to the current LPC11xx family of devices. The user has the option to override those values if needed. This ensures compatibility of the library for future devices in which the actual address assignment might be different than the ones available at the time the library is released.

Note that while performing the MISR algorithm computation, a part of the test will be BLOCKING. It blocks all access to the flash memory until the MISR engine has completed the generation of the signature.

### Important file or function notifications:

- The FLASHTEStPOST function must be executed prior to the branch to main. It should also execute in Privileged Thread mode.

- After test execution, and all included tests pass, the variable type\_testResult FlashPostTestStatus will be set to IEC60335\_testPassed = 1

- The variable FlashPostTestStatus must be defined by the user but can be located in any software module which is part of the application code, as long as its scope is made visible (so it cannot be declared as a C *static* variable). This status variable should preferably be defined in a dedicated module, which the user could

| AN11208          | All information provided in this document is subject to legal disclaimers. |  |

|------------------|----------------------------------------------------------------------------|--|

| Application note | Rev. 1.1 — 22 January 2014                                                 |  |

© NXP B.V. 2014. All rights reserved.

place in a specific section of the device RAM memory, according to its application requirements.

- The variable FlashPostTestStatus should be defined as being "not initialised", to prevent its value being changed by the application initialisation code before reaching *main*, so that the POST test result is preserved. This is tool chain specific and left to the user.

- In case of failure during test execution, the variable type\_testResult

FlashPostTestStatus will be set to IEC60335\_testPassed = 0

- In case of failure, the function will behave in the following way:

- (default) The CPU will be kept in a safe state, executing an infinite loop.

This behavior can be overridden by the user application, by re-defining the function \_flashPostTestFailureHook in an assembly module included within the application code.

- (application specific) The function flashPostTestFailureHook is an optional assembly function, located in a module included in the user application.

This allows the system to perform different or additional recovery actions than the one described in point 1 above.

An MISR type of signature should be located in memory at an address which is aligned to (a multiple of) 16 bytes (128 bits) because of the MISR hardware requirements.

AN11208

**Application note**

© NXP B.V. 2014. All rights reserved. 45 of 76

# 4.7 Variable Memory (4.2)

# 4.7.1 Test description