## Bluetooth™ V2.1 + EDR ("Lisbon") for automotive applications

### **Features**

- Based on Ericsson technology licensing baseband core (EBC)

- Bluetooth<sup>™</sup> specification compliance: V2.1 + EDR ("Lisbon")

- Point-to-point, point-to-multipoint (up to 7 slaves) and scatternet capability

- Support ACL and SCO links

- Extended SCO (eSCO) links

- Faster connection

- HW support for packet types

- ACL: DM1, DM3, DM5, DH1, DH3, DH5, 2-DH1, 2-DH3, 2-DH5, 3-DH1, 3-DH3, 3-DH5

- SCO: HV1, HV3 and DV

- eSCO: EV3, EV4, EV5, 2-EV3, 2-EV5, 3-EV3, 3-EV5

- Adaptive frequency hopping (AFH)

- Channel quality driven data rate (CQDDR)

- "Lisbon" features

- Encryption pause/resume (EPR)

- Extended inquiry response (EIR)

- Link supervision time out (LSTO)

- Secure simple pairing

- Sniff subrating

- Quality of service (QoS)

Packet boundary flag

Erroneous data delivery

- Transmit power

- Power class 2 and power class 1.5 (above 4 dBm)

- Programmable output power

- Power class 1 compatible

- HCI

- HCI H4 and enhanced H4 transport layer

- HCI proprietary commands (e.g. peripherals control)

- Single HCI command for patch/upgrade download

- eSCO over HCI supported

- Supports pitch-period error concealment (PPEC)

- Efficient and flexible support for WLAN coexistence scenarios

LFBGA48 (6x6x1.4mm; 0.8mm Pitch)

- Low power consumption

- Ultra low power architecture with 3 different low-power levels

- Deep sleep modes, including host-power saving feature

- Dual wake-up mechanism: initiated by the host or by the Bluetooth device

- Communication interfaces

- Fast UART up to 4 MHz

- Flexible SPI interface up to 13 MHz

- PCM interface

- Up to 10 additional flexibly programmable GPIOs

- External interrupts possible through the GPIOs

- Fast I<sup>2</sup>C interface as master

- Clock support

- System clock input (digital or sine wave) at 9.6, 10, 13, 16, 16.8, 19.2, 26, 33.6 or 38.4 MHz

- Low power clock input at 3.2 kHz, 32 kHz and 32.768 kHz

- ARM7TDMI CPU

- Memory organization

- On chip RAM, including provision for patches

- On chip ROM, preloaded with SW up to HCI

- Ciphering support up to 128-bit key

- Single power supply with internal regulators for core voltage generation

- Supports 1.65 V to 2.85 V I/O systems

- Auto calibration (VCO, filters)

Contents STA2500D

## **Contents**

| 1 | Desc | cription                                          | 6          |

|---|------|---------------------------------------------------|------------|

| 2 | Quio | k reference data                                  | 7          |

|   | 2.1  | Absolute maximum ratings                          | 7          |

|   | 2.2  | Operating ranges                                  | 7          |

|   | 2.3  | I/O specifications                                | 8          |

|   | 2.4  | Clock specifications                              | 8          |

|   | 2.5  | Current consumption                               | 0          |

| 3 | Bloc | k diagram and electrical schematic                | 2          |

| 4 | Pino | out                                               | 3          |

|   | 4.1  | Pin description and assignment                    | 3          |

|   | 4.2  | HW configuration of the STA2500D                  | 6          |

|   | 4.3  | I/O Supply 1                                      | 7          |

| 5 | Fund | ctional description1                              | 8          |

|   | 5.1  | Transmitter 1                                     | 8          |

|   | 5.2  | Receiver                                          | 8          |

|   | 5.3  | PLL                                               | 8          |

|   | 5.4  | Bluetooth controller V1.2 and V2.0 + EDR features | 9          |

|   | 5.5  | Bluetooth controller V2.1 + EDR ("Lisbon")        | 9          |

|   | 5.6  | Processor and memory 1                            | 9          |

|   | 5.7  | TX output power control                           | 20         |

| 6 | Gen  | eral specification 2                              | ː <b>1</b> |

|   | 6.1  | Receiver 2                                        | <u>?</u> 1 |

|   | 6.2  | Transmitter 2                                     | :4         |

|   | 6.3  | Class 1 operation                                 | 26         |

|   | 6.4  | Power-up 2                                        | :6         |

|   | 6.5  | System clock                                      | 27         |

|   | 6.6  | Low power clock                                   | :7         |

|   | 6.7  | Clock detection                                   | 27         |

|   |      |                                                   |            |

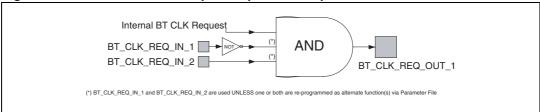

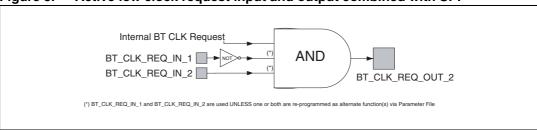

|              | 6.8   | Clock r              | equest signals                                         | 27   |

|--------------|-------|----------------------|--------------------------------------------------------|------|

|              | 6.9   | Interru              | ots                                                    | 29   |

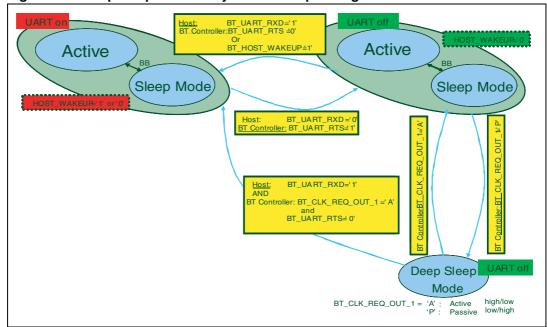

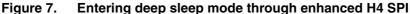

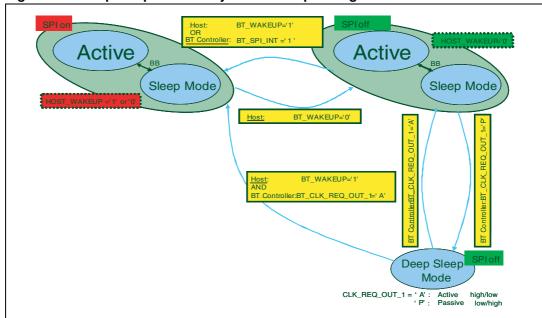

|              | 6.10  | Low po               | wer modes                                              | 29   |

|              |       | 6.10.1               | Overview                                               | 29   |

|              |       | 6.10.2               | Some examples for the usage of the low power modes     | 30   |

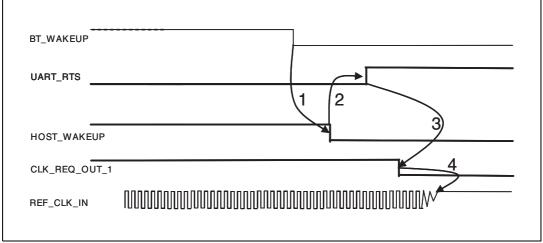

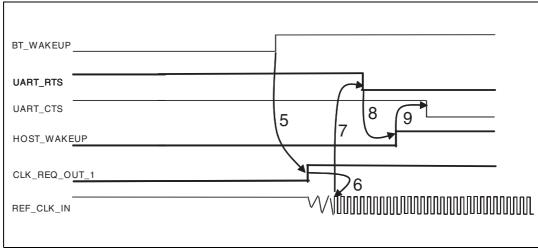

|              |       | 6.10.3               | Deep sleep mode entry and wake-up                      | 30   |

|              | 6.11  | Patch F              | RAM                                                    | 37   |

|              | 6.12  | Downlo               | oad of SW parameter file                               | 37   |

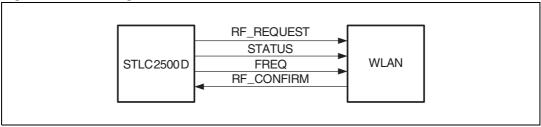

|              | 6.13  | Bluetoo              | oth - WLAN coexistence in collocated scenario          | 38   |

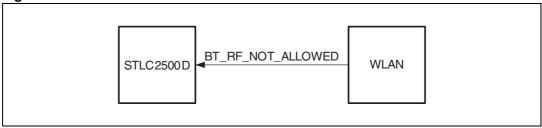

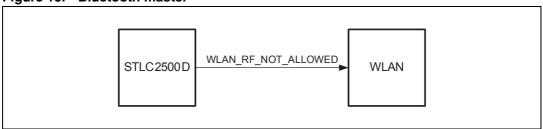

|              |       | 6.13.1               | Algorithm 1: PTA (packet traffic arbitration)          |      |

|              |       | 6.13.2               | Algorithm 2: WLAN master                               | 39   |

|              |       | 6.13.3               | Algorithm 3: Bluetooth master                          |      |

|              |       | 6.13.4               | Algorithm 4: two-wire mechanism                        |      |

|              |       | 6.13.5               | Algorithm 5: Alternating wireless medium access (AWMA) | 40   |

| 7            | Digit | al interf            | aces                                                   | 41   |

|              | 7.1   | The UA               | ART interface                                          | 41   |

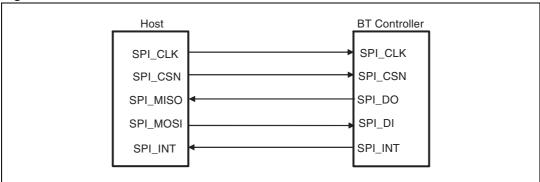

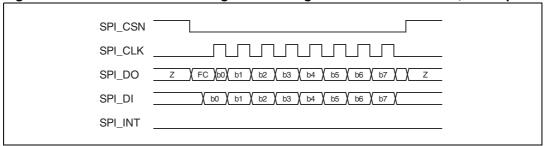

|              | 7.2   | The SF               | PI interface                                           | 41   |

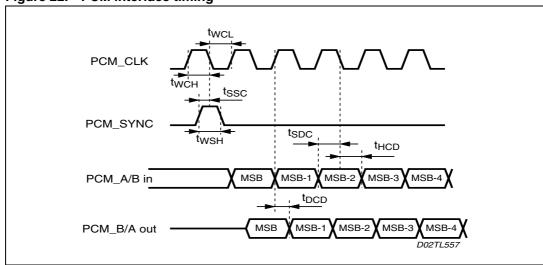

|              | 7.3   | The PC               | CM interface                                           | 43   |

|              | 7.4   | The JT               | AG interface                                           | 46   |

|              | 7.5   | Alterna              | ite I/O functions                                      | 46   |

|              | 7.6   | The I <sup>2</sup> C | C interface                                            | 47   |

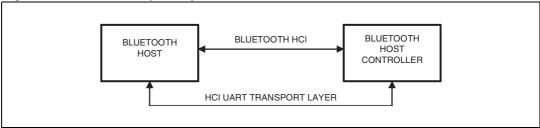

| 8            | HCI t | ranspo               | rt layer                                               | 48   |

|              | 8.1   | H4 UAI               | RT transport layer                                     | 48   |

|              | 8.2   | Enhand               | ced H4 SPI transport layer                             | 49   |

|              | 8.3   | H4 SPI               | transport layer                                        | 49   |

|              | 8.4   | eSCO                 | over HCI                                               | 49   |

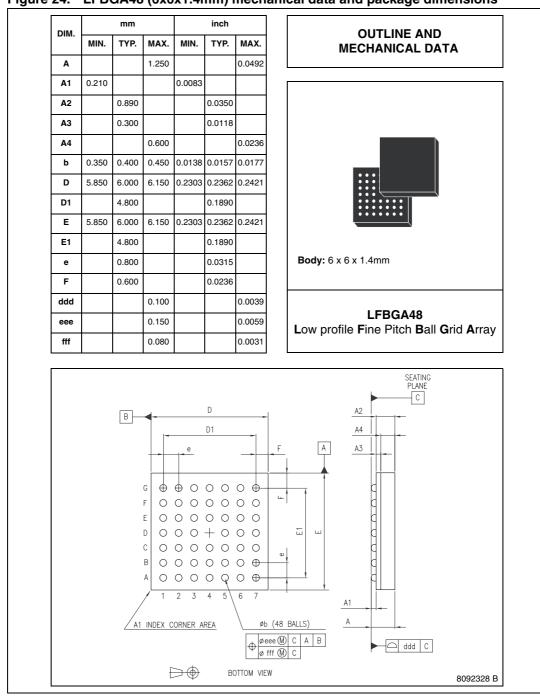

| 9            | Pack  | age info             | ormation                                               | 50   |

| 10           | Refe  | rences               |                                                        | 52   |

| 11           | Acro  | nyms a               | nd abbreviations                                       | 53   |

| 12           | Orde  | r codes              | ;                                                      | 56   |

| 13           | Revi  | sion his             | story                                                  | 57   |

| <b>5</b> 77  |       |                      | Dog ID 16067 Pov 2                                     | 0/50 |

| — , <u> </u> |       |                      | Doc ID 16067 Rev 2                                     | 3/58 |

List of tables STA2500D

## List of tables

| rabie i.  | Absolute maximum ratings                                                             | . / |

|-----------|--------------------------------------------------------------------------------------|-----|

| Table 2.  | Operating ranges                                                                     |     |

| Table 3.  | DC input specification                                                               | . 8 |

| Table 4.  | DC output specification                                                              | . 8 |

| Table 5.  | System clock supported frequencies                                                   | . 8 |

| Table 6.  | System clock overall specifications                                                  | . 8 |

| Table 7.  | System clock, sine wave specifications                                               |     |

| Table 8.  | System clock, digital clock DC specifications                                        | . 9 |

| Table 9.  | System clock, digital clock AC specifications                                        | . 9 |

| Table 10. | Low power clock specifications                                                       | . 9 |

| Table 11. | Current consumption                                                                  |     |

| Table 12. | The STA2500D pin list (functional and supply)                                        | 14  |

| Table 13. | Configuration programming                                                            |     |

| Table 14. | I/O supply split diagram                                                             |     |

| Table 15. | Mbps receiver parameters - GFSK                                                      |     |

| Table 16. | Mbps receiver parameters - $\pi$ /4-DQPSK                                            |     |

| Table 17. | Mbps receiver parameters - 8-DPSK                                                    |     |

| Table 18. | Transmitter parameters                                                               |     |

| Table 19. | Output power: class 1 control signals                                                |     |

| Table 20. | Output power: class 1 device pin configuration (depending on SW parameter download). |     |

| Table 21. | Output power: class 1 device pin configuration (depending on SW parameter download). |     |

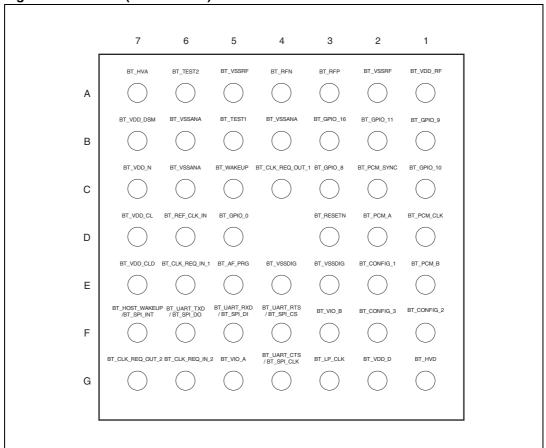

| Table 22. | Use of the BT_CLK_REQ_IN and BT_CLK_REQ_OUT signals in different modes               |     |

| Table 23. | Low power modes                                                                      |     |

| Table 24. | WLAN HW signal assignment                                                            |     |

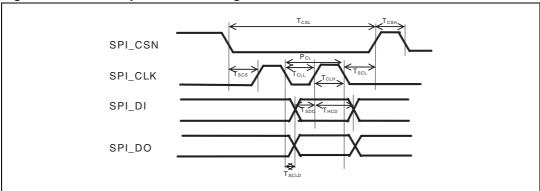

| Table 25. | SPI timing parameters                                                                |     |

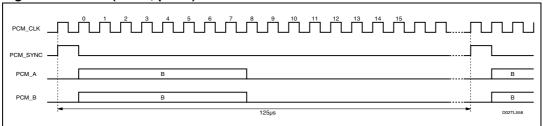

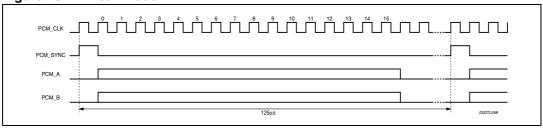

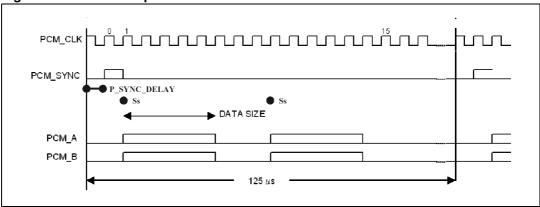

| Table 26. | PCM interface parameters                                                             |     |

| Table 27. | PCM interface timing (at PCM_CLK = 2048 kHz)                                         |     |

| Table 28. | Examples of BT_GPIO pin programming                                                  |     |

| Table 29. | Package markings legend                                                              |     |

| Table 30. | References                                                                           |     |

| Table 31. | Acronyms and abbreviations                                                           |     |

| Table 32. | Ordering information                                                                 |     |

| Tahla 33  | Document revision history                                                            | 57  |

STA2500D List of figures

# **List of figures**

| Figure 1.        | Block diagram and electrical schematic                                                     | 12     |

|------------------|--------------------------------------------------------------------------------------------|--------|

| Figure 2.        | Pinout (bottom view)                                                                       |        |

| Figure 3.        | Active high clock request input and output combined with UART or SPI                       | 28     |

| Figure 4.        | Active low clock request input and output combined with UART                               | 28     |

| Figure 5.        | Active low clock request input and output combined with SPI                                | 28     |

| Figure 6.        | Deep sleep mode entry and wake-up through H4 UART                                          |        |

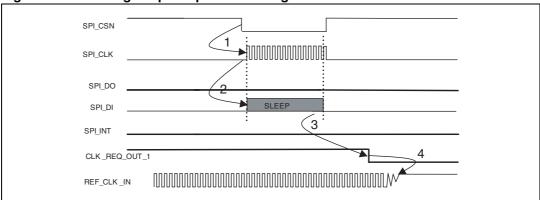

| Figure 7.        | Entering deep sleep mode through enhanced H4 SPI                                           |        |

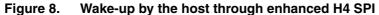

| Figure 8.        | Wake-up by the host through enhanced H4 SPI                                                | 33     |

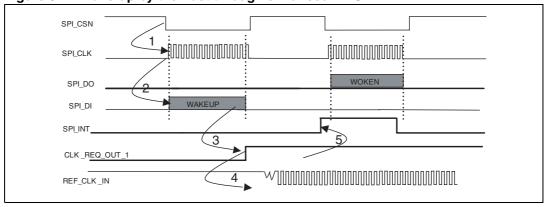

| Figure 9.<br>SPI | Wake-up by the Bluetooth controller with data transmission to the host, through enhance 34 | ed H4  |

| Figure 10.       | Deep sleep mode entry and wake-up through H4 SPI                                           | 35     |

| Figure 11.<br>36 | Entering deep sleep mode, pending data on UART interface, through UART with hand           | lshake |

| Figure 12.       | Wakeup by host through UART with handshake                                                 | 37     |

| Figure 13.       | PTA diagram                                                                                |        |

| Figure 14.       | WLAN master                                                                                | 39     |

| Figure 15.       | Bluetooth master                                                                           | 39     |

| Figure 16.       | SPI interface                                                                              | 41     |

| Figure 17.       | SPI data transfer timing for data length of 8 bits and lsb first, full duplex              | 42     |

| Figure 18.       | SPI setup and hold timing                                                                  | 43     |

| Figure 19.       | PCM (A-law, µ-law) standard mode                                                           | 44     |

| Figure 20.       | Linear mode                                                                                | 44     |

| Figure 21.       | Multislot operation                                                                        | 44     |

| Figure 22.       | PCM interface timing                                                                       | 45     |

| Figure 23.       | UART transport layer                                                                       | 48     |

| Figure 24.       | LFBGA48 (6x6x1.4mm) mechanical data and package dimensions                                 | 50     |

| Figure 25.       | Package markings                                                                           | 51     |

Description STA2500D

## 1 Description

The STA2500D is a single chip Bluetooth solution that is fully optimized for automotive applications such as telematics, navigation and portable navigation. Power consumption levels are targeted at battery powered devices and single chip solution brings cost advantages. Manufacturers can easily and quickly integrate the STA2500D on their product to enable a rapid time to market.

STA2500D supports the Bluetooth specification V2.1 + EDR ("Lisbon") and is optimized in terms of RF performance and cost.

The STA2500D is a ROM-based solution targeted at applications requiring integration up to HCI level. Patch RAM is available, enabling multiple patches/upgrades and fast time to volume. The STA2500D's main interfaces are UART or SPI for HCI transport, PCM for voice and GPIOs for control purposes.

The radio has been designed specifically for single chip requirements, for low power consumption and minimum BOM count.

STA2500D Quick reference data

## 2 Quick reference data

BT\_VIO\_x means BT\_VIO\_A, BT\_VIO\_B.

BT\_HVx means BT\_HVA, BT\_HVD.

(See also *Table 12*.)

## 2.1 Absolute maximum ratings

The absolute maximum rating (AMR) corresponds to the maximum value that can be applied without leading to instantaneous or very short-term unrecoverable hard failure (destructive breakdown).

Table 1. Absolute maximum ratings

| Symbol              | Parameter                                                                                       | Min. | Max.  | Unit |

|---------------------|-------------------------------------------------------------------------------------------------|------|-------|------|

| BT_HVx              | Core supply voltages                                                                            | -0.3 | 4.0   | V    |

| BT_VIO_A            | Supply voltage I/O                                                                              | -0.3 | 4.0   | V    |

| BT_VIO_B            | Supply voltage I/O (for the low power clock)                                                    | -0.3 | 4.0   | V    |

| BT_V <sub>in</sub>  | Input voltage of any digital pin                                                                | -0.3 | 4.0   | V    |

| V <sub>ssdiff</sub> | Maximum voltage difference between different types of $\ensuremath{\text{V}_{\text{SS}}}$ pins. | -0.3 | 0.3   | V    |

| T <sub>stg</sub>    | Storage temperature                                                                             | - 65 | + 150 | °C   |

## 2.2 Operating ranges

Operating ranges define the limits for functional operation and parametric characteristics of the device. Functionality outside these limits is not implied.

Table 2. Operating ranges

| Symbol              | Parameter                                    | Min. | Тур. | Max. | Unit |

|---------------------|----------------------------------------------|------|------|------|------|

| BT_T <sub>amb</sub> | Operating ambient temperature                | -40  | 25   | +85  | °C   |

| BT_HVx              | Core supply voltages                         | 2.65 | 2.75 | 2.85 | V    |

| BT_VIO_A            | I/O supply voltage                           | 1.65 | -    | 2.85 | ٧    |

| BT_VIO_B            | I/O supply voltage (for the low power clock) | 1.17 | -    | 2.85 | ٧    |

Quick reference data STA2500D

## 2.3 I/O specifications

The I/Os comply with the EIA/JEDEC standard JESD8-B.

Table 3. DC input specification

| Symbol             | Parameter                                                                                          | Min.               | Тур. | Max.                                | Unit |

|--------------------|----------------------------------------------------------------------------------------------------|--------------------|------|-------------------------------------|------|

| V <sub>IL_BT</sub> | Low level input voltage                                                                            | -0.2               | -    | 0.35 *<br>BT_VIO_x                  | V    |

| V <sub>IH_BT</sub> | High level input voltage                                                                           | 0.65 *<br>BT_VIO_x | -    | (BT_VIO_x<br>+ 0.2) and<br>(≤ 2.85) | V    |

| C <sub>in_BT</sub> | Input capacitance <sup>(1)</sup>                                                                   | 1                  | -    | 2.5                                 | pF   |

| R <sub>pu</sub>    | Pull-up equivalent resistance (with V <sub>in</sub> = 0 V)                                         | 31                 | 47   | 73                                  | kΩ   |

| R <sub>pd</sub>    | Pull-down equiv. resistance (with V <sub>in</sub> = BT_VIO_x)                                      | 29                 | 50   | 100                                 | kΩ   |

| V <sub>hyst</sub>  | Schmitt trigger hysteresis (at BT_VIO_A = 1.8 V) except for BT_CONFIG1-3, BT_RESETN, BT_WAKEUP     | 0.4                | 0.5  | 0.6                                 | V    |

| V <sub>hyst</sub>  | Schmitt trigger hysteresis (at BT_VIO_x = 1.8 V) for BT_CONFIG1-3, BT_RESETN, BT_WAKEUP, BT_LP_CLK | 0.223              | -    | 0.314                               | V    |

| V <sub>hyst</sub>  | Schmitt trigger hysteresis (at BT_VIO_B = 1.3 V)                                                   | 0.2                | -    | 0.3                                 | V    |

<sup>1.</sup> Except for the system clock.

Table 4. DC output specification

| Symbol             | Parameter                 | Condition                  | Min.               | Тур. | Max. | Unit |

|--------------------|---------------------------|----------------------------|--------------------|------|------|------|

| V <sub>OL_BT</sub> | Low level output voltage  | $I_d = X^{(1)} \text{ mA}$ | -                  | -    | 0.15 | V    |

| V <sub>OH_BT</sub> | High level output voltage | $I_d = X^{(1)} \text{ mA}$ | BT_VIO_x<br>- 0.25 | -    | -    | V    |

<sup>1.</sup> X is the source/sink current under worst-case conditions according to the drive capabilities (see Section 3)

## 2.4 Clock specifications

The STA2500D supports, on the BT\_REF\_CLK\_IN pin, the system clock both as a sine wave clock and as a digital clock. For configuration, see *Table 12*: pin BT\_VDD\_CLD (E6).

Table 5. System clock supported frequencies

| Symbol          | Parameter                  | Values                                         | Unit |

|-----------------|----------------------------|------------------------------------------------|------|

| F <sub>IN</sub> | Clock input frequency list | 9.6, 10, 13, 16, 16.8, 19.2,<br>26, 33.6, 38.4 | MHz  |

Table 6. System clock overall specifications

| Symbol             | Parameter                    | Min. | Тур. | Max. | Unit |

|--------------------|------------------------------|------|------|------|------|

| F <sub>INTOL</sub> | Tolerance on input frequency | -20  | -    | 20   | ppm  |

STA2500D Quick reference data

Table 7. System clock, sine wave specifications

| Symbol            | Parameter                                                                         | Min. | Тур. | Max. | Unit   |

|-------------------|-----------------------------------------------------------------------------------|------|------|------|--------|

| V <sub>PP</sub>   | Peak to peak voltage range                                                        | 0.27 | 0.5  | 1.8  | V      |

| N <sub>H</sub>    | Total harmonic content of input signal                                            | -    | -    | -25  | dBc    |

| Z <sub>INRe</sub> | Real part of parallel input impedance at pin                                      | 30   | 60   | 90   | kΩ     |

| Z <sub>INIm</sub> | Imaginary part of parallel input impedance at pin                                 | -    | 5    | 8    | pF     |

| Z <sub>IDRe</sub> | Real impedance discrepancy between active and non-active mode of clock input      | -    | -    | 7    | kΩ     |

| Z <sub>IDim</sub> | Imaginary impedance discrepancy between active and non-active mode of clock input | -    | -    | 500  | fF     |

|                   | Phase noise @ 10 kHz <sup>(1)</sup>                                               | -    | -    | -126 | dBc/Hz |

<sup>1.</sup> Equivalent to max 10 ps time jitter (rms).

Table 8. System clock, digital clock DC specifications

| Symbol          | Parameter                | Min.                 | Тур. | Max.                                  | Unit |

|-----------------|--------------------------|----------------------|------|---------------------------------------|------|

| V <sub>IL</sub> | Low level input voltage  | -0.2                 | -    | 0.35 *<br>BT_VDD_CLD                  | V    |

| V <sub>IH</sub> | High level input voltage | 0.65 *<br>BT_VDD_CLD | -    | (BT_VDD_CLD<br>+ 0.2) and<br>(≤ 2.85) | ٧    |

| C <sub>IN</sub> | Input capacitance        | -                    | 5    | 8                                     | pF   |

Table 9. System clock, digital clock AC specifications

| Symbol             | Parameter                           | Min. | Тур. | Max. | Unit   |

|--------------------|-------------------------------------|------|------|------|--------|

| T <sub>RISE</sub>  | 10% - 90% rise time                 | -    | 1.5  | 6    | ns     |

| T <sub>FALL</sub>  | 90% - 10% fall time                 | -    | 1.5  | 6    | ns     |

| D <sub>CYCLE</sub> | Duty cycle                          | 45   | 50   | 55   | %      |

| -                  | Phase noise @ 10 kHz <sup>(1)</sup> | -    | -    | -121 | dBc/Hz |

<sup>1.</sup> Equivalent to max 15 ps time jitter (rms).

Table 10. Low power clock specifications

The low power clock pin is powered by connecting BT\_VIO\_B to the wanted supply.

| Symbol            | Parameter                                     | Min.               | Тур. | Max.               | Unit |  |

|-------------------|-----------------------------------------------|--------------------|------|--------------------|------|--|

| F <sub>IN</sub>   | Clock input frequencies                       | 3.2, 32, 32.768    |      |                    |      |  |

| -                 | Duty cycle                                    | 30                 | -    | 70                 | %    |  |

| -                 | Tolerance on input frequency                  | -250               | -    | 250                | ppm  |  |

| V <sub>IL</sub>   | Low level input voltage                       | -                  | -    | 0.35 *<br>BT_VIO_B | V    |  |

| V <sub>IH</sub>   | High level input voltage                      | 0.65 *<br>BT_VIO_B | -    | -                  | V    |  |

| V <sub>hyst</sub> | Schmitt trigger hysteresis (BT_VIO_B = 1.8 V) | 0.4                | 0.5  | 0.6                | V    |  |

Quick reference data STA2500D

Table 10. Low power clock specifications (continued)

The low power clock pin is powered by connecting BT\_VIO\_B to the wanted supply.

| Symbol            | Parameter                                     | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------------------------------|------|------|------|------|

| V <sub>hyst</sub> | Schmitt trigger hysteresis (BT_VIO_B = 1.3 V) | 0.2  | 0.3  | 0.4  | V    |

| C <sub>IN</sub>   | Input capacitance                             | 1    | -    | 2.5  | pF   |

| T <sub>RISE</sub> | 10% - 90% rise time <sup>(1)</sup>            | -    | -    | 1    | μS   |

| T <sub>FALL</sub> | 90% - 10% fall time <sup>(1)</sup>            | -    | -    | 1    | μS   |

| -                 | Total jitter <sup>(2)</sup>                   | -    | -    | 250  | ppm  |

The rise and fall time are not the most important parameters for the low power clock input due to the Schmitt trigger logic. It

is more important that the noise on the Low power clock line remains substantially below the hysteresis in amplitude.

## 2.5 Current consumption

$T_{amb}$  = 25°C, 13 MHz digital clock, 7 dBm output power for BR packets, 3 dBm output power for EDR packets.

Table 11. Current consumption<sup>(1)</sup>

| State                                                                                                      | Тур.       | Unit |

|------------------------------------------------------------------------------------------------------------|------------|------|

| Complete Power Down                                                                                        | 1          | μА   |

| Deep Sleep mode                                                                                            | 20         | μА   |

| Functional Sleep mode <sup>(2)</sup>                                                                       | 1.2        | mA   |

| Sniff mode (1.28 s, 2 attempts, 0 timeouts), combined with H4 UART Deep Sleep mode                         |            |      |

| (see section 6.10.3) Master mode                                                                           | 55         | μА   |

| Slave mode                                                                                                 | 83         | μΑ   |

| Inquiry scan (1.28 seconds period), combined with H4 UART Deep Sleep mode (see section 6.10.3)             | 318        | μА   |

| HW Page scan (1.28 seconds period), combined with H4 UART Deep Sleep mode (see section 6.10.3)             | 312        | μА   |

| HW Inquiry and Page scan (1.28 seconds period), combined with H4 UART Deep Sleep mode (see section 6.10.3) | 591        | μА   |

| Idle ACL connection (Master)                                                                               | 3.6        | mA   |

| Idle ACL connection (Slave)                                                                                | 8.2        | mA   |

| Active: audio (HV3) Master (not sniffed)                                                                   | 11.7       | mA   |

| Active: audio (HV3) Slave (Sniff 1.28 s, 2 attempts, 0 timeouts)                                           | 10.6       | mA   |

| Active: data (DH1) Master or Slave<br>(172.8 kbps asymmetrical in TX mode)<br>(172.8 kbps symmetrical)     | 23<br>28.5 | mA   |

<sup>2.</sup> The total jitter is defined as the error that can appear on the actual frequency between two clock edges compared to the perfect frequency. Due to this, the total jitter value must contain the jitter itself and the error due to the accuracy on the clock frequency. The lower the accuracy, the smaller the jitter is allowed to be.

STA2500D Quick reference data

Table 11. Current consumption<sup>(1)</sup> (continued)

| State                                                                                 | Тур. | Unit |

|---------------------------------------------------------------------------------------|------|------|

| Active: data (DH5) Master or Slave                                                    |      |      |

| (723.2 kbps asymmetrical in TX mode)                                                  | 35.4 | mA   |

| (433.9 kbps symmetrical)                                                              | 35.4 | mA   |

| Active: data (2-DH5) Master or Slave (869.7 kbps symmetrical)                         | 35.4 | mA   |

| Active: data (3-DH5) Master or Slave (1306.9 kbps symmetrical)                        | 35.4 | mA   |

| Active: audio eSCO (EV3), (64 kbps symmetrical T <sub>eSCO</sub> = 6)                 |      |      |

| Master mode                                                                           | 12   | mA   |

| Slave mode                                                                            | 15   | mA   |

| Active: audio eSCO (2-EV3), (64 kbps symmetrical T <sub>eSCO</sub> = 12)              |      |      |

| Master mode                                                                           | 7.8  | mA   |

| Slave mode                                                                            | 11.7 | mA   |

| Active: audio eSCO (3-EV3), (64 kbps symmetrical T <sub>eSCO</sub> = 18)              |      |      |

| Master mode                                                                           | 6.5  | mA   |

| Slave mode                                                                            | 10.5 | mA   |

| Active: audio eSCO (EV5), (64 kbps symmetrical T <sub>eSCO</sub> = 36), Master mode   | 8    | mA   |

| Active: audio eSCO (EV5), (64 kbps symmetrical T <sub>eSCO</sub> = 36), Slave mode    | 11.9 | mA   |

| Active: audio eSCO (2-EV5), (64 kbps symmetrical T <sub>eSCO</sub> = 36), Master mode | 6.3  | mA   |

| Active: audio eSCO (3-EV5), (64 kbps symmetrical T <sub>eSCO</sub> = 36), Master mode | 5.75 | mA   |

<sup>1.</sup> The power consumption (except for power safe modes i.e. complete power down and deep sleep mode) will rise (with approx. 200  $\mu$ A) if an analog system clock is used instead of a digital clock.

<sup>2.</sup> In functional sleep mode, the baseband clock is still running.

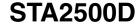

# 3 Block diagram and electrical schematic

Figure 1. Block diagram and electrical schematic

12/58 Doc ID 16067 Rev 2

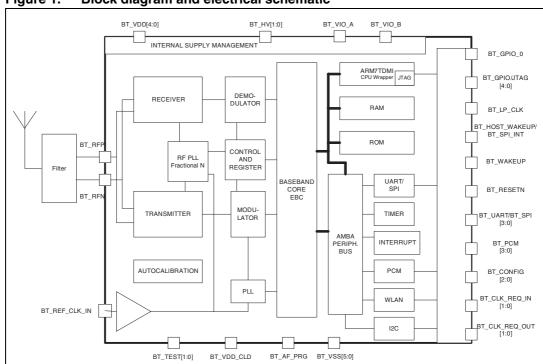

STA2500D Pinout

### 4 Pinout

Figure 2. Pinout (bottom view)

## 4.1 Pin description and assignment

Table 12 shows the pin list of the STA2500D.

In columns "Reset" and "Default after reset", the "PD/PU" shows the pads implementing an internal pull-down/up.

The column "Reset" shows the state of the pins during hardware reset; the column "Default after reset" shows the state of the pins after the hardware reset state is left, but before any software parameter download.

The column "Type" describes the pin directions:

- I for Input (All inputs have a Schmitt trigger function.)

- O for Output

- I/O for Input/Output

- O/t for tri-state output

Pinout STA2500D

For the output pin the default drive capability is 2 mA, except for pin K3 (BT\_GPIO\_11) and pin L3 (BT\_GPIO\_8) where it is 8 mA such that when used for Class 1, these 2 pins can be used for a switch control in a cheaper way.

Table 12. The STA2500D pin list (functional and supply)

| Name                          | Pin<br># | Description                                                                         | Туре               | Reset <sup>(1)</sup>                 | Default <sup>(2)</sup><br>after reset |  |

|-------------------------------|----------|-------------------------------------------------------------------------------------|--------------------|--------------------------------------|---------------------------------------|--|

| Clock and reset pins          |          |                                                                                     |                    |                                      |                                       |  |

| BT_RESETN                     | D3       | Global reset - active low                                                           | -                  | -                                    |                                       |  |

| BT_REF_CLK_IN                 | D6       | Reference clock input <sup>(3)</sup>                                                | I                  | Input                                | Input                                 |  |

| BT_LP_CLK                     | G3       | Low power clock input                                                               | -                  | -                                    |                                       |  |

| SW initiated low power        | r mod    | le                                                                                  |                    |                                      |                                       |  |

| BT_CLK_REQ_OUT_1              | C4       | Wake-up signal to Host (Active high or Active low, depending on configuration pins) |                    | Input PD/PU,<br>depends on<br>config | Output<br>depends on<br>config        |  |

| BT_CLK_REQ_OUT_2              | G7       | Wake-up signal to Host. Active low (SPI mode only)                                  | I/O <sup>(4)</sup> | Input PU                             | I/O depends on config                 |  |

| BT_CLK_REQ_IN_1               | E6       | Clock request input (Active high)                                                   |                    | Input PD                             | Input PD                              |  |

| BT_CLK_REQ_IN_2               | G6       | Clock request input (Active low)                                                    |                    | Input PU                             | Input PU                              |  |

| BT_HOST_WAKEUP/<br>BT_SPI_INT | F7       | Wake-up signal to Host or SPI interrupt                                             |                    | Input PD                             | Output                                |  |

| BT_WAKEUP                     | C5       | Wake-up signal to Bluetooth (Active high)                                           | I/O                | Input (5)                            | Input                                 |  |

| UART interface                |          |                                                                                     |                    |                                      | •                                     |  |

| BT_UART_RXD/                  | F5       | UART receive data                                                                   |                    |                                      | Input PD                              |  |

| BT_SPI_DI                     | гэ       | SPI data in                                                                         |                    | In a st DD                           | Input PD                              |  |

| BT_UART_TXD/                  | F6       | UART transmit data                                                                  |                    | Input PD                             | Output high                           |  |

| BT_SPI_DO                     | 10       | SPI data out                                                                        | I/O <sup>(4)</sup> |                                      | Input PD                              |  |

| BT_UART_CTS/                  | G4       | UART clear to send                                                                  |                    |                                      | Input PU                              |  |

| BT_SPI_CLK                    | αт       | SPI clock                                                                           |                    | Input PU                             | Input PD                              |  |

| BT_UART_RTS/                  | F4       | UART request to send                                                                |                    | input i O                            | Output low                            |  |

| BT_SPI_CSN                    | 1 7      | SPI chip select                                                                     |                    |                                      | Input PU                              |  |

| PCM interface                 |          |                                                                                     |                    |                                      |                                       |  |

| BT_PCM_SYNC                   | C2       | PCM frame signal                                                                    |                    |                                      |                                       |  |

| BT_PCM_CLK                    | D1       | PCM clock signal                                                                    | I/O <sup>(4)</sup> | Input PD                             | Input PD                              |  |

| BT_PCM_A                      | D2       | PCM data                                                                            | ] "//              | Iniput PD                            | Iniput PD                             |  |

| BT_PCM_B                      | E1       | PCM data                                                                            |                    |                                      |                                       |  |

| JTAG interface                |          |                                                                                     |                    |                                      |                                       |  |

| BT_GPIO_9                     | B1       | JTAG_TDI or GPIO                                                                    | -                  | Input PU <sup>(6)</sup>              | Input PU <sup>(6)</sup>               |  |

|                               |          |                                                                                     |                    |                                      |                                       |  |

STA2500D Pinout

Table 12. The STA2500D pin list (functional and supply) (continued)

| Name                                      | Pin<br># | Description                                                                                                                                                     | Туре               | Reset <sup>(1)</sup>    | Default <sup>(2)</sup><br>after reset |

|-------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------|---------------------------------------|

| BT_GPIO_11                                | B2       | JTAG_TDO or GPIO                                                                                                                                                | -                  | Input PD <sup>(6)</sup> | Input PD <sup>(6)</sup>               |

| BT_GPIO_10                                | C1       | JTAG_TMS or GPIO                                                                                                                                                | I/O <sup>(4)</sup> | Input PD <sup>(6)</sup> | Input PD <sup>(6)</sup>               |

| BT_GPIO_16                                | ВЗ       | JTAG_NTRST (Active low) or Alternate function.                                                                                                                  | -                  | Input PD <sup>(6)</sup> | Input PD <sup>(6)</sup>               |

| BT_GPIO_8                                 | СЗ       | JTAG_TCK or GPIO                                                                                                                                                | -                  | Input PD <sup>(6)</sup> | Input PD <sup>(6)</sup>               |

| General purpose input                     | outp/    | ut pins                                                                                                                                                         |                    |                         |                                       |

| BT_GPIO_0                                 | D5       | General purpose I/O                                                                                                                                             | I/O <sup>(4)</sup> | Input PD                | Input PD                              |

| Configuration pins                        |          |                                                                                                                                                                 |                    |                         |                                       |

| BT_CONFIG_1                               | E2       |                                                                                                                                                                 | -                  | -                       | -                                     |

| BT_CONFIG_2                               | F1       | Configuration signal                                                                                                                                            | I                  | Input                   | Input                                 |

| BT_CONFIG_3                               | F2       |                                                                                                                                                                 | -                  | -                       | -                                     |

| RF signals                                |          |                                                                                                                                                                 |                    |                         |                                       |

| BT_RFP                                    | А3       | Differential DE new                                                                                                                                             | I/O                | -                       | -                                     |

| BT_RFN                                    | A4       | Differential RF port                                                                                                                                            | 1/0                | -                       | -                                     |

| Power supply                              |          |                                                                                                                                                                 |                    |                         |                                       |

| BT_HVA                                    | A7       | Downer cumply (Connect to 0.75 V)                                                                                                                               |                    |                         |                                       |

| BT_HVD                                    | G1       | Power supply (Connect to 2.75 V)                                                                                                                                | -                  | -                       | -                                     |

| BT_VIO_A                                  | G5       | 1.65 V to 2.85 V I/Os supply <sup>(7)</sup>                                                                                                                     | -                  | -                       | -                                     |

| BT_VIO_B                                  | F3       | 1.17 V to 2.85 V I/Os supply <sup>(7)</sup>                                                                                                                     | -                  | -                       | -                                     |

| System 1.65 V BT_VDD_CLD E7 (Connereferen |          | System clock supply 1.65 V to 2.85 V (Connect to BT_VIO_A in case of a digital reference clock input, to BT_VSSANA in case of an analog reference clock input.) | -                  | -                       | -                                     |

| BT_VSSDIG                                 | E3<br>E4 | Digital ground                                                                                                                                                  | -                  | -                       | -                                     |

|                                           | B4       |                                                                                                                                                                 |                    |                         |                                       |

| BT_VSSANA                                 | B6       | Analog ground                                                                                                                                                   | -                  | -                       | -                                     |

|                                           | C6       |                                                                                                                                                                 |                    |                         |                                       |

| BT_VSSRF                                  | A2<br>A5 | RF ground                                                                                                                                                       | -                  | -                       | -                                     |

| BT_VDD_CL                                 | D7       | Internal supply decoupling/Regulator output. Need 220nF decoupling capacitor to BT_VSSANA.                                                                      | -                  | -                       | -                                     |

Pinout STA2500D

Table 12. The STA2500D pin list (functional and supply) (continued)

| Name       | Pin<br>#                                                                                      | Description                                                                                | Туре | Reset <sup>(1)</sup> | Default <sup>(2)</sup><br>after reset |  |

|------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|----------------------|---------------------------------------|--|

| BT_VDD_D   | G2                                                                                            | Internal supply decoupling/Regulator output. Need 220nF decoupling capacitor to BT_VSSDIG. | -    | -                    | -                                     |  |

| BT_VDD_DSM | B7                                                                                            | Internal supply decoupling/Regulator output. Need 220nF decoupling capacitor to BT_VSSANA. | -    | -                    | -                                     |  |

| BT_VDD_N   | C7                                                                                            | Internal supply decoupling/Regulator output. Need 220nF decoupling capacitor to BT_VSSANA. | -    | -                    | -                                     |  |

| BT_VDD_RF  | Internal supply decoupling/Regulator output.  A1 Need 220nF decoupling capacitor to BT_VSSRF. |                                                                                            | -    | -                    | -                                     |  |

| Other pins | Other pins                                                                                    |                                                                                            |      |                      |                                       |  |

| BT_TEST1   | B5                                                                                            | Test pin                                                                                   | I/O  | Input <sup>(8)</sup> | Input <sup>(8)</sup>                  |  |

| BT_TEST2   | A6                                                                                            | iest μιτ                                                                                   | 1/0  | input · /            | input · /                             |  |

| BT_AF_PRG  | E5                                                                                            | Test pin (Leave unconnected) <sup>(9)</sup>                                                | I/O  | Open                 | Open                                  |  |

- 1. Pin behaviour during HW reset (BT\_RESETN low).

- 2. Pin behaviour immediately after HW reset and internal chip initialization, but before SW parameter download.

- 3. See also pin BT\_VDD\_CLD in Table 12.

- Reconfigurable I/O pin. The functionality of these I/Os can be configured through software parameter download (see Section 7.5).

- 5. Should be strapped to BT\_VSSDIG if not used.

- 6. JTAG mode.

- 7. Described in Section 4.3.

- 8. To be strapped to BT\_VSSANA.

- 9. Pin is ST reserved for test function and it must be soldered to an isolated pad (not connected to anything, just floating).

## 4.2 HW configuration of the STA2500D

By means of the three configuration pins, one can select the Host interface (UART or SPI) and clock request signal polarity to be used at startup.

The available combinations of Host interface and protocol are illustrated in *Table 13* (where '1' = BT\_VIO\_A and '0' = BT\_VSSDIG). Additionally, the polarity of the BT\_CLK\_REQ signals can be programmed through the same pins. The polarity of the BT\_CLK\_REQ\_IN and BT\_CLK\_REQ\_OUT signals is further described in *Section 6.8*.

STA2500D Pinout

Table 13. Configuration programming

| BT_CONFIG_1 | BT_CONFIG_2 | BT_CONFIG_3 | Communication<br>Protocol      | BT_CLK_REQ_OUT_1 | BT_CLK_REQ_OUT_2       |

|-------------|-------------|-------------|--------------------------------|------------------|------------------------|

| 0           | 1           | 0           | H4 UART                        | Active high      | Depending on SW config |

| 0           | 1           | 1           | H4 UART                        | Active low       | Depending on SW config |

| 1           | 1           | 0           | Reserved                       | Reserved         | Reserved               |

| 1           | 1           | 1           | Reserved                       | Reserved         | Reserved               |

| 1           | 0           | 0           | Reserved                       | Reserved         | Reserved               |

| 1           | 0           | 1           | Enhanced H4 SPI <sup>(1)</sup> | Active high      | Active low             |

| 0           | 0           | 1           | Reserved                       | Reserved         | Reserved               |

| 0           | 0           | 0           | Reserved                       | Reserved         | Reserved               |

<sup>1.</sup> In order to get other SPI modes, the Host must send a specific configuration at start-up in addition of these configuration pins.

## 4.3 I/O Supply

The device STA2500D has two different I/O supplies: BT\_VIO\_A and BT\_VIO\_B.

The two different pins may be potentially connected to separate dedicated voltage supplies in order to harmonize the digital levels to the platform.

They are linked to different interfaces as described in Table 14.

Table 14. I/O supply split diagram

| I/O supply name | Voltage<br>range [V] | Function          | Associated pins                                                                                                         |

|-----------------|----------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|

|                 |                      | Configuration     | BT_CONFIG_1, BT_CONFIG_2, BT_CONFIG_3                                                                                   |

|                 |                      |                   | BT_WAKEUP                                                                                                               |

|                 |                      | Control           | BT_RESETN                                                                                                               |

|                 |                      |                   | BT_CLK_REQ_OUT_1, BT_CLK_REQ_OUT_2                                                                                      |

| DT 1/10 A       |                      | GPIO (JTAG)       | BT_GPIO_8 (JTAG_TCK), BT_GPIO_9 (JTAG_TDI),<br>BT_GPIO_10 (JTAG_TMS), BT_GPIO_11 (JTAG_TDO),<br>BT_GPIO_16 (JTAG_NTRST) |

| BT_VIO_A        | 1.65 - 2.85          | PCM               | BT_PCM_A, BT_PCM_B, BT_PCM_SYNC, BT_PCM_CLK                                                                             |

|                 |                      | Control           | BT_REG_CTRL                                                                                                             |

|                 |                      | UART (SPI)        | BT_UART_RXD (SPI_DI), BT_UART_TXD (SPI_DO), BT_UART_RTS (SPI_CSN), BT_UART_CTS (SPI_CLK), BT_HOST_WAKEUP (SPI_INT)      |

|                 |                      | Control (GPIO)    | BT_CLK_REQ_IN_1 (GPIO_1), BT_CLK_REQ_IN_2 (GPIO_2)                                                                      |

|                 |                      | GPIO              | BT_GPIO_0                                                                                                               |

| BT_VIO_B        | 1.17 - 2.85          | Low - power clock | BT_LP_CLK                                                                                                               |

## 5 Functional description

### 5.1 Transmitter

The transmitter uses the serial transmit data from the Bluetooth Controller. The transmitter modulator converts this data into GFSK,  $\pi/4$ -DQPSK or 8-DPSK modulated I and Q digital signals for respectively 1, 2 and 3 Mbps transmission speed. These signals are then converted to analog signals that are low pass filtered before up-conversion. The carrier frequency drift is limited by a closed loop PLL.

### 5.2 Receiver

The STA2500D implements a low-IF receiver for Bluetooth modulated input signals. The radio signal is taken from a balanced RF input and amplified by an LNA. The mixers are driven by two quadrature LO signals, which are locally generated from a VCO signal running at twice the frequency. The I and Q mixer output signals are band pass filtered by a polyphase filter for channel filtering and image rejection. The output of the band pass filter is amplified by a VGA to the optimal input range for the A/D converter. Further channel filtering is done in the digital part. The digital part demodulates the GFSK,  $\pi$ /4-DQPSK or 8-DPSK coded bit stream by evaluating the phase information. RSSI data is extracted. Overall automatic gain amplification in the receive path is controlled digitally. The RC time constants for the analog filters are automatically calibrated on chip.

### 5.3 PLL

The on chip VCO is part of a PLL. The tank resonator circuitry for the VCO is completely integrated without need of external components. Variations in the VCO centre frequency are calibrated out automatically.

### 5.4 Bluetooth controller V1.2 and V2.0 + EDR features

The Bluetooth controller is backward compatible with the Bluetooth specification V1.2 [] and V2.0 + EDR []. Here below is a list with the main features of those specifications:

- Adaptive Frequency Hopping (AFH): hopping kernel, channel assessment as Master and as Slave

- Fast Connection: Interlaced scan for Page and Inquiry scan, answer FHS at first reception, RSSI used to limit range

- Extended SCO (eSCO) links: supports EV3, EV4 and EV5 packets

- Channel Quality Driven Data Rate change (CQDDR)

- QoS Flush

- Synchronization: BT clocks are available at HCl level for synchronization of parallel applications on different Slaves

- L2CAP Flow & Error control

- LMP SCO handling

- 2 Mbps packet types

- ACL: 2-DH1, 2-DH3, 2-DH5

- eSCO: 2-EV3, 2-EV5

- 3 Mbps packet types

- ACL: 3-DH1, 3-DH3, 3-DH5

- eSCO: 3-EV3, 3-EV5

## 5.5 Bluetooth controller V2.1 + EDR ("Lisbon")

- Encryption Pause/Resume (EPR)

- Extended Inquiry Response (EIR)

- Link Supervision Time Out (LSTO)

- Secure Simple Pairing

- Sniff Subrating

- Quality of Service (Qos)

- Packet Boundary Flag

- Erroneous Data Delivery

## 5.6 Processor and memory

- ARM7TDMI

- On chip RAM, including provision for patches

- On chip ROM, preloaded with SW up to HCI

## 5.7 TX output power control

The STA2500D supports output power control with advanced features:

- Basic feature:

- With the standard TX power control algorithm enabled, the STA2500D will adapt its output power when a remote BT device supports the RSSI feature; this allows the remote device to measure the link strength and to request the STA2500D to decrease/increase its output power. In case the remote device does not support the RSSI feature, the STA2500D will use its 'default' output power level.

- Advanced features, available via specific HCl commands:

- Enhanced power control feature: allows the STA2500D to decrease autonomously its output power until the remote BT device, supporting the RSSI feature, requests to increase the output power.

## 6 General specification

All the values are provided according to the Bluetooth specification V2.1 + EDR ("Lisbon") unless otherwise specified. The below values are preliminary and will be updated in the next version of this datasheet.

## 6.1 Receiver

All specifications below are given at device pin level and with the conditions as specified. Parameters are given for each of the 3 modulation types supported.

Typical is defined at  $T_{amb} = 25$  °C, BT\_HV = 2.75 V. Minimum and Maximum are worst cases over corner lots and temperature. Parameters are given at device pin, except for receiver interferers measured at antenna with a filter having a typical attenuation of 2.3 dB.

Table 15. Mbps receiver parameters - GFSK

| Symbol                    | Parameter                                             | Test condition                       | Min. | Тур.  | Max. | Unit |

|---------------------------|-------------------------------------------------------|--------------------------------------|------|-------|------|------|

| RFin                      | Input frequency range                                 | -                                    | 2402 | 1     | 2480 | MHz  |

| RXsensC                   | Receiver sensitivity (Clean transmitter)              | @ BER 0.1%                           | -    | -88   | -86  | dBm  |

| RXsensD                   | Receiver sensitivity (Dirty transmitter)              | @ BER 0.1%                           | -    | -87   | -84  | dBm  |

| RXmax                     | Maximum useable input signal level                    | @ BER 0.1%                           | 1    | 10    | 15   | dBm  |

| Receiver bloc             | cking performance @ BER 0.1%                          | on Channel 58 (without Filter        | )    |       |      |      |

| -                         | signal in GSM band 900 MHz<br>(824 MHz to 960 MHz)    | @ Input signal<br>strength = -67 dBm | -    | -15   | -    | dBm  |

| -                         | signal in GSM band 1800 MHz<br>(1805 MHz to 1990 MHz) | @ Input signal<br>strength = -67 dBm | -    | -2.5  | -    | dBm  |

| -                         | signal in WCDMA band<br>(2010 MHz to 2170 MHz)        | @ Input signal<br>strength = -67 dBm | -    | -1.5  | -    | dBm  |

| Receiver inte             | rferer performance @ BER 0.1%                         | ,<br>D                               |      |       |      |      |

| C/I <sub>co-channel</sub> | Co-channel interference                               | @ Input signal<br>strength = -60 dBm | -    | 9.5   | 11   | dB   |

| C/I <sub>1MHz</sub>       | Adjacent (±1 MHz) interference                        | @ Input signal<br>strength = -60 dBm | 1    | -9    | 0    | dB   |

| C/I <sub>+2MHz</sub>      | Adjacent (+2 MHz) interference                        | @ Input signal<br>strength = -60 dBm | -    | -40   | -30  | dB   |

| C/I <sub>-2MHz</sub>      | Adjacent (-2 MHz) interference                        | @ Input signal<br>strength = -67 dBm | -    | -26   | -9   | dB   |

| C/I <sub>+3MHz</sub>      | Adjacent (+3 MHz) interference                        | @ Input signal<br>strength = -67 dBm | -    | -46.5 | -40  | dB   |

Table 15. Mbps receiver parameters - GFSK (continued)

| Symbol                    | Parameter                        | Test condition                                   | Min. | Тур. | Max. | Unit |  |  |

|---------------------------|----------------------------------|--------------------------------------------------|------|------|------|------|--|--|

| C/I <sub>-3MHz</sub>      | Adjacent (-3 MHz) interference   | @ Input signal<br>strength = -67 dBm             | -    | -43  | -20  | dB   |  |  |

| C/I <sub>≥4MHz</sub>      | Adjacent (≥ ±4 MHz) interference | @ Input signal<br>strength = -67 dBm             | -    | -48  | -40  | dB   |  |  |

| Receiver inter-modulation |                                  |                                                  |      |      |      |      |  |  |

| IMD                       | Inter-modulation                 | Measured as defined in BT test specification []. | -39  | -32  | =    | dBm  |  |  |

Typical is defined at  $T_{amb}$  = 25 °C, BT\_HV = 2.75 V. Minimum and Maximum are worst cases over corner lots and temperature. Parameters are given at device pin, except for receiver interferers measured at antenna with a filter having a typical attenuation of 2.3 dB.

Table 16. Mbps receiver parameters -  $\pi$ /4-DQPSK

| Symbol                    | Parameter                                                                     | Test condition                       | Min. | Тур.  | Max.  | Unit |

|---------------------------|-------------------------------------------------------------------------------|--------------------------------------|------|-------|-------|------|

| RFin                      | Input frequency range                                                         | =                                    | 2402 |       | 2480  | MHz  |

| RXsensC                   | Receiver sensitivity (Clean transmitter)                                      | @ BER 0.01%                          | -    | -87   | -85   | dBm  |

| RXsensD                   | Receiver sensitivity (Dirty transmitter)                                      | @ BER 0.01%                          | -    | -86.5 | -84.5 | dBm  |

| RXmax                     | Maximum useable input signal level                                            | @ BER 0.1%                           | -15  | -9    | -     | dBm  |

| Receiver bloc             | cking performance @ BER 0.1%                                                  | on channel 58 (without Filter)       | )    |       |       |      |

| -                         | signal in GSM band 900 MHz<br>(824 MHz to 960 MHz)                            | @ Input signal<br>strength = -67 dBm | -    | -15.5 | -     | dBm  |

| -                         | signal in GSM band 1800 MHz<br>(1805 MHz to 1990 MHz)                         | @ Input signal<br>strength = -67 dBm | -    | -3.5  | -     | dBm  |

| -                         | signal in WCDMA band @ Input signal (2010 MHz to 2170 MHz) strength = -67 dBm |                                      | -    | -2.5  | -     | dBm  |

| Receiver inte             | rferer performance @ BER 0.1%                                                 | ,<br><b>D</b>                        |      |       |       |      |

| C/I <sub>co-channel</sub> | Co-channel interference                                                       | @ Input signal<br>strength = -60 dBm | -    | 11    | 13    | dB   |

| C/I <sub>1MHz</sub>       | Adjacent (±1 MHz) interference                                                | @ Input signal<br>strength = -60 dBm | -    | -11.5 | 0     | dB   |

| C/I <sub>+2MHz</sub>      | Adjacent (+2 MHz) interference                                                | @ Input signal<br>strength = -60 dBm | -    | -40   | -30   | dB   |

| C/I <sub>-2MHz</sub>      | Adjacent (-2 MHz) interference                                                | @ Input signal<br>strength = -67 dBm | -    | -20   | -7    | dB   |

| C/I <sub>+3MHz</sub>      | Adjacent (+3 MHz) interference                                                | @ Input signal<br>strength = -67 dBm | -    | -48.5 | -40   | dB   |

Table 16. Mbps receiver parameters -  $\pi$ /4-DQPSK (continued)

| Symbol               | Parameter                        | Test condition                       | Min. | Тур. | Max. | Unit |

|----------------------|----------------------------------|--------------------------------------|------|------|------|------|

| C/I <sub>-3MHz</sub> | Adjacent (-3 MHz) interference   | @ Input signal<br>strength = -67 dBm | -    | -47  | -20  | dB   |

| C/I <sub>≥4MHz</sub> | Adjacent (≥ ±4 MHz) interference | @ Input signal<br>strength = -67 dBm | -    | -48  | -40  | dB   |

Typical is defined at  $T_{amb}$  = 25 °C, BT\_HV = 2.75 V. Minimum and Maximum are worst cases over corner lots and temperature. Parameters are given at device pin, except for receiver interferers measured at antenna with a filter having a typical attenuation of 2.3 dB.

Table 17. Mbps receiver parameters - 8-DPSK

| Symbol                    | Parameter                                                                     | Test condition                       | Min. | Тур.  | Max.  | Unit |

|---------------------------|-------------------------------------------------------------------------------|--------------------------------------|------|-------|-------|------|

| RFin                      | Input frequency range                                                         | -                                    | 2402 | -     | 2480  | MHz  |

| RXsensC                   | Receiver sensitivity (Clean transmitter)                                      | @ BER 0.01%                          | -    | -79.5 | -77.5 | dBm  |

| RXsensD                   | Receiver sensitivity (Dirty transmitter)                                      | @ BER 0.01%                          | -    | -77   | -74.5 | dBm  |

| RXmax                     | Maximum useable input signal level                                            | @ BER 0.1%                           | -20  | -15   | -     | dBm  |

| Receiver bloc             | cking performance @ BER 0.1%                                                  | on channel 58 (without Filter        | )    |       |       |      |

| -                         | Signal in GSM band 900 MHz<br>(824 MHz to 960 MHz)                            | @ Input signal<br>strength = -67 dBm | -    | -20   | -     | dBm  |

| -                         | Signal in GSM band 1800 MHz<br>(1805 MHz to 1990 MHz)                         | @ Input signal<br>strength = -67 dBm | -    | -14.5 | -     | dBm  |

| -                         | Signal in WCDMA band @ Input signal (2010 MHz to 2170 MHz) strength = -67 dBm |                                      | -    | -14   | -     | dBm  |

| Receiver inte             | rferer performance @ BER 0.1%                                                 | ,<br>,                               |      |       |       |      |

| C/I <sub>co-channel</sub> | Co-channel interference                                                       | @ Input signal<br>strength = -60 dBm | -    | 19    | 21    | dB   |

| C/I <sub>1MHz</sub>       | Adjacent (±1 MHz) interference                                                | @ Input signal<br>strength = -60 dBm | -    | -4    | 5     | dB   |

| C/I <sub>+2MHz</sub>      | Adjacent (+2 MHz) interference                                                | @ Input signal<br>strength = -60 dBm | -    | -37   | -25   | dB   |

| C/I <sub>-2MHz</sub>      | Adjacent (-2 MHz) interference                                                | @ Input signal<br>strength = -67 dBm | -    | -12   | 0     | dB   |

| C/I <sub>+3MHz</sub>      | Adjacent (+3 MHz) interference                                                | @ Input signal<br>strength = -67 dBm | -    | -46   | -33   | dB   |

| C/I <sub>-3MHz</sub>      | Adjacent (-3 MHz) interference                                                | @ Input signal<br>strength = -67 dBm | -    | -40   | -13   | dB   |

| C/I <sub>≥4MHz</sub>      | Adjacent (≥ ±4 MHz) interference                                              | @ Input signal<br>strength = -67 dBm | -    | -43   | -33   | dB   |

## 6.2 Transmitter

Unless otherwise stated, typical is defined at  $T_{amb}$  = 25 °C, BT\_HV = 2.75 V. Minimum and Maximum are worst cases over corner lots and temperature. Parameters are given at device pin, except for in-band spurious measured at antenna.

Table 18. Transmitter parameters

| Symbol                | Parameter                               | Test condition                                                            | Min.  | Тур.  | Max.  | Unit |

|-----------------------|-----------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|------|

| RFout                 | Output frequency range                  | -                                                                         | 2402  | -     | 2480  | MHz  |

| RF Transmit           | Power                                   |                                                                           | •     |       |       |      |

| TXpout<br>(GFSK)      | Maximum output power <sup>(1)</sup>     | @ 2402 - 2480 MHz<br>@ 25 °C                                              | 6     | 8     | 10    | dBm  |

| TXpout<br>(GFSK)      | Maximum output power <sup>(1)</sup>     | @ 2402 - 2480 MHz<br>@ worst cases over<br>corner lots and<br>temperature | 4.5   | 8     | 10.5  | dBm  |

| TXpout<br>(GFSK)      | Minimum output power                    | @ 2402 - 2480 MHz                                                         | -52.5 | -47.5 | -42.5 | dBm  |

| TXpout (π/4-DQPSK)    | Maximum output power <sup>(1) (2)</sup> | @ 2402 - 2480 MHz<br>@ 25 °C                                              | 3.5   | 6     | 8     | dBm  |

| TXpout (π/4-DQPSK)    | Minimum output power <sup>(2)</sup>     | @ 2402 - 2480 MHz                                                         | -43.5 | -38.5 | -33.5 | dBm  |

| TXpoutrel (π/4-DQPSK) | Relative transmit power (3)             | @ 2402 - 2480 MHz                                                         | -     | -0.2  | -     | dB   |

| TXpout<br>(8-DPSK)    | Maximum output power <sup>(1) (2)</sup> | @ 2402 - 2480 MHz<br>@ 25 °C                                              | 3.5   | 6     | 8     | dBm  |

| TXpout<br>(8-DPSK)    | Minimum output power <sup>(2)</sup>     | @ 2402 - 2480 MHz                                                         | -43.5 | -38.5 | -33.5 | dBm  |

| TXpoutrel<br>(8-DPSK) | Relative transmit power (3)             | @ 2402 - 2480 MHz                                                         | -     | -0.2  | -     | dB   |

| In-band spuri         | ious emission <sup>(4)</sup>            |                                                                           |       |       |       |      |

| FCC                   | FCC's 20 dB BW                          | -                                                                         | 900   | 930   | 950   | kHz  |

| ACP_2                 | Channel offset = ±2 MHz                 | -                                                                         | -     | -43.5 | -20   | dBm  |

| ACP_3                 | Channel offset = ±-3 MHz                | -                                                                         | -     | -52.5 | -40   | dBm  |

| ACP_4                 | Channel offset ≥ ±4 MHz                 | -                                                                         | -     | -54.5 | -40   | dBm  |

| EDR_IBS_1             | Channel offset = ±1 MHz (2 and 3 Mbps)  | -                                                                         | -     | -33.5 | -26   | dB   |

| EDR_IBS_2             | Channel offset = ±2 MHz (2 and 3 Mbps)  | -                                                                         | -     | -31.5 | -20   | dBm  |

| EDR_IBS_3             | Channel offset = ±3 MHz (2 and 3 Mbps)  | -                                                                         | -     | -45   | -40   | dBm  |

| EDR_IBS_4             | Channel offset = ±4 MHz (2 and 3 Mbps)  | -                                                                         | -     | -50   | -40   | dBm  |

Table 18. Transmitter parameters (continued)

| Table 10.                                                                   | Transmitter parameters (continued)         |                                      |      |      |       |        |  |