# MicroConverter, Dual 16-Bit ADCs with Embedded 62kB FLASH MCU

## **Preliminary Technical Data**

## ADuC846

#### FEATURES

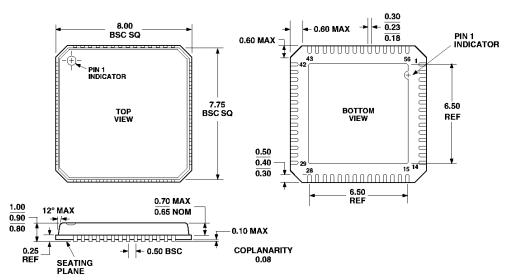

**High Resolution Sigma-Delta ADCs** Two Independent ADCs (16-Bit Resolution) 16-Bit No Missing Codes 16-Bit rms (16 Bit p-p) Effective Resolution @ 20 Hz Offset Drift 10 nV/°C, Gain Drift 0.5 ppm/°C Memorv 62 Kbytes On-Chip Flash/EE Program Memory 4 Kbytes On-Chip Flash/EE Data Memory Flash/EE, 100 Year Retention, 100 Kcycles Endurance 3 Levels of Flash/EE Program Memory Security In-Circuit Serial Download (No External Hardware) High Speed User Download (5 Seconds) 2304 Bytes On-Chip Data RAM 8051-Based Core 8051 Compatible Instruction Set High Performance Single Cycle Core 32 kHz External Crystal On-Chip Programmable PLL (12.58 MHz Max) 3 × 16-Bit Timer/Counter 26 Programmable I/O Lines 11 Interrupt Sources, Two Priority Levels Dual Data Pointer, Extended 11-Bit Stack Pointer **On-Chip Peripherals Internal Power on Reset Circuit** 12-Bit Voltage Output DAC Dual 16-Bit S-D DACs/PWMs **On-Chip Temperature Sensor Dual Excitation Current Sources** Time Interval Counter (Wakeup/RTC Timer) UART. SPI<sup>®</sup>, and I<sup>2</sup>C<sup>®</sup> Serial I/O High Speed Baud Rate Generator (incl 115,200) Watchdog Timer (WDT) Power Supply Monitor (PSM) Power Normal: 2.3mA Max @ 3.6 V (Core CLK = 1.57 MHz) Power-Down: 20µA Max with Wakeup Timer Running Specified for 3 V and 5 V Operation Package and Temperature Range 52-Lead MQFP (14 mm × 14 mm), -40°C to +125°C 56-Lead CSP (8 mm × 8 mm), -40°C to +85°C APPLICATIONS Intelligent Sensors WeighScales Portable Instrumentation, Battery Powered Systems 4-20mA Transmitters Data Logging **Precision System Monitoring**

#### REV. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

#### GENERAL DESCRIPTION

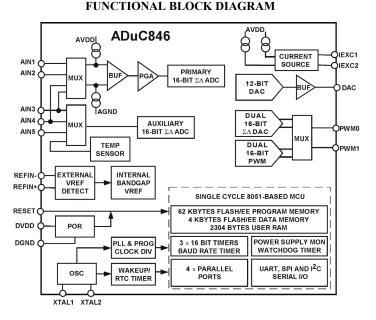

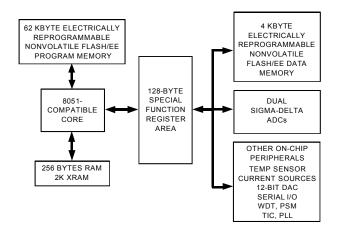

The ADuC846 is a complete smart transducer front end, integrating two high resolution sigma-delta ADCs, an 8-bit MCU, and program/data Flash/EE memory on a single chip.

The two independent ADCs (primary and auxiliary) include a temperature sensor and a PGA (allowing direct measurement of low level signals). The ADCs with on-chip digital filtering and programmable output data rates are intended for the measurement of wide dynamic range, low frequency signals, such as those in weigh scale, strain-gage, pressure transducer, or temperature measurement applications.

The device operates from a 32 kHz crystal with an on-chip PLL generating a high frequency clock of 12.58 MHz. This clock is routed through a programmable clock divider from which the MCU core clock operating frequency is generated. The microcontroller core is an optimized single cycle 8052 offering up to 12.58MIPs performance while maintaining the 8051 instruction set compatibility.

62 Kbytes of nonvolatile Flash/EE program memory, 4 Kbytes of nonvolatile Flash/EE data memory, and 2304 bytes of data RAM are provided on-chip. The program memory can be configured as data memory to give up to 60 Kbytes of NV data memory in data logging applications.

On-chip factory firmware supports in-circuit serial download and debug modes (via UART), as well as single-pin emulation mode via the EA pin. The ADuC846 is supported by a QuickStart<sup>™</sup> development system featuring low cost software and hardware development tools.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

## SPECIFICATIONS<sup>1</sup>

$\begin{array}{l} (AVDD = 2.7 \ V \ to \ 3.6 \ V \ or \ 4.75 \ V \ to \ 5.25 \ V, \ DVDD = 2.7 \ V \ to \ 3.6 \ V \ or \ 4.75 \ V \ to \ 5.25 \ V, \ REFIN(+) \\ = 2.5 \ V, \ REFIN(-) = \ AGND; \ AGND = \ DGND = 0 \ V; \ XTAL1/XTAL2 = \ 32.768 \ kHz \ Crystal; \ all \ specifications \ T_{MIN}, \ to \ T_{MAX} \ unless \ otherwise \ noted.). \end{array}$

| PRIMARY ADC<br>Conversion Rate<br>No Missing Codes <sup>2</sup><br>Resolution<br>Output Noise<br>Integral Non Linearity |                     | 19.79<br>13.5<br>16<br>ables X and | 105                | Hz<br>Bits<br>Bits Pk-Pk | On Both Channels<br>19.79Hz Update Rate                                |

|-------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------|--------------------|--------------------------|------------------------------------------------------------------------|

| No Missing Codes <sup>2</sup><br>Resolution<br>Output Noise<br>Integral Non Linearity                                   | 16<br>See Ta        | 13.5<br>16<br>ables X and          | 105                | Bits                     |                                                                        |

| Resolution<br>Output Noise<br>Integral Non Linearity                                                                    | See Ta              | 16<br>ables X and                  |                    |                          | 19.79Hz Update Rate                                                    |

| Resolution<br>Output Noise<br>Integral Non Linearity                                                                    |                     | 16<br>ables X and                  |                    |                          |                                                                        |

| Integral Non Linearity                                                                                                  |                     | ables X and                        |                    | DIIS PK-PK               | Range = $\pm 20$ mV, 20Hz Update Rate                                  |

| Integral Non Linearity                                                                                                  |                     |                                    |                    | Bits Pk-Pk               | Range = $\pm 2.56V$ , 20Hz Update Rate                                 |

| Integral Non Linearity                                                                                                  |                     |                                    | 1 XI in            |                          | Output Noise varies with selected Update Rates                         |

|                                                                                                                         |                     | C836 Data                          |                    |                          | and Gain Range                                                         |

|                                                                                                                         |                     |                                    | ±15                | ppm of FSR               | 1 LSB <sub>16</sub>                                                    |

| Offset Error <sup>3</sup>                                                                                               |                     | ± 3                                |                    | μV                       |                                                                        |

| Offset Error Drift (vs. Temp)                                                                                           |                     | $\pm 10$                           |                    | nV/°C                    |                                                                        |

| Full-Scale Error <sup>4</sup>                                                                                           |                     | $\pm 10$                           |                    | μν                       |                                                                        |

| Gain Error Drift <sup>5</sup> (vs. Temp)                                                                                |                     | $\pm 0.5$                          |                    | ppm/°C                   |                                                                        |

| ADC Range Matching                                                                                                      |                     | ± 0.5                              |                    | μV                       | AIN=18mV                                                               |

| Power Supply Rejection                                                                                                  | 80                  | 12                                 |                    | dBs                      |                                                                        |

| Power Suppry Rejection                                                                                                  | 80                  | 113                                |                    | dBs                      | AIN=1V, Range=± 2.56V<br>AIN=7.8mV, Range=± 20mV                       |

| Common Mode DC Rejection                                                                                                |                     | 115                                |                    | ubs                      | AIN-7.811V, Kange- $\pm 2011$ V                                        |

| Common Mode DC Rejection                                                                                                | 95                  |                                    |                    | dD -                     | ODC ADI-7.9mW Danas- 1.20mW                                            |

| On AIN<br>On AIN                                                                                                        | 95                  | 113                                |                    | dBs                      | <pre>@DC, AIN=7.8mV, Range=± 20mV<br/>@DC, AIN=1V, Range=± 2.56V</pre> |

| Common Mode 50/60Hz Rejection                                                                                           |                     | 113                                |                    | dBs                      | (a) DC, AIN=1V, Range=± 2.56V<br>20 Hz Update Rate                     |

| 5                                                                                                                       | 05                  |                                    |                    | dD -                     |                                                                        |

| On AIN                                                                                                                  | 95<br>00            |                                    |                    | dBs                      | $50/60$ Hz $\pm$ 1Hz, AIN=7.8mV, Range= $\pm$ 20mV                     |

| On AIN                                                                                                                  | 90                  |                                    |                    | dBs                      | $50/60$ Hz $\pm$ 1Hz, AIN=1V, Range= $\pm$ 2.56V                       |

| Normal Mode 50/60 Hz Rejection<br>On AIN                                                                                | 60                  |                                    |                    | dBs                      | 50/COLL + 111- 20 LL- Lundete Dete                                     |

| Oli Alin                                                                                                                | 00                  |                                    |                    | ubs                      | $50/60$ Hz $\pm$ 1Hz, 20 Hz Update Rate                                |

| PRIMARY ADC ANALOG INPUTS                                                                                               |                     |                                    |                    |                          |                                                                        |

| Differential Input Voltage Ranges <sup>9,10</sup>                                                                       |                     |                                    |                    |                          |                                                                        |

| Bipolar Mode (ADC0CON.5 = $0$ )                                                                                         | $\pm 1.0$           | 24 x V <sub>REF</sub> /G           | GAIN               | V                        | $V_{REF} = REFIN(+) - REFIN(-)$ (or Int 1.25V Ref)                     |

|                                                                                                                         |                     |                                    |                    |                          | GAIN = 1  to  128                                                      |

| Unipolar Mode (ADC0CON. $5 = 1$ )                                                                                       | $0 \rightarrow 1.0$ | 24 x REFI                          | N/GAIN             | V                        | $V_{REF} = REFIN(+) - REFIN(-)$                                        |

| 1                                                                                                                       |                     |                                    |                    |                          | GAIN=1 to 128                                                          |

| Analog Input Current <sup>2</sup>                                                                                       |                     |                                    | $\pm 1$            | nA                       | $T_{MAX} = 85^{\circ}C$                                                |

|                                                                                                                         |                     |                                    | ± 5                | nA                       | $T_{MAX} = 125^{\circ}C$                                               |

| Analog Input Current Drift                                                                                              |                     | ± 5                                |                    | pA/°C                    | $T_{MAX} = 85^{\circ}C$                                                |

|                                                                                                                         |                     | $\pm 15$                           |                    | pA/°C                    | $T_{MAX} = 125^{\circ}C$                                               |

| Absolute AIN Voltage Limits <sup>2</sup>                                                                                | $A_{GND} + 0$       | .1 AV                              | $V_{\rm DD} - 0.1$ | V                        | - MAA                                                                  |

| EXTERNAL REFERENCE INPUTS                                                                                               |                     |                                    |                    |                          |                                                                        |

| REFIN(+) to REFIN(-) Range <sup>2</sup>                                                                                 | 1                   | 2.5                                | $AV_{DD}$          | V                        |                                                                        |

| Average Reference Input Current                                                                                         |                     | +/- 1                              | 00                 | μA/V                     | Both ADCs Enabled                                                      |

| Average Reference Input Current Drift                                                                                   |                     | +/- 0.01                           |                    | nA/V/°C                  |                                                                        |

| 'NO Ext. REF' Trigger Voltage                                                                                           | 0.3                 |                                    | 0.65               | V                        | NOXREF bit active if VREF<0.3V                                         |

| i o Entrati i ingger voimge                                                                                             | 0.5                 |                                    | 0.00               | , ,                      | NOXREF bit Inactive if VREF>0.65                                       |

| Common Mode DC Rejection                                                                                                | 125                 |                                    |                    | dBs                      | $(a)DC, AIN=1V, Range=\pm 2.56V$                                       |

| Common Mode 50/60Hz Rejection                                                                                           | 90                  |                                    |                    | dBs                      | $50/60Hz \pm 1Hz$ , AIN=1V, Range= $\pm 2.56V$                         |

| Normal Mode 50/60 Hz Rejection                                                                                          | 60                  |                                    |                    | dBs                      | $50/60Hz \pm 1Hz$ , $741\sqrt{10}$ , $740/200$                         |

|                                                                                                                         |                     |                                    |                    |                          | · · · · ·                                                              |

| PARAMETER                                                                                                                                                                                                                                                                      | MIN                        | ТҮР                                                                                                     | MAX                  | UNITS                                                              | CONDITION                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| AUXILIARY ADC<br>No Missing Codes <sup>2</sup><br>Resolution<br>Output Noise                                                                                                                                                                                                   | 16<br>See Tab              | 16<br>ble XII in A<br>Datasheet                                                                         |                      | Bits<br>Bits Pk-Pk                                                 | 20 Hz Update Rate<br>Range = $\pm$ 2.5V, 20Hz Update Rate<br>Output Noise varies with selected Update Rates                             |

| Integral Non Linearity<br>Offset Error <sup>3</sup><br>Offset Error Drift<br>Fullscale Error <sup>4</sup><br>Gain Error Drift <sup>5</sup><br>Power Supply Rejection<br>Normal Mode 50/60 Hz Rejection<br>On AIN<br>On REFIN                                                   | 80<br>60<br>60             | Datasheet<br>-2<br>1<br>-2.5<br>$\pm 0.5$                                                               | ± 15                 | ppm of FSR<br>LSB<br>µV /°C<br>LSBs<br>ppm/°C<br>dBs<br>dBs<br>dBs | 1 LSB <sub>16</sub><br>AIN=1V, Range=± 2.56V<br>50/60Hz ± 1Hz, 19.79Hz Update Rate<br>50/60Hz ± 1Hz, 19.79Hz Update Rate                |

| AUXILIARY ADC ANALOG INPUTS<br>Differential Input Voltage Ranges <sup>9, 10</sup><br>(Bipolar Mode – ADC0CON3 = 0)<br>(Unipolar Mode – ADC0CON3 = 1)<br>Average Analog Input Current<br>Analog Input Current Drift<br>Absolute AIN Voltage Limits <sup>2, 11</sup>             | A <sub>GND</sub><br>- 0.03 | $\pm$ REFIN<br>0 → REFIN<br>125<br>$\pm 2$                                                              |                      | V<br>NA/V<br>pA/V/°C<br>V                                          | REFIN=REFIN(+)-REFIN(-) (or Int 1.25V Ref)<br>REFIN=REFIN(+)-REFIN(-) (or Int 1.25V Ref)                                                |

| ADC SYSTEM CALIBRATION<br>Full Scale Calibration Limit<br>Zero Scale Calibration Limit<br>Input Span                                                                                                                                                                           | -1.05 x F<br>0.8 x FS      | S                                                                                                       | .05 x FS<br>2.1 x FS | V<br>V<br>V                                                        |                                                                                                                                         |

| DAC<br>Voltage Range<br>Resistive Load<br>Capactive Load<br>Output Impedance<br>I <sub>SINK</sub>                                                                                                                                                                              |                            | $\begin{array}{c} 0 \rightarrow V_{REF} \\ 0 \rightarrow AV_{DE} \\ 10 \\ 100 \\ 0.5 \\ 50 \end{array}$ |                      | V<br>V<br>kΩ<br>pF<br>Ω<br>μΑ                                      | DACCON.2 = 0<br>DACCON.2 = 1<br>From DAC Output to AGND<br>From DAC Output to AGND                                                      |

| <ul> <li>DC Specifications<sup>7</sup><br/>Resolution<br/>Relative Accuracy<br/>Differential NonLinearity<br/>Offset Error<br/>Gain Error<sup>8</sup></li> <li>AC Specifications<sup>2,7</sup><br/>Voltage Output Settling Time<br/>Digital to Analog Glitch Energy</li> </ul> | 12                         | ± 3<br>± 1<br>15<br>10                                                                                  | -1<br>±50<br>±1      | LSBs<br>Bit<br>mV<br>%<br>%<br>us<br>nVs                           | Guaranteed 12-Bit Monotonic<br>$AV_{DD}$ Range<br>$V_{REF}$ Range<br>Setling time to 1LSB of final value<br>1 LSB change at major carry |

### PRELIMINARY TECHNICAL DATA ADuC846 SPECIFICATIONS<sup>1</sup>

#### ТҮР CONDITION PARAMETER MIN MAX UNITS INT REFERENCE ADC Reference 1.237 1.25 1.2625 V initial tolerance @ 25°C, VDD=5V Reference Voltage Power Supply Rejection 45 dBs Reference Tempco 100 ppm/°C DAC Reference Reference Voltage 2.475 V initial tolerance @ 25°C, VDD=5V 2.5 1.525 Power Supply Rejection 50 dBs Reference Tempco $\pm 100$ ppm/°C **TEMPERATURE SENSOR** Accuracy +/- 2 °C **MQFP** Package Thermal Impedance 90 °C/W 52 °C/W **CSP** Package TRANSDUCER BURNOUT CURRENT SOURCES AIN+ Current -100 AIN+ is the selected positive input to the nA primary ADC AIN- Current 100 AIN- is the selected negative input to the nA primary ADC Initial Tolerance at 25°C +/- 10 % 0.03 %/°C Drift **EXCITATION CURRENT SOURCES** Output Current -200 Available from each Current Source μΑ Initial Tolerance at 25°C +/-10 % 200 ppm/°C Drift Initial Current Matching at 25°C +/-1 % Matching between both Current Sources 20 ppm/°C Drift Matching AV<sub>DD</sub>=5V +/- 5% Line Regulation (AV<sub>DD</sub>) 1 μA/V Load Regulation 0.1 V **Output Compliance** A<sub>GND</sub> $AV_{DD}$ -0.6 V POWER SUPPLY MONITOR (PSM) AV<sub>DD</sub> Trip Point Selection Range 2.63 4.63 V Four Trip Points selectable in this range AV<sub>DD</sub> Trip Point Accuracy +/-3.0% $T_{MAX} = 85^{\circ}C$ $T_{MAX} = 125^{\circ}C$ AV<sub>DD</sub> Trip Point Accuracy +/- 3.0 % DV<sub>DD</sub> Trip Point Selection Range V Four Trip Points selectable in this range 2.63 4.63 DV<sub>DD</sub> Trip Point Accuracy % $T_{MAX} = \hat{8}5^{\circ}C$ +/-3.0DV<sub>DD</sub> Trip Point Accuracy +/- 3.0 % $T_{MAX} = 125^{\circ}C$ **CRYSTAL OSCILLATOR (XTAL 1AND XTAL2)** Logic Inputs, XTAL1 Only<sup>2</sup> V<sub>INL</sub>, Input Low Voltage 0.8 $DV_{DD} = 5V$ V $DV_{DD} = 3V$ 0.4 V $DV_{DD} = 5V$ 3.5 V V<sub>INH</sub>, Input Low Voltage V $DV_{DD} = 3V$ 2.5 pF XTAL1 Input Capacitance 18 XTAL2 Output Capacitance 18 pF

| PARAMETER                                                        | MIN  | ТҮР     | MAX    | UNITS    | CONDITION                                                |

|------------------------------------------------------------------|------|---------|--------|----------|----------------------------------------------------------|

| LOGIC INPUTS                                                     |      |         |        |          |                                                          |

| All Inputs except SCLOCK, RESET                                  |      |         |        |          |                                                          |

| and XTAL1 <sup>2</sup>                                           |      |         |        |          |                                                          |

| V <sub>INL</sub> , Input Low Voltage                             |      |         | 0.8    | V        | $DV_{DD} = 5V$                                           |

| <b>X7 T (T X7 1</b> )                                            | 2.0  |         | 0.4    | V        | $DV_{DD} = 3V$                                           |

| V <sub>INH</sub> , Input Low Voltage                             | 2.0  |         |        | V        |                                                          |

| SCLOCK and RESET Only<br>(Schmidt Triggered Inputs) <sup>2</sup> |      |         |        |          |                                                          |

| $V_{T+}$                                                         | 1.3  |         | 3.0    | V        | $DV_{DD} = 5V$                                           |

| • 1+                                                             | 0.95 |         | 2.5    | v        | $DV_{DD} = 3V$                                           |

| V <sub>T</sub> -                                                 | 0.8  |         | 1.4    | V        | $DV_{DD} = 5V$                                           |

| 1-                                                               | 0.4  |         | 1.1    | V        | $DV_{DD} = 3V$                                           |

| $V_{T+}$ - $V_{T-}$                                              | 0.3  |         | 0.85   | V        | $DV_{DD} = 5V \text{ or } 3V$                            |

| Input Currents                                                   | 2.0  |         |        | V        |                                                          |

| Port 0, P1.2 $\rightarrow$ P1.7, $\overline{EA}$                 | 2.0  |         | +/- 10 | ν<br>μA  | $V_{IN} = 0V$ or $V_{DD}$                                |

| SCLOCK, MOSI,MISO $\overline{SS}^{13}$                           | -10  |         | -40    | μΑ<br>μΑ | $V_{IN} = 0V, DV_{DD} = 5V,$ Internal Pullup             |

| belock, mosi, miso be                                            | 10   |         | +/-10  | μΑ       | $V_{IN} = DV_{DD}, DV_{DD}=5V$                           |

| RESET                                                            |      |         | +/-10  | μΑ       | $V_{IN} = 0V, DV_{DD} = 5V$                              |

| 10021                                                            | 35   |         | 105    | μΑ       | $V_{IN} = DV_{DD}$ , $DV_{DD} = 5V$ , Internal Pull-Down |

| P1.0, P1.1, Port 2, Port 3                                       | 50   |         | +/-10  | μΑ       | $V_{IN} = DV_{DD}, DV_{DD} = 5V$                         |

|                                                                  | -180 |         | -660   | μΑ       | $V_{IN} = 2V, DV_{DD} = 5V$                              |

|                                                                  | -20  |         | -75    | μΑ       | $V_{IN} = 0.45V, DV_{DD} = 5V$                           |

| Input Capacitance                                                |      | 5       |        | pF       | All Digital Inputs                                       |

| LOGIC OUTPUTS                                                    |      |         |        |          |                                                          |

| All Digital Outputs except XTAL2 <sup>2</sup>                    |      |         |        |          |                                                          |

| V <sub>OH</sub> , Output High Voltage                            | 2.4  |         |        | V        | $DV_{DD} = 5V, I_{SOURCE} = 80 \ \mu A$                  |

|                                                                  | 2.4  |         |        | V        | $DV_{DD} = 3V, I_{SOURCE} = 20 \ \mu A$                  |

| V <sub>OL</sub> , Output Low Voltage <sup>14</sup>               |      |         | 0.8    | V        | $I_{SINK} = 8mA$ , SCLOCK, MOSI/SDATA                    |

|                                                                  |      |         | 0.8    | V        | $I_{SINK} = 10mA, P1.0, P1.1$                            |

| Electine State Lechene Comment                                   |      |         | 0.8    | V        | $I_{SINK} = 1.6 \text{mA}$ , All Other Outputs           |

| Floating State Leakage Current                                   |      | 5       | +/-10  | μA<br>nE |                                                          |

| Floating State Output Capacitance                                |      | 5       |        | pF       |                                                          |

| START UP TIME                                                    |      |         |        |          |                                                          |

| At Power On                                                      |      | 300     |        | ms       |                                                          |

| After External RESET in Normal Mode                              |      | 3       |        | ms       |                                                          |

| After WDT RESET in Normal Mode                                   |      | 3       |        | ms       | Controlled via WDCON SFR                                 |

| From Idle Mode                                                   |      | 10      |        | us       |                                                          |

| From Power-Down Mode                                             |      |         |        |          |                                                          |

| Oscillator Running                                               |      | •       |        |          | PLLCON.7 = 0                                             |

| Wakeup with INTO Interrupt                                       |      | 20      |        | us       |                                                          |

| Wakeup with SPI Interrupt                                        |      | 20      |        | us       |                                                          |

| Wakeup with TIC Interrupt<br>Wakeup with External RESET          |      | 20<br>3 |        | us       |                                                          |

| Oscillator Powered Down                                          |      | 3       |        | us       | PLLCON.7 = 1                                             |

| Wakeup with INTO Interrupt                                       |      | 20      |        | us       | 1 LLCON, I = 1                                           |

| Wakeup with SPI Interrupt                                        |      | 20      |        | us       |                                                          |

| Wakeup with External RESET                                       |      | 5       |        | ms       |                                                          |

| makeup mai External RESET                                        |      | 5       |        | 1115     |                                                          |

### PRELIMINARY TECHNICAL DATA ADuC846 SPECIFICATIONS<sup>1</sup>

| PARAMETER                                                    | MIN       | ТҮР     | MAX       | UNITS    | CONDITION                                                               |

|--------------------------------------------------------------|-----------|---------|-----------|----------|-------------------------------------------------------------------------|

| FLAH/EE MEMORY RELIABILITY CI                                | HARACTE   | RISTICS |           |          |                                                                         |

| Endurance <sup>16</sup>                                      | 100,000   | 700,000 |           | Cycles   |                                                                         |

| Data Retention <sup>17</sup>                                 | 100       |         |           | 2        |                                                                         |

| DOWED DECLUDEMENTS                                           |           |         |           |          |                                                                         |

| POWER REQUIREMENTS<br>Power Supply Voltages                  |           |         |           |          |                                                                         |

| $AV_{DD}$ 3V Nominal                                         | 2.7       |         | 3.6       | V        |                                                                         |

| $AV_{DD}$ 5V Nominal                                         | 4.75      |         | 5.25      | v<br>V   |                                                                         |

| $DV_{DD}$ 3V Nominal                                         | 2.7       |         | 3.6       | vV       |                                                                         |

| $DV_{DD}$ 5V Nominal                                         | 4.75      |         | 5.25      | v        |                                                                         |

|                                                              |           |         |           |          |                                                                         |

| 5V POWER CONSUMPTION<br>Normal Mode <sup>18, 19</sup>        |           |         |           |          | 4.75V < DVDD <5.25V, AVDD= 5.25V                                        |

| DV <sub>DD</sub> Current                                     |           |         | 4         | mA       | core clock = 1.57 MHz                                                   |

|                                                              |           | 13      | 16        | mA       | core clock = 12.58MHz                                                   |

| AV <sub>DD</sub> Current                                     |           |         | 180       | μA       |                                                                         |

| Power-Down Mode <sup>18, 19</sup>                            |           |         |           | •        |                                                                         |

| DV <sub>DD</sub> Current                                     |           |         | 53        | μA       | $T_{MAX} = 85^{\circ}C$ ; Osc ON;TIC ON                                 |

|                                                              |           |         | 100       | μΑ       | $T_{MAX} = 125$ °C; Osc ON; TIC ON                                      |

| DV <sub>DD</sub> Current                                     |           |         | 30        | μA       | $T_{MAX} = 85^{\circ}C; Osc OFF$                                        |

|                                                              |           |         | 80        | μA       | $T_{MAX} = 125^{\circ}C$ ; Osc OFF                                      |

| AV <sub>DD</sub> Current                                     |           |         | 1         | μA       | $T_{MAX} = 85^{\circ}C$ ; Osc ON or OFF                                 |

|                                                              |           |         | 3         | μA       | $T_{MAX} = 125^{\circ}C$ ; Osc ON or OFF                                |

| Typical Additional Peripheral Currents (AI <sub>r</sub>      | and D Ipp | )       | 5         | μ        |                                                                         |

| Primary ADC                                                  |           | , 1     |           | mA       |                                                                         |

| Auxiliary ADC                                                |           | 0.5     |           | mA       |                                                                         |

| Power Supply Monitor                                         |           | 50      |           | μA       |                                                                         |

| DAC                                                          |           | 150     |           | μA       |                                                                         |

| Dual Excitation Current Sources                              |           | 400     |           | μΑ       |                                                                         |

|                                                              |           |         |           |          |                                                                         |

| <b>3V POWER CONSUMPTION</b><br>Normal Mode <sup>18, 19</sup> |           |         |           |          | 4.75V < DVDD <5.25V, AVDD= 5.25V                                        |

| $DV_{DD}$ Current                                            |           |         | 2.3       | mA       | core clock = 1.57 MHz                                                   |

| Dv <sub>DD</sub> Current                                     |           | 8       | 2.3<br>10 | mA<br>mA | core clock = 12.58 MHz                                                  |

| AV <sub>DD</sub> Current                                     |           | 0       | 180       |          |                                                                         |

| Power-Down Mode <sup>18, 19</sup>                            |           |         | 100       | μΑ       |                                                                         |

| $DV_{DD}$ Current                                            |           |         | 20        |          | $T_{MAX} = 85^{\circ}C$ ; Osc ON;TIC ON                                 |

| D v DD Current                                               |           |         | 20<br>40  | μΑ       | $T_{MAX} = 85$ °C; Osc ON; TIC ON<br>$T_{MAX} = 125$ °C; Osc ON; TIC ON |

| DV Current                                                   |           | 10      | 40        | μA       | $I_{MAX} = 125$ °C; OSC ON; TIC ON<br>Osc OFF                           |

| DV <sub>DD</sub> Current                                     |           | 10      | 80        | μA       |                                                                         |

|                                                              |           |         | 80        | μA       | $T_{MAX} = 125^{\circ}C; Osc OFF$                                       |

| AV <sub>DD</sub> Current                                     |           |         | 1         | μA       | $T_{MAX} = 85^{\circ}C; Osc ON or OFF$                                  |

|                                                              |           |         | 3         | μΑ       | $T_{MAX} = 125^{\circ}C$ ; Osc ON or OFF                                |

### ADuC846

#### NOTES

- Temperature Range for ADuC844BS (MQFP package) is -40°C to +125°C. Temperature Range for ADuC844BCP (CSP package) is -40°C to +85°C.

- 2 These numbers are not production tested but are guaranteed by design and/or characterization data on production release.

- 3 System Zero-Scale Calibration can remove this error.

- 4 The primary ADC is factory calibrated at 25°C with AVDD = DVDD = 5 V yielding this full-scale error of 10  $\mu$ V. If user power supply or temperature conditions are significantly different from these, an Internal Full-Scale Calibration will restore this error to 10  $\mu$ V. A system zero-scale and full-scale calibration will remove this error altogether.

- 5 Gain Error Drift is a span drift. To calculate Full-Scale Error Drift, add the Offset Error Drift to the Gain Error Drift times the full-scale input.

- 6 The auxiliary ADC is factory calibrated at  $25^{\circ}$ C with AVDD = DVDD = 5 V yielding this full-scale error of -2.5 LSB. A system zero-scale and full-scale calibration will remove this error altogether.

- 7 DAC linearity and ac specifications are calculated using: reduced code range of 48 to 4095, 0 to VREF, reduced code range of 100 to 3950, 0 to VDD.

- 8 Gain Error is a measure of the span error of the DAC.

- 9 In general terms, the bipolar input voltage range to the primary ADC is given by RangeADC = ±(VREF 2<sup>RN</sup>)/125, where: VREF = REFIN(+) to REFIN(-) voltage and VREF = 1.25 V when internal ADC VREF is selected. RN = decimal equivalent of RN2, RN1, RN0 e.g., VREF = 2.5 V and RN2, RN1, RN0 = 1, 1, 0 the RangeADC = ±1.28 V, In unipolar mode, the effective range is 0 V to 1.28 V in our example.

- 10 1.25 V is used as the reference voltage to the ADC when internal VREF is selected via XREF0 and XREF1 bits in ADC0CON and ADC1CON, respectively.

- 11 In bipolar mode, the Auxiliary ADC can only be driven to a minimum of AGND 30 mV as indicated by the Auxiliary ADC absolute AIN voltage limits. The bipolar range is still –VREF to +VREF; however, the negative voltage is limited to –30 mV.

- 12 The ADuC846BCP (CSP Package) has been qualified and tested with the base of the CSP Package floating.

- 13 Pins configured in SPI Mode, pins configured as digital inputs during this test.

- 14 Pins configured in I<sup>2</sup>C Mode only.

- 15 Flash/EE Memory Reliability Characteristics apply to both the Flash/EE program memory and Flash/EE data memory.

- 16 Endurance is qualified to 100 Keyeles as per JEDEC Std. 22 method A117 and measured at -40 °C, +25°C, +85°C, and +125°C. Typical endurance at 25°C is 700 Keyeles.

- 17 Retention lifetime equivalent at junction temperature (TJ) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6eV will derate with junction temperature.

- 18 Power Supply current consumption is measured in Normal, Idle, and Power-Down Modes under the following conditions: Normal Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, Core Executing internal software loop. Idle Mode: Reset = 0.4 V, Digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON, PCON.0 = 1, Core Execution suspended in idle mode. Power-Down Mode: Reset = 0.4 V, All P0 pins and P1.2–P1.7 Pins = 0.4 V, All other digital I/O pins are open circuit, Core Clk changed via CD bits in PLLCON, PCON.1 = 1, Core Execution suspended in power-down mode, OSC turned ON or OFF via OSC\_PD bit (PLLCON.7) in PLLCON SFR.

- 19 DVDD power supply current will increase typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

Specifications subject to change without notice

## ADuC846

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| -0.3 V to +7 V                      |

|-------------------------------------|

| –0.3 V to +7 V                      |

| –0.3 V to +7 V                      |

| -0.3 V to +7 V                      |

| -0.3 V to +0.3 V                    |

| -2 V to +5 V                        |

| -0.3 V to AV <sub>DD</sub> $+0.3$ V |

| –0.3 V to AV <sub>DD</sub> +0.3 V   |

| 30 mA                               |

| -0.3 V to DV <sub>DD</sub> $+0.3$ V |

| -0.3 V to DV <sub>DD</sub> $+0.3$ V |

| -40°C to +125°C                     |

| -65°C to +150°C                     |

| 150°C                               |

| 90°C/W                              |

|                                     |

| 215°C                               |

| 220°C                               |

|                                     |

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>AGND and DGND are shorted internally on the ADuC846.

<sup>3</sup>Applies to P1.2 to P1.7 pins operating in analog or digital input modes.

#### **ORDERING GUIDE**

| MODEL           | Temperature<br>Range (°C) | Voltage Range<br>(V) | User Code<br>Space | Package Description                | Package<br>Option |

|-----------------|---------------------------|----------------------|--------------------|------------------------------------|-------------------|

| ADuC846BS62-5   | -40 <b>→</b> +125         | 4.75 → 5.25          | 62 kBytes          | 52-Lead Plastic Quad Flatpack      | S-52              |

| ADuC846BS62-3   | -40 <b>→</b> +125         | 2.75 <b>→</b> 3.60   | 62 kBytes          | 52-Lead Plastic Quad Flatpack      | S-52              |

| ADuC846BCP62-5  | -40 <b>→</b> +85          | 4.75 → 5.25          | 62 kBytes          | 56-Lead Chip Scale Package         | CP-56             |

| ADuC846BCP62-3  | -40 <b>→</b> +85          | 2.75 <b>→</b> 3.60   | 62 kBytes          | 56-Lead Chip Scale Package         | CP-56             |

| ADuC846BCP32-5  | -40 <b>→</b> +85          | 4.75 <b>→</b> 5.25   | 32 kBytes          | 56-Lead Chip Scale Package         | CP-56             |

| ADuC846BCP32-3  | -40 <b>→</b> +85          | 2.75 <b>→</b> 3.60   | 32 kBytes          | 56-Lead Chip Scale Package         | CP-56             |

| ADuC846BCP8-5   | -40 <b>→</b> +85          | 4.75 <b>→</b> 5.25   | 8 kBytes           | 56-Lead Chip Scale Package         | CP-56             |

| ADuC846BCP8-3   | -40 <b>→</b> +85          | 2.75 <b>→</b> 3.60   | 8 kBytes           | 56-Lead Chip Scale Package         | CP-56             |

| EVAL-ADuC846QS  |                           |                      |                    | QuickStart Development System      |                   |

| EVAL-ADuC846QSP |                           |                      |                    | QuickStart Plus Development System |                   |

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADuC846 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

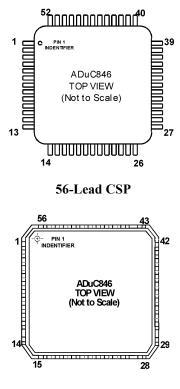

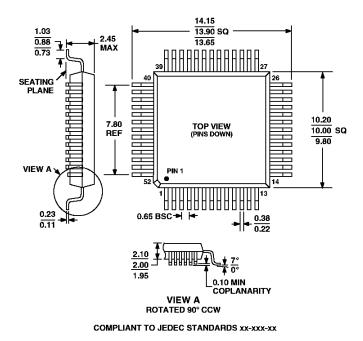

#### PIN CONFIGURATION

#### 52-Lead MQFP

### ADuC846

#### PIN FUNCTION DESCRIPTIONS

| Pin No:                               | Pin No:                                                             | Pin             | Type* | Description                                                                                                                                                                                                                                                                            |

|---------------------------------------|---------------------------------------------------------------------|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP                               | 56-CSP                                                              | Mnemonic        |       |                                                                                                                                                                                                                                                                                        |

| 1, 2                                  | 56, 1                                                               | P1.0/P1.1       | I/O   | P1.0 and P1.1 can function as a digital inputs or digital outputs and have a pull-<br>up configuration as described below for Port 3. P1.0 and P1.1 have an increased<br>current drive sink capability of 10mA.                                                                        |

|                                       |                                                                     | P1.0/T2/PWM0    | I/O   | P1.0 and P1.1 also have various secondary functions as described below.<br>P1.0 can also be used to provide a clock input to Timer 2. When enabled, counter 2 is incremented in response to a negative transition on the T2 input pin.                                                 |

|                                       |                                                                     | P1.1/T2EX/PWM1  | I/O   | If the PWM is enabled, the PWM0 output will appear at this pin.<br>P1.1 can also be used to provide a control input to Timer 2. When enabled, a<br>negative transition on the T2EX input pin will cause a Timer 2 capture or reload<br>event.                                          |

| $3 \rightarrow 4 \\ 9 \rightarrow 12$ | $\begin{array}{c} 2 \rightarrow 3 \\ 11 \rightarrow 14 \end{array}$ | P1.2 →P1.7      | Ι     | If the PWM is enabled, the PWM1 output will appear at this pin.<br>Port 1.2 to Port 1.7 have no digital output driver; they can function as a digital<br>input for which '0' must be written to the port bit. As a digital input, these pins<br>must be driven high or low externally. |

|                                       |                                                                     | P1.2/DAC/IEXC1  | I/O   | These pins also have the following analog functionality:<br>The voltage output from the DAC or one or both current sources (200uA or 2 x 200uA) can be configured to appear at this pin.                                                                                               |

|                                       |                                                                     | P1.3/AIN5/IEXC2 | I/O   | Auxiliary ADC Input or one or both current sources can be configured at this pin.                                                                                                                                                                                                      |

|                                       |                                                                     | P1.4/AIN1       | Ι     | Primary ADC, Positive Analog Input                                                                                                                                                                                                                                                     |

|                                       |                                                                     | P1.5/AIN2       | Ι     | Primary ADC, Negative Analog Input                                                                                                                                                                                                                                                     |

|                                       |                                                                     | P1.6/AIN3       | Ι     | Auxiliary ADC Input or Muxed Primary ADC, Positive Analog Input                                                                                                                                                                                                                        |

|                                       |                                                                     | P1.7/AIN4/DAC   | I/O   | Auxiliary ADC Input or Muxed Primary ADC, Negative Analog Input. The voltage                                                                                                                                                                                                           |

| 5                                     | 4                                                                   | AVDD            | S     | Analog Supply Voltage                                                                                                                                                                                                                                                                  |

| 6                                     | 5                                                                   | AGND            | S     | Analog Ground.                                                                                                                                                                                                                                                                         |

| N/C                                   | 6                                                                   | AGND            | S     | A second Analog ground is provided with the CSP version only.                                                                                                                                                                                                                          |

| 7                                     | 7                                                                   | REFIN-          | Ι     | External Reference Input, negative terminal                                                                                                                                                                                                                                            |

| 8                                     | 8                                                                   | <b>REFIN+</b>   | Ι     | External Reference Input, positive terminal                                                                                                                                                                                                                                            |

| 13                                    | 15                                                                  | $\overline{SS}$ | Ι     | The slave select input for the SPI Interface is present at this pin. A weak pull-up is present on this pin.                                                                                                                                                                            |

| 14                                    | 16                                                                  | MISO            | Ι     | Master Input/Slave Output for the SPI Interface. There is a weak pull-up on this                                                                                                                                                                                                       |

| 15                                    | 17                                                                  | RESET           | Ι     | input pin.<br>Reset Input. A high level on this pin for 16 core clock cycles while the<br>oscillator is running resets the device. There is an internal weak pull-down and<br>a Schmitt trigger input stage on this pin.                                                               |

| Pin No:                                 | Pin No:                                 | Pin            | Type*  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------|-----------------------------------------|----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP                                 | 56-CSP                                  | Mnemonic       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16-19<br>22-25                          | 18-21<br>24-27                          | P3.0 → P3.7    | I/O    | P3.0–P3.7 are bi-directional port pins with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low will source current because of the internal pull-up resistors. When driving a 0-to-1 output transition, a strong pull-up is active for two core clock periods of the instruction cycle. Port 3 pins also have various secondary functions described below.                                                                                                                                                             |

| 16                                      | 18                                      | P3.0/RXD       |        | Receiver Data for UART serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17                                      | 19                                      | P3.1/TXD       |        | Transmitter Data for UART serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 18                                      | 20                                      | P3.2/INT0      |        | External Interrupt 0. This pin can also be used as a gate control input to Timer0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19                                      | 21                                      | P3.3/INT1      |        | External Interrupt 1. This pin can also be used as a gate control input to Timer1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 22                                      | 24                                      | P3.4/T0/PWMCLK |        | Timer/Counter 0 External Input<br>If the PWM is enabled, an external clock may be input at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 23                                      | 25                                      | P3.5/T1        |        | Timer/Counter 1 External Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 24                                      | 26                                      | P3.6/WR        |        | External Data Memory Write Strobe. Latches the data byte from Port 0 into an external data memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 25                                      | 27                                      | P3.7/RD        |        | External Data Memory Read Strobe. Enables the data from an external data memory to Port 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20, 34, 48<br>21, 35, 47                | 22, 36, 51<br>23, 37, 50                | DVDD<br>DGND   | S<br>S | Digital Supply Voltage<br>Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 26                                      | 28                                      | SCLOCK         | I/O    | Serial interface clock for either the I <sup>2</sup> C or SPI interface. As an input, this pin is a Schmitt-triggered input and a weak internal pull-up is present on this pin unless it is outputting logic low. This pin can also be directly controlled in software as a digital output pin.                                                                                                                                                                                                                                                                                                                                                                                        |

| 27                                      | 29                                      | MOSI/SDATA     | I/O    | Serial Data I/O for the I <sup>2</sup> C Interface or Master Output/Slave Input for the SPI Interface. A weak internal pull-up is present on this pin unless it is outputting logic low. This pin can also be directly controlled in software as a digital output pin.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $28 \rightarrow 31$ $36 \rightarrow 39$ | $30 \rightarrow 32$ $38 \rightarrow 42$ | P2.0 → P2.7    | I/O    | Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that<br>have 1s written to them are pulled high by the internal pull-up resistors, and in<br>that state can be used as inputs. As inputs, Port 2 pins being pulled externally<br>low will source current because of the internal pull-up resistors.<br>Port 2 emits the high order address bytes during fetches from external<br>program memory and middle and high order address bytes during accesses to<br>the 24-bit external data memory space.                                                                                                                                                       |

| 32                                      | 34                                      | XTAL1          | Ι      | Input to the crystal oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 33                                      | 35                                      | XTAL2          | 0      | Output from the crystal oscillator inverter. (see "Hardware Design Considerations" for description)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 40                                      | 43                                      | ĒĀ             |        | External Access Enable, Logic Input. When held high, this input enables the device to fetch code from internal program memory locations 0000h to F7FFh. When held low this input enables the device to fetch all instructions from external program memory. To determine the mode of code execution, i.e., internal or external, the $\overline{EA}$ pin is sampled at the end of an external RESET assertion or as part of a device power cycle. $\overline{EA}$ may also be used as an external emulation I/O pin and therefore the voltage level at this pin must not be changed during normal mode operation as it may cause an emulation interrupt that will halt code execution. |

## ADuC846

| Pin No:                                                               | Pin No:                                                               | Pin         | Type* | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52-MQFP                                                               | 56-CSP                                                                | Mnemonic    |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 41                                                                    | 44                                                                    | PSEN        |       | Program Store Enable, Logic Output. This output is a control signal that<br>enables the external program memory to the bus during external fetch<br>operations. It is active every six oscillator periods except during external data<br>memory accesses. This pin remains high during internal program execution.<br>PSEN can also be used to enable serial download mode when pulled low<br>through a resistor at the end of an external RESET assertion or as part of a<br>device power cycle.      |

| 42                                                                    | 45                                                                    | ALE         |       | Address Latch Enable, Logic Output. This output is used to latch the low byte (and page byte for 24-bit data address space accesses) of the address to external memory during external code or data memory access cycles. It is activated every six oscillator periods except during an external data memory access. It can be disabled by setting the PCON.4 bit in the PCON SFR.                                                                                                                     |

| $\begin{array}{c} 43 \rightarrow 46 \\ 49 \rightarrow 52 \end{array}$ | $\begin{array}{c} 46 \rightarrow 49 \\ 52 \rightarrow 55 \end{array}$ | P0.0 → P0.7 | I/O   | P0.0–P0.7, these pins are part of Port0 which is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have 1s written to them float and in that state can be used as high impedance inputs. An external pull-up resistor will be required on P0 outputs to force a valid logic high level externally. Port 0 is also the multiplexed low-order address and data bus during accesses to external program or data memory. In this application it uses strong internal pull-ups when emitting 1s. |

\*I = Input, O = Output, S = Supply.

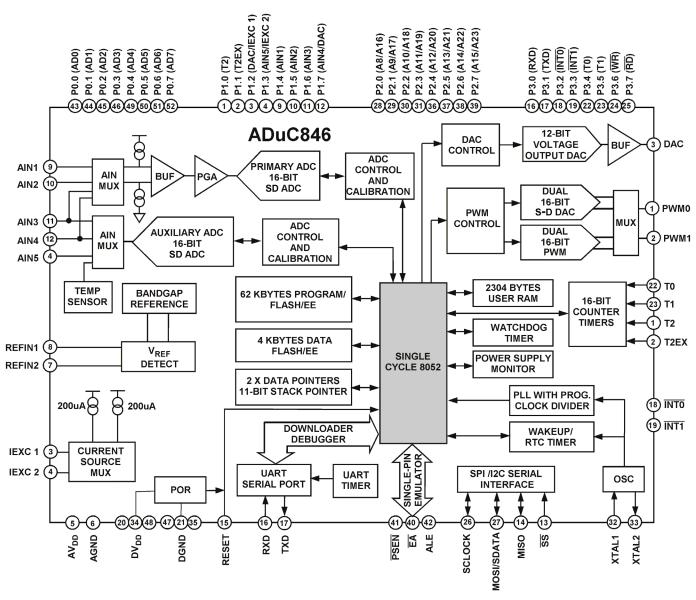

#### DETAILED BLOCK DIAGRAM WITH PIN NUMBERS

PIN NUMBERS REFER TO THE 52 PIN MQFP PACKAGE\*

Figure 1: Detailed Block Diagram of the ADuC846

## ADuC846

#### INTRODUCTION

The ADuC846 is a pin compatible upgrade to the ADuC836 and provides increased core performance. The ADUC846 has a single cycle 8052 core allowing operation at up to 12.58MIPs. It has all the same features as the ADuC836 but the standard 12-cycle 8052 core has been replaced with a 12.6MIPs single cycle core.

Since the ADuC846 and ADuC836 share the same feature set only the differences between the two chips are documented here. For full documentation on the ADuC836 please consult the datasheet available at http://www.analog.com/microconverter

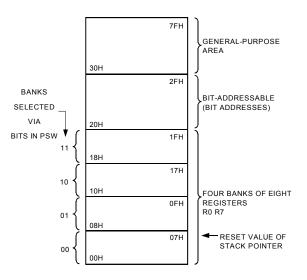

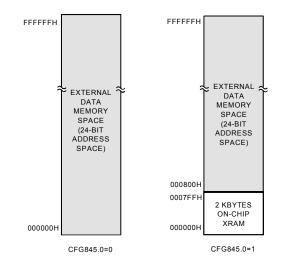

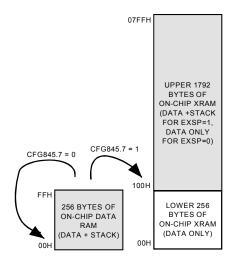

#### **MEMORY7 ORGANISATION**

The ADuC846 contains 4 different memory blocks namely:

- 62kBytes of On-Chip Flash/EE Program Memory

- 4kBytes of On-Chip Flash/EE Data Memory

- 256 Bytes of General Purpose RAM

- 2kBytes of Internal XRAM

#### (1) Flash/EE Program Memory

The ADuC846 provides 62kBytes of Flash/EE program memory to run user code. The user can choose to run code from this internal memory or run code from an external program memory. If the user applies power or resets the device while the  $\overline{EA}$  pin is pulled low externally, the part will execute code from the external program space, otherwise if  $\overline{EA}$  is pulled high externally the part defaults to code execution from its internal 62kBytes of Flash/EE program memory. The ADuC846 does not support the rollover from F7FFh in internal code space to F800h in external code space. Instead the 2048 bytes between F800h and FFFFh will appear as NOP instructions to user code.

Permanently embedded firmware allows code to be serially downloaded to the 62kBytes of internal code space via the UART serial port while the device is in-circuit. No external hardware is required.