# Am2085 ISDN Subscriber Access Controller (ISAC-S)

#### DISTINCTIVE CHARACTERISTICS

- S-Bus transceiver according to CCITT I.430

- Recovery of clock and frame

- Frame alignment for trunk line termination

- Access to Echo bit

- Implementation of activation/deactivation procedure according to CCITT I.430

- Support of LAPD protocol

- FIFO buffer (2 × 64 byte) for efficient transfer of D-channel packets

- Serial interfaces for various types of B-channel sources/destinations (SLD, SSI)

- Switching functions for B-channels

- Watchdog timer

- Switching of test loops

- 8-bit microprocessor interface

- Advanced CMOS technology

- Low power consumption

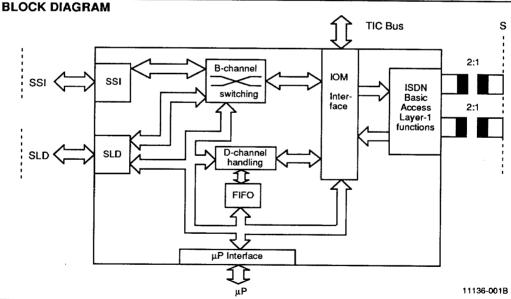

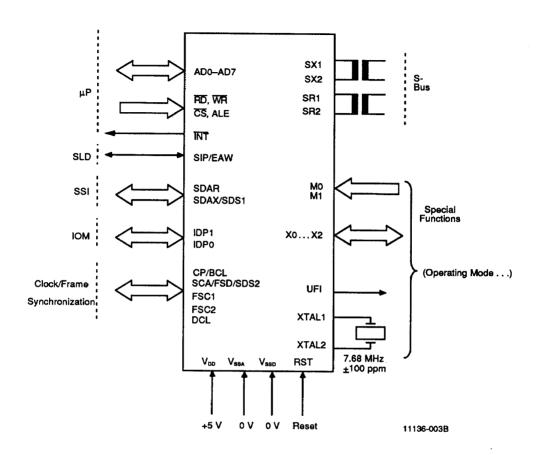

# **GENERAL DESCRIPTION**

The Am2085 ISAC-S™ is a transceiver circuit able to interface voice/data communication equipment to the four-wire CCITT S-bus. It supports the LAPD protocol in hardware. For an efficient transfer of D-channel packets, FIFO structures are used.

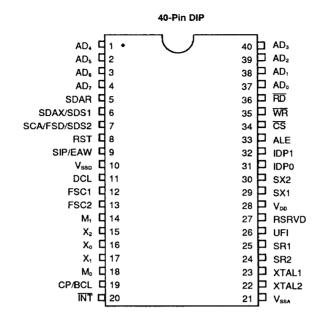

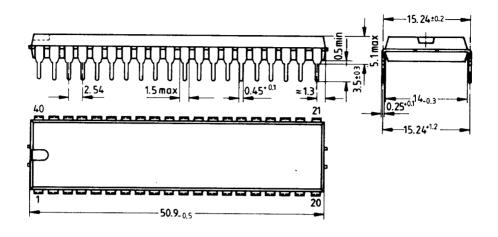

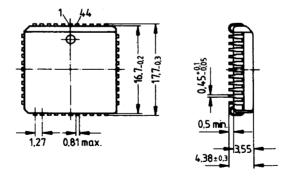

The device is mounted in a 40-pin CMOS package.

The power consumption of the device in the active state is 80 mW (8 mW in Power Down State).

Publication # Rev. Amendment 11136 C / & /1 Issue Date: July 1989

1-135

# CONNECTION DIAGRAMS Top View

11136-002B

#### 44-Pin PLCC 3 2 43 42 41 40 39 RD(DS) SDAX/SDS1 38 WR(R/W) SCA/FSD/SDS2 9 37 T CS RST [ 36 ALE SIP/EAW/A5 11 ☐ IDP1 V<sub>ssp</sub> L 12 DCL IDPo 33 FSC1 13 ☐ SX2 FSC2 14 32 SX1 15 31 Jv∞ м, С 16 X2 [ RSRVD 29 ] UFI A, [ X, [ X, [ M, [ CP/BCL [ INT [ Vss. [ XTAL2 XTAL1 SR2 Note: Pin 1 is marked for orientation.

1-136 Am2085

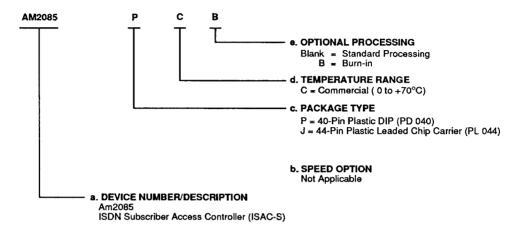

### ORDERING INFORMATION

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The ordering number (Valid Combination) is formed by a combination of:

a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

| Vaild Comb | oinations        |

|------------|------------------|

| AM2085     | PC, JC, PCB, JCB |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

1-138 Am2085

#### PIN DESCRIPTION

#### ADo-AD7

#### Address Bus (input)

The multiplexed Address/Data Bus transfers data and commands between the microprocessor System and the ISAC-S.

#### ALE

#### Address Latch Enable (Input)

A High on this line indicates an address on the external address/data bus, selecting one of the ISAC-S internal sources or destinations.

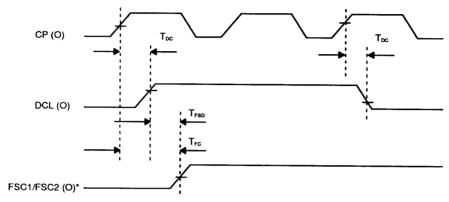

#### CP

#### (Output)

Synchronized clock output.

## $\overline{\mathsf{cs}}$

## Chip Select (Input; Active Low)

A Low on this line selects the ISAC-S for a read/write operation.

#### DCL

#### Clock (Input/Output)

This pin supplies the device clock.

## FSC<sub>1</sub>

## Frame Sync 1 (Input/Output)

Supplies the synchronization signal 1: input (LT-S/NT) or output (TE/LT-S).

#### FSC<sub>2</sub>

#### Frame Sync 2 (Input/Output)

Supplies the synchronization signal 2: input (LT-S/NT) or output (TE/LT-T).

#### INT

## Interrupt (Output; Active Low)

The signal is activated when the ISAC-S requests an interrupt. It is an open-drain output.

#### M<sub>1</sub>, M<sub>0</sub>

(Input)

Setting of operating mode.

#### RD

#### Read (Input: Active Low)

This signal indicates a read operation.

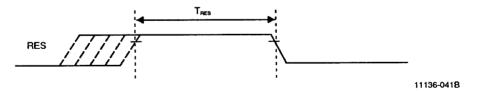

#### RST

## Reset (input; Acitve High)

A High on this input focus forces the ISAC-S into reset state.

#### SCA/FSD

#### Serial Clock Port A/Frame Sync. Delayed (Output)

Depending on the programmed timing mode, this output supports either a 128-kHz clock signal for the SSI port or a delayed 8-kHz frame synchronization signal for IOM interface.

#### SDAR

#### Serial Data Port A Receive (SSI) (Input)

This line receives serial data at standard TTL or CMOS levels. An integrated pull-up circuit enables connection of an open-drain/open-collector driver without an external pull-up resistor.

#### SDAX

## Serial Data Port A Transmit (SSI) (Output)

This line transmits serial data at standard TTL or CMOS levels.

#### SDI

#### (Input/Output)

Serial Data In, IOM interface.

# SDO

(Output)

Serial Data Out, IOM interface.

#### SIP/EAW

#### SLD Interface Port (Input/Output)

This line transmits and receives serial data at standard TTL or CMOS levels. When the terminal-specific functions are selected, this line serves as the subscriber awake line.

#### SR<sub>1</sub>

#### (Output)

S-bus receiver, 2.5 V reference output.

#### SR<sub>2</sub>

(Input)

S-bus receiver, signal input.

#### SX1

#### (Output)

Positive output S-bus transmitter.

#### SX2

(Output)

Negative output S-bus transmitter.

Am2085 1-139

UFI

(Output)

Connection for an optional external RC circuit.

$V_{DD}$

Power supply (+5 V ±5%).

$V_{\text{SSA}}$

Analog ground.

Vssp

Digital ground.

WR

Write (Input; Active Low)

This signal indicates a write operation.

X<sub>2</sub>, X<sub>1</sub>, X<sub>0</sub>

(Input/Output)

Operating mode-specific functions.

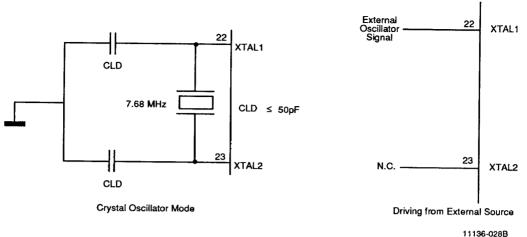

XTAL1

(Input)

Connection for crystal or external clock input.

XTAL2

(Output)

Connection for external crystal. Left unconnected if external clock is used.

1-140 Am2085

## **OPERATIONAL DESCRIPTION**

The ISAC-S, designed for the user area of the ISDN basic access, can be used for the following applications

corresponding to the appropriate basic operating mode of the ISAC-S:

| Terminal equipment type 1                                                                   |                                                          |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------|

| ISDN feature telephone, extended ISDN terminal                                              | TE Mode                                                  |

| Network termination 2                                                                       |                                                          |

| PABX, including the functions for the following:                                            |                                                          |

| -line termination on S(LT-S), just as in a digital<br>subscriber line module                | LT-S mode (INFO 2 and 4 will be generated automatically) |

| SSSSSIBST INTO THOUGH                                                                       | NT mode (Info 2 and 4 must be initiated by software)     |

| <ul> <li>line termination on T(LT-T), just as in a digital<br/>line trunk module</li> </ul> | LT-T mode                                                |

The operating mode of the ISAC-S must be selected by pin-strapping, as described in Operating Modes, before Power On Reset.

## Reset

After Reset, Layer 1 will have reached the following state:

- G1 deactivated in LT-S/(NT) mode

- F3 standby in TE/LT-T mode

according to CCITT I.430 (see Control of Layer 1). F3 standby state means that the internal oscillator is active, and the DCL clock and the FSC1/FSC2 frame signals are delivered as output signals. The F3 power down state, with a minimum power consumption of not more than 8 mW, can be achieved by programming the CFS-bit = "1" in the ADFR register.

Table 1. Subset of ISAC-S Registers with Defined Reset Values (in Hex)

| Register | Value After Reset | Meaning                                                        |

|----------|-------------------|----------------------------------------------------------------|

| ISTA     | 00                | No interrupts                                                  |

| MASK     | 00                | All interrupts enabled                                         |

| EXIR     | 00                | No interrupts                                                  |

| STAR     | 48                | XFIFO is ready to be written to                                |

|          |                   | RFIFO is ready to receive at least 16 octets of a new message  |

| CMDR     | 00                | No command                                                     |

| MODE     | 00                | Auto mode                                                      |

|          |                   | 1-octet address field                                          |

|          |                   | External timer mode                                            |

|          |                   | Receiver inactive                                              |

|          |                   | IOM interface, monitor channel not used (TE: pt-pt, LT-S/(NT): |

|          |                   | point-to-multipoint)                                           |

| RFBC     | 00                | No frame bytes received                                        |

| SPCR     | 00                | SDI pin = High                                                 |

|          |                   | SIP/SAW pin "High Impedance" (SLD interface deactivated)       |

|          |                   | Timing mode 0 (terminal)                                       |

|          |                   | IOM interface test loop deactivated                            |

| •        |                   | SLD B-channel loop is selected                                 |

|          |                   | SDAX pin = High                                                |

| STCR     | 00                | Serial interface port for the SLD interface selected           |

|          |                   | TIC bus address 0                                              |

|          |                   | No Synchronous Transfer                                        |

| CIXR     | BF                | C/I code = 1111                                                |

|          |                   | TE-channel data = 1                                            |

|          |                   | TIC bus is not requested for transmitting a C/I code           |

| ADFR     | 00                | No prefilter                                                   |

|          |                   | Active clock signals (Standby) in TE mode                      |

|          |                   | Adaptive timing (point-to-multipoint) in NT/LT-S               |

|          |                   | FSC1/FSC2 frame signals are not inverted in TE mode            |

|          |                   | Interframe time fill = consecutive 1                           |

Am2085

1-141

## Initialization

During initialization phase the appropriate registers must be programmed according to the application and the desired features, as listed in Table 2.

Table 2. Programming for initialization Phase

| Function             | Register  | Effect                                                                                                             |

|----------------------|-----------|--------------------------------------------------------------------------------------------------------------------|

| Special Functions    | ADFR      | Prefilter                                                                                                          |

|                      |           | Disabled Layer-1 functions                                                                                         |

|                      |           | Standby/power-down selection in TE mode, fixed (point-to-point, S interface), adaptive (S-bus) timing in LT-S mode |

|                      |           | B1/B2-channel assignment (SSI) in TE mode                                                                          |

|                      |           | Interframe time fill in HDLC port mode                                                                             |

| Masking Interrupts   | MASK      | Masking of selective interrupt sources                                                                             |

| D-channel            | MODE      | Message transfer mode                                                                                              |

| (HDLC port)          |           | 2-octet/(1-octet) address                                                                                          |

|                      |           | Timer mode: external/internal (auto mode only)                                                                     |

|                      |           | IOM interface mode:                                                                                                |

|                      |           | IOM: point-to-point and point-to-multipoint (LT-S,NT) IOM: point-to-multipoint (TE)                                |

|                      |           | HDLC port: (TEM-bit 1)                                                                                             |

|                      | TIMR      | N1 and T1 in internal timer mode (TDM-bit in mode) T2 in external timer mode                                       |

|                      | XAD1      | SAPI: LAPD transmit address octet (auto mode only)                                                                 |

|                      | XAD2      | TEI:                                                                                                               |

|                      | SAP1/SAP2 | SAPI: LAPD receive address octet for the internal address recognition                                              |

|                      | TEI1/TEI2 | TEI:                                                                                                               |

| Serial interface     | SPCR      | SLD port inactive/active                                                                                           |

| B-channel switching, |           | Timing mode 0, 1                                                                                                   |

| Terminal-specific    |           | IOM interface loop (reduced timer resolution)                                                                      |

| functions            |           | B-channel switching                                                                                                |

|                      | STCR      | Terminal-specific functions/SLD interface                                                                          |

|                      |           | TIC bus address                                                                                                    |

|                      | CIXR      | Subscriber/Exchange Awake, Watchdog Timer                                                                          |

Table 3. Characteristics and Typical ISDN Applications of the Message Transfer Modes

|                        |                                                                                                                     | Message Tra                                                                | ansfer Modes                   |                                |                                                |

|------------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------|--------------------------------|------------------------------------------------|

|                        | Auto Mode                                                                                                           | Non-<br>Auto Mode                                                          | Transparent<br>Mode            | Ext. Transparent<br>Mode 1     | Ext. Transparent<br>Mode 0                     |

| Characteristics        | One logical link (SAP1, TEI1) can be handled autonomously Window Size (WZ) = 1 Full address recognition (SAPI, TEI) | Full<br>address<br>recognition<br>(SAPI, TEI)                              | SAPI<br>address<br>recognition | SAPI<br>address<br>recognition | No address<br>recognition<br>fully transparent |

| Typical<br>Application | Terminal: WZ = 1<br>Exchange:<br>point-to-point<br>configuration<br>WZ = 1                                          | Terminal: WZ ≥ 1<br>Exchange:<br>point-to-point<br>configuration<br>WZ ≥ 1 | Exchange:<br>bus configuration | Exchange:<br>bus configuration | Diagnostic                                     |

1-142 Am2085

## **Processing**

Assuming the ISAC-S has been initialized for typical applications in the user area of the ISDN basic access, the ISAC-S is now ready to transmit and receive messages in the D-channel (LAPD support). As a prerequisite for that, the Layer 1 must be previously activated. The control of the data transfer phase is mainly done by commands from microprocessor to ISAC-S via the CMDR register and by interrupt indications from ISAC-S to microprocessor (ISTA and EXIR register).

The two B-channels (B1/B2) can be switched in a highly flexible manner between the S interface (IOM interface) and the SSI and SLD interface.

## Control of Layer 1

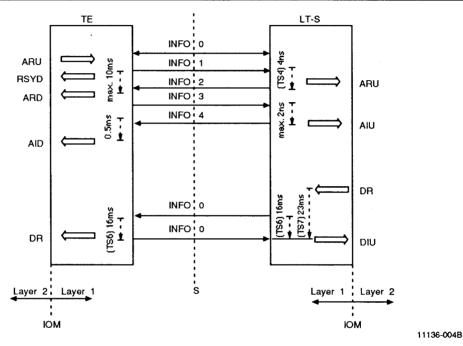

The management commands of Layer 2, programmed in the CIXR register, trigger certain procedures in Layer 1. The responses from Layer 1 can be read from CIRR register after a CIC interrupt (ISTA). An example of activation and deactivation with the respective commands and indications is depicted in Figure 4.

Figure 4. Example of Activation/Deactivation

Am2085 1-143

Tables 4 to 6 contain the command/indication codes in the different operating modes:

Table 4. Commands and Indications in LT-S Mode

| Command (downstream)  | Abbr. | Code | Remark                                                 |

|-----------------------|-------|------|--------------------------------------------------------|

| Deactivate request    | DR    | 0000 | (x)                                                    |

| Send continuous zeros | SCZ   | 0001 | Transmission of AMI pulses at a frequency of 96 kHz (x |

| Send single zeros     | SSZ   | 0010 | Transmission of AMI pulses at a frequency of 2 kHz (x) |

| Activate request      | ARD   | 1000 | (1)                                                    |

| Activate request loop | ARL   | 1010 | Activate request for loop 2                            |

| Deactivate indication | DID   | 1111 | Deactivation acknowledgment, quiescent state           |

| Indication (upstream) |       |      |                                                        |

| Lost signal level     | LSL   | 0001 | No receive signal                                      |

| Lost framing          | RSYU  | 0100 | Receiver is not synchronous                            |

| Activate request      | ARU   | 1000 | Info 1 received                                        |

| Activate indication   | AlU   | 0100 | Synchronous receiver                                   |

| Deactivate indication | DIU   | 1111 | Timer TS6 or TS7 expired after deactivation command    |

Table 5. Commands and Indications In NT Mode

| Command (downstream)     | Abbr. | Code | Remark                                              |

|--------------------------|-------|------|-----------------------------------------------------|

| Deactivate request       | DR    | 0000 | (x)                                                 |

| Send continuous zeros    | SCZ   | 0100 | Transmission of AMI pulses at a frequency of 96 kHz |

| Activate request         | ARD   | 1000 | Transmission of info 2                              |

| Activate request loop    | ARL   | 1010 | Transmission of info 2, switching of test loop 2    |

| Deactivate indication    | DID   | 1111 | Deactivation acknowledgment, quiescent state        |

| Activate indication      | AID   | 1100 | Transmission of info 4                              |

| Activate indication loop | AIL   | 1110 |                                                     |

| Indication (upstream)    |       |      |                                                     |

| Timing                   | TIM   | 0000 | Clocks are required                                 |

| Lost signal level        | LSL   | 0001 | No receive level                                    |

| Lost framing             | RSYU  | 0100 | Receiver is not synchronous                         |

| Error indication         | EI    | 0110 | RST and SCZ both active                             |

| Activate request         | ARU   | 1000 | Info 1 received                                     |

| Activate indication      | AIU   | 1100 | Synchronous receiver                                |

| Deactivate indication    | DIU   | 1111 | Timer TS6 or TS7 expired after deactivation command |

1-144 Am2085

Table 6. Commands and Indications TE/LT-T

| Command (downstream)                       | Abbr. | Code | Remark                                                |

|--------------------------------------------|-------|------|-------------------------------------------------------|

| Timing                                     | TIM   | 0000 | Clocks are required                                   |

| Reset                                      | RS    | 0001 | (x)                                                   |

| Send single zeros                          | SSZ   | 0010 | Transmission of AMI pulses at a frequency of 2 kHz (x |

| Activate request, priority 8               | AR8   | 1000 | Activation command set D-channel priority to 8        |

| Activate request, priority 10              | AR10  | 1001 | Activation command set D-channel priority to 10       |

| Activate request                           | ARL   | 1010 | Activation of test loop 3 (x)                         |

| Deactivate indication                      | DIU   | 1111 | IOM interface can be switched into idle state         |

| Indication (upstream)                      |       |      |                                                       |

| Power up                                   | PU    | 0111 | IOM clocking is provided                              |

| Deactivate request                         | DR    | 0000 | Deactivation request by S                             |

| Slip detected                              | SD    | 0010 | Wander is larger than 18 µs peak-to-peak              |

| Disconnected                               | DIS   | 0100 | Pin CON connected to GND                              |

| Error indication                           | ΕI    | 0110 | (RST=1 and CFS-bit=0) or RS                           |

| Level detected                             | RSY   | 0100 | Signal received, receiver                             |

| Activate request                           | ARD   | 1000 | Info 2 received                                       |

| Test indication                            | TI    | 1010 | Test loop 3 activated or continuous zeros transmitted |

| Activate indication with priority class 8  | 8 IA  | 1100 | Info 4 received, D-channel priority is 8 or 9         |

| Activate indication with priority class 10 | Al 10 | 1101 | Info 4 received, D-channel priority is 10 or 11       |

| Deactivate indication                      | DID   | 1111 | Clocks will be in disabled quiescent state            |

| Note: (x) = unconditional comm             | ands  |      | ,                                                     |

## Transfer of LAPD frames in the D-Channel

When Layer 1 of the S interface is activated, the ISAC-S is able to transmit and receive LAPD frames via this international standardized interface in a highly sophisticated manner.

The LAPD protocol support depends on the selected message transfer mode (Table 5 and Layer 2 Functions section). The powerful FIFO structure of the ISAC-S,

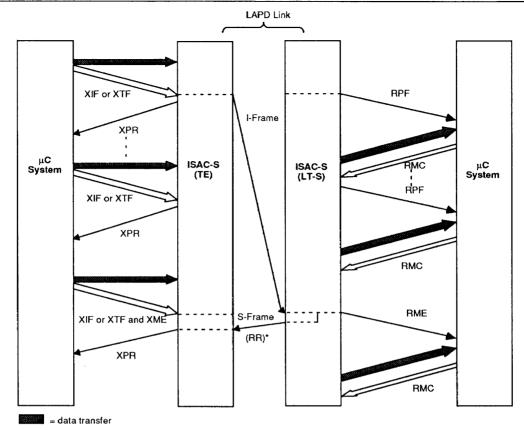

which consists of a 2  $\times$  32 byte receive and a 2  $\times$  32 byte transmit FIFO, as well as an intelligent FIFO controller, builds a flexible connection between the LAPD controller of the ISAC-S and upper layer protocol functions in the microcontroller system via the microprocessor interface. Assuming a normally running communication link (Layer 1 activated, Layer 2 link established, TEI assigned, and so on), Figure 5 demonstrates the transfer of an I-frame via the D channel.

\*In auto mode, the "RR" response will be transmitted autonomously (provided operation is normal)

11136-005B

Figure 5. Transmission of an I-Frame in the D-channel (Subscriber to Exchange)

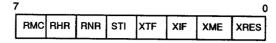

The following table summarizes the commands which can be programmed by setting appropriate bits in the

CMDR register to Control Layer 2 (see also Detailed Register Description).

Table 7. CMDR Register Bits for Layer 2 Control

| Com. | HEX | Bit 70    | Meaning                                                |

|------|-----|-----------|--------------------------------------------------------|

| RMC  | 80  | 1000 0000 | Receive message complete                               |

| RHR  | 40  | 0100 0000 | Reset HDLC receiver                                    |

| RNR  | 20  | 0010 0000 | Receiver not ready (auto mode)                         |

| STI  | 10  | 0001 0000 | Start timer                                            |

| XTF  | 08  | 0000 1000 | Transmit transparent frame without closing the frame   |

| XIF  | 04  | 0000 0100 | Transmit "auto mode" I-frame without closing the frame |

| XTFC | OA  | 0000 1010 | Transmit transparent frame and close frame             |

| XIFC | 06  | 0000 0110 | Transmit "auto mode" I-frame and close frame           |

| RHX  | 01  | 0000 0001 | Reset HDLC Transmitter                                 |

1-146 Am2085

# Interrupt List

In the following table, all interrupts of the ISAC-S are listed together (see also Detailed Register Description).

Table 8. Meaning of ISAC-S Interrupts (Layer 1 and Layer 2)

|                                    |            | Interrupt    |                                                | Meaning                                                                                                | Reaction (ISDN)                                                                                                                                |

|------------------------------------|------------|--------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Layer 2<br>receive                 | RPF<br>RME | ISTA<br>ISTA | Receive<br>Pool Full<br>Receive<br>Message End | Request for reading received octets of a LAPD frame from RFIFO.                                        | Read the octets and acknowledge with RMC command.                                                                                              |

|                                    | RFO        | EXIR         | Receive<br>Frame<br>Overflow                   | A frame has been lost.<br>The microcontroller<br>has failed the minimum<br>reaction time.              | Error report for statistical purposes only.                                                                                                    |

|                                    | PCE        | EXIR         | Protocol<br>Error                              | S- or I-frame with in-<br>correct N(R) or S-frame<br>with I-field received,<br>(in auto mode only).    | Error report Data link release indication to Layer 3.                                                                                          |

|                                    | TIN        | ISTA         | Timer<br>interrupt                             | External timer expired or, in auto mode, internal timer (T200) and repeat counter (N200) both expired. | Error report Data link release indication to Layer 3 (no acknowledgment from peer entity).                                                     |

| Layer 2<br>transmit                | XPR        | ISTA         | Transmit<br>Pool Ready                         | Acknowledgment that further octels of an LAPD frame can be written to the XFIFO.                       | Write further octets to the XFIFO and subsequently request (further) transmission with X_F or X_FC.                                            |

|                                    | RSC        | ISTA         | Receive<br>Status<br>Change                    | A status change from<br>peer has been received,<br>RR/RNR frame,                                       | Read STAR register, check<br>RRNR-bit and report it.                                                                                           |

|                                    | XMR        | EXIR         | Transmit<br>Message<br>Repeat                  | Frame must be repeated due to a transmission error and/or a received negative acknowledgment.          | Transmission of this frame must be repeated. No indication to Layer 3.                                                                         |

|                                    | XDU        | EXIR         | Transmit<br>Data<br>Underrun                   | Frame has been aborted because the XFIFO holds no further data (messages greater than 32 octets).      |                                                                                                                                                |

| Layer 1                            | CIC        | ISTA         | C/I Code<br>Change                             | A change of indication<br>from layer-1 has been<br>detected.                                           | Read CIRR register and report reason to management entity.                                                                                     |

|                                    | MOR        | EXIR         | _                                              | Not used in the ISAC-S.                                                                                | management entity.                                                                                                                             |

| Synchronous<br>transfer            | SIN        | ISTA         | Synchronous<br>Transfer<br>Interrupt           | Synchronization of micro-<br>processor and data transfer<br>via serial interfaces.                     | Access to B-channel registers BCX1/2, BCR1/2, or SFCR. Has to be confirmed by setting the appropriate STO/(1)-bit in STCR within a time limit. |

| 77.3                               | SOV        | EXIR         | Synchronous<br>Transfer<br>Overflow            | The SIN interrupt was not confirmed on time by setting the appropriate ST0/(1)-bit in STCR.            | Abnormal error condition.<br>Revise access software.                                                                                           |

| Terminal-<br>specific<br>functions | SAW        | EXIR         | Subscriber<br>Awake                            | Indicates a falling edge<br>on SAW line (terminal-<br>specific functions are selected.                 | Switch into "Power Up"<br>state and start data link                                                                                            |

|                                    | wov        | EXIR         | Watchdog<br>Timer<br>Overflow                  | Watchdog timer has been expired (terminal-specific functions are selected).                            | establish procedure.<br>Worst error condition.<br>Restart system software.                                                                     |

|                                    | EXI        | ISTA         | Extended<br>Interrupt                          | An interrupt indicated in EXIR has occurred.                                                           | Read EXIR and determine interrupt source.                                                                                                      |

#### **FUNCTIONAL DESCRIPTION**

The Am2085 performs the Layer 1 functions of the ISDN basic access as well as B-channel switching and widespread functional support for Layer 2.

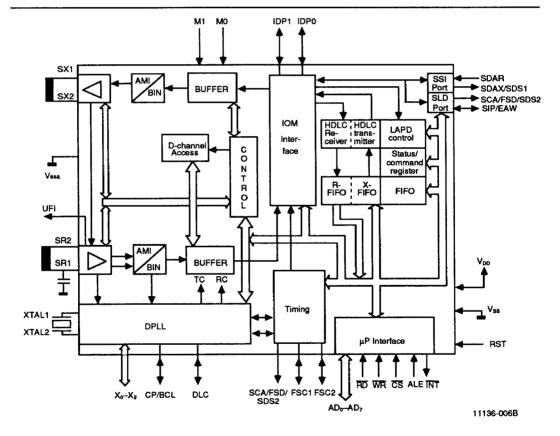

### General Functions and Device Architecture

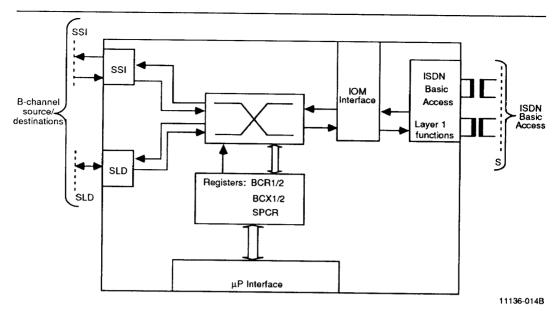

The detailed block diagram of the ISAC-S is shown in Figure 6.

The left side of the diagram contains the Layer 1 functions, according to CCITT I series recommendations:

- S-bus transmitter and receiver

- Timing recovery and synchronization by means of digital PLL circuitry

- Activation/Deactivation

D-channel access

Furthermore the following diagnostic tests are implemented:

- Test loop 2 (NT/LT-S) and 3 (TE/LT-T) close to the S-bus

- Send single AMI pulses at 2 kHz and send continuous AMI pulses at 96 kHz

The right side consists of Layer 2 functions to support LAPD and provides B-channel switching capabilities.

In a special operating mode, the auto mode, the ISAC-S processes information transfer and procedure handshakes (I- and S-frames) of the LAPD protocol autonomously.

Flaure 6. ISAC-S Device Architecture

1-148 Am2085

Two serial interfaces to B-channel sources/destinations are realized:

- The standard SLD interface which is a bidirectional (ping-pong) 256-kb/s interface primarily optimized for telecommunication applications

- The full-duplex 128-kb/s interface, SSI, which can serve as a general interface in TEs to transfer the two B-channels

Control and monitor functions as well as data transfers (D-channel messages, transparent B-channel data) by the user's CPU is performed through a standard 8-bit microprocessor interface. A highly sophisticated 2 × 64 byte FIFO structure for both directions enables a flexible D-channel message information exchange between the LAPD (HDLC) controller and a microcontroller system.

The timing unit is responsible for the system clock and frame synchronization. Pin-strapping determines its operating mode.

# **Operating Modes**

The Am2085 is configurable for the following applications:

- ISDN terminals (TE)

- -> TE (mode)

- ISDN subscriber line termination (LT-S)

- ---> LT-S/(NT) mode

- ISDN trunk line termination (PABX connection to central office)

- -> LT-T mode

Configuration is performed by pin-strapping (pins  $M_2$ ,  $M_0$ ), yielding different meanings to the multifunctional pins ( $X_0$ ,  $X_1$ ,  $X_2$ ) as well as the clock and framing signal pins (DCL, FSC1, FSC2, CP).

Table 9. Operating Modes and Functions of Mode-Specific Pins of Am2085 ISAC-S

| Appli-<br>cation | M2 | Мо | DCL         | FSC1/2    | СР           | X2                     | X1               | Χo            |

|------------------|----|----|-------------|-----------|--------------|------------------------|------------------|---------------|

| TE               | 0  | 0  | O: 512 kHz* | O: 8 kHz* | O: 1536 kHz* | O: ECHO                | 0. 0040111       |               |

| LT-T             | ñ  | 1  | l: 512 kHz  | l: 8 kHz  |              |                        | O: 3840 kHz      | I: CON        |

|                  | •  | •  |             | I. OKIZ   | O: 512 kHz*  | <li>l: fixed at 0</li> | I: fixed at 0    | 1: CON        |

| LT-S1            | 1  | 0  | l: 512 kHz  | i: 8 kHz  | l: fixed     | l: fixed at 0          | O: 7680 kHz at 0 | l: fixed at 0 |

| NT               | 1  | 1  | l: 512 kHz  | l: 8 kHz  | I: SCZ       | I: SSZ                 | l: fixed at 0    | - 11X00 at 1  |

Notes: ECHO Reproduces the E-bits received from the S interface synchronously to IOM frame "D"-bits

(bit positions 24 and 25 of IOM frame). All other bit positions are binary 1.

CON Connected to S-bus

SCZ Send continuous binary zeros (96 kHz)

SSZ Send single binary zeros (2 kHz)

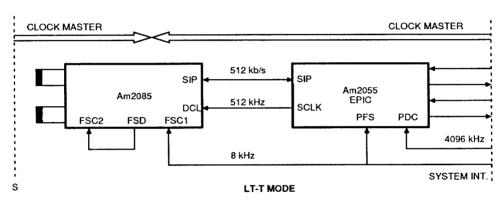

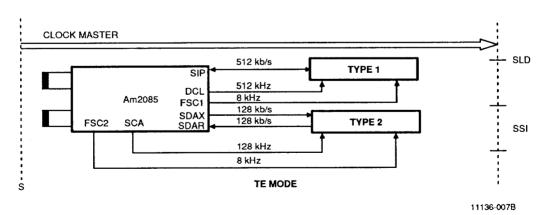

Figure 7. Operating Modes of ISAC-S

1-150 Am2085

## Interfaces

The ISAC-S serves three different user-oriented interface types:

- parallel processor interface to higher layer functions

- SSI and SLD as interfaces for B-channel sources/ destinations

- IOM interface; to the Layer 1 functions of the ISDN basic access (TIC bus)

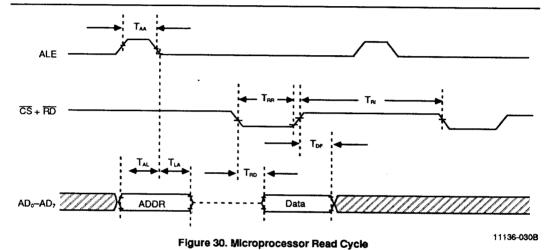

## Microprocessor Interface

The microprocessor interface consists of bus transceiver, address register, and bus control logic. Via this interface, the ISAC-S can be connected to the multiplexed address/data bus of a microcontroller system. The following functions can be performed by writing and reading special registers in the ISAC-S (see Detailed Register Description section):

- Transfer of data packets in the D-channel

- Control of Layer 2 functions for the ISDN basic access

- Switching of B-channels

- Access to the B-channels

- Control of Layer 1 functions for the ISDN basic access

- Support of diagnostic functions

In the case of special events in the ISAC-S, the processor is notified by interrupt. The interrupt source can be determined and acknowledged by means of the ISAC-S registers ISTA, EXIR, and MASK (see Detailed Register Description).

# Serial Synchronous Interface (SSI)

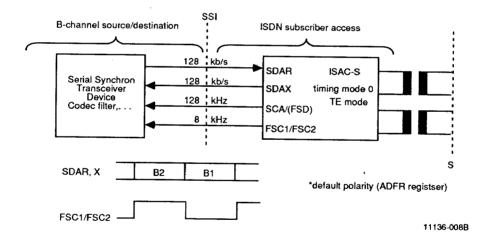

The serial port SSI serves as a full-duplex connection to B-channel sources/destinations in terminal equipment with a data rate of 128 kb/s. SSI consists of one data line for each direction (SDAX and SDAR), the 8-kHz frame synchronization signal (FSC1 and/or FSC2), and the 128-kHz clock signal (SCA/FSD). This serial interface allows the possible connection of serial synchronous transceiver devices (USART Am82520 HSCC) and various CODEC filters directly to the ISAC-S, as illustrated in Figure 8.

Figure 8. Connection of B-channel Sources/Destinations to the ISAC-S via SSI

Programming the FSC1/FSC2-bit in the ADFR register makes it possible to independently program the strobe signals FSC1/FSC2 so that either B1 or B2 is selected for further processing by the terminal device. The microcontroller system has access to B-channel data via the ISAC-S registers BCR1/BCR2 and BCX1/BCX2.

The microprocessor access must be synchronized to the serial transmission process by means of the Synchronous Transfer Interrupt (STCR; see Detailed Register Description).

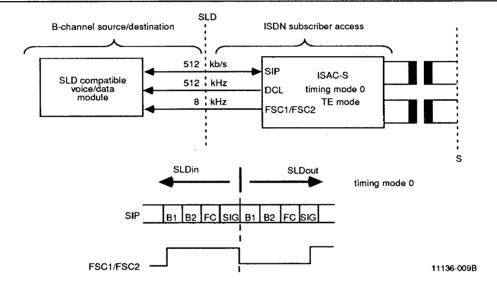

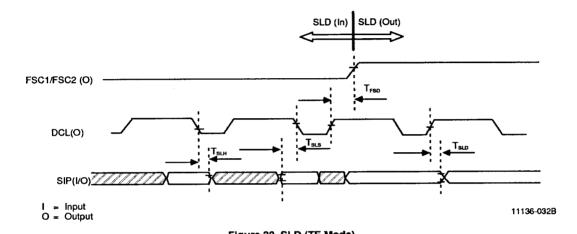

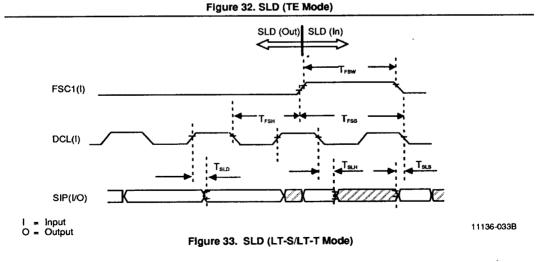

#### **SLD Interface**

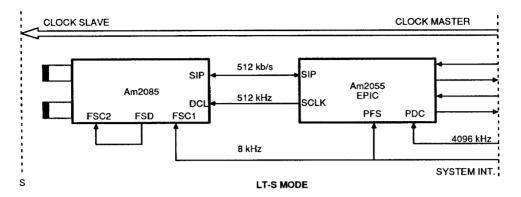

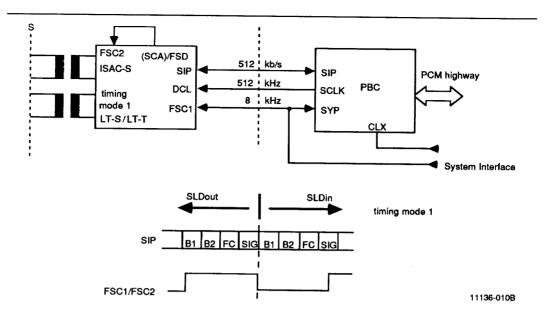

The standard SLD interface is a three-wire interface with a 512-kHz clock (DCL), an 8-kHz frame direction signal (exchange: FSC1 only, terminal: FSC1 and FSC2), and a serial ping-pong data lead (SIP) with an effective full-duplex data rate of 256 kb/s.

The SLD interface can be used in:

- Terminal configurations (timing mode "0") as a full-duplex time-multiplexed (ping-pong) connection to B-channel sources/destinations.

- Digital exchange configurations (timing mode "1") as a full-duplex time-multiplexed connection of B-channel sources/destinations, in this case the ISAC-S itself, to a peripheral board controller. In a typical line-card application the PBC performs time slot assignment of the B-channels to PCM highways, building a system interface to a switching network and a central processor as shown in Figure 10.

Figure 9. Connection of B-channel Sources/Destinations to the ISAC-S via SLD

Figure 10. Connection of the ISAC-S as B-channel Source/Destination to a Peripheral Board Controller (PBC)

The microcontroller system has access to B-channel data, the Feature Control Byte (FC) and the Signaling Information (SIG) via the ISAC-S registers:

- BCR1/2 and BCX1/2 <---B1/B2

- SFCR

- <--FC

- SSGR and SSGX <--SIG

The microprocessor access to BCR1/2, BCX1/2 and SFCR must be synchronized to the serial transmission process by means of the Synchronous Transfer Interrupt (STCR) and the BVS-bit (STAR).

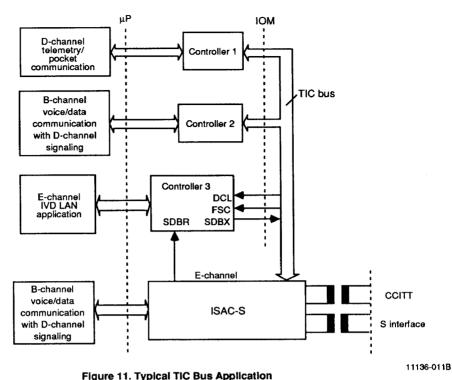

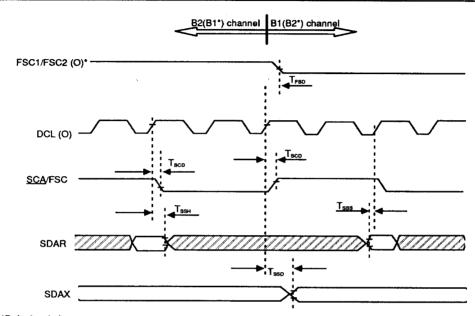

# ISDN Oriented Modular (IOM) Interface

Although the ISAC-S combines the Layer 1 functions of an Am2080 S-bus transceiver (SBC) with the HDLC functions on one chip, the IOM interface is externally still available for Telecom IC (TIC) bus applications. The TIC bus allows the possible connection of up to seven additional IOM-compatible Communications Controllers via the Layer 1 functions of the ISAC-S to CCITT's S interface as shown in Figure 11.

rigule II. Typical IIO bas Applicat

nd a avnahrani

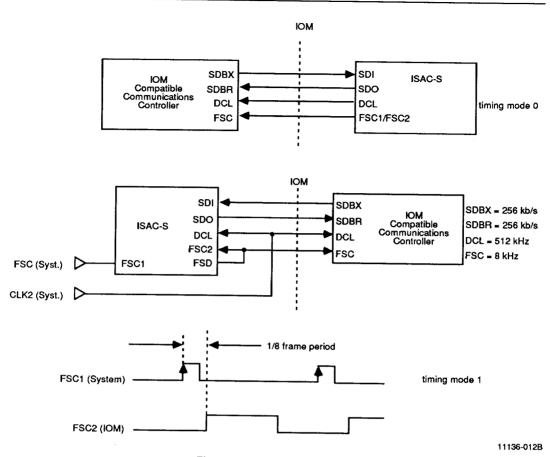

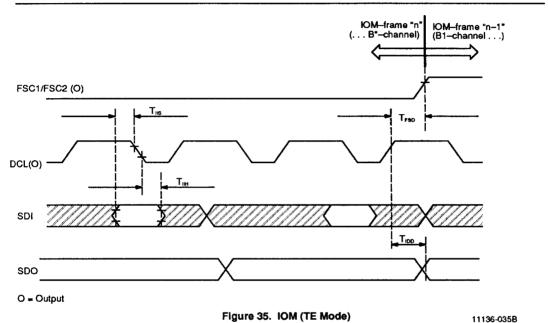

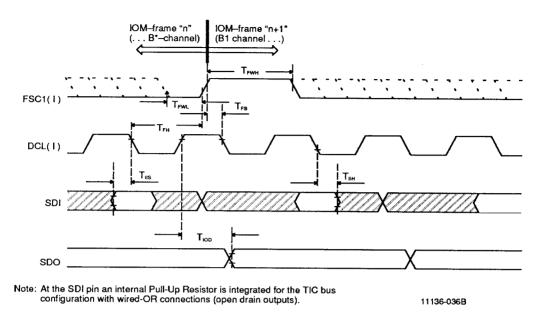

The IOM interface consists of one data line per direction (SDBR and SDBX). Three additional signals define the data clock (DCL) and the frame synchronization (FSC1/FSC2) at this interface. These signals are internally derived from the S interface and are delivered by the ISAC-S in timing mode 0 (terminal).

In timing mode 1 (exchange), the clock and a synchronization signal are provided by the system. In this case, the IOM interface is synchronization by a synchronization signal SCA/FSD, delayed in time with respect to the frame synchronization signal supplied by the system. This reduces the round-trip delay time (see Figure 12).

Figure 12. IOM Interface Signals

The IOM interface has two different clocking states:

- Idle state <— FSC1/FSC2 and DCL are disabled and both data lines are logical High (power down)

- Clocked state <— FSC1/FSC2 and DCL are enabled (stand by)

Unlike digital exchange configurations in which the IOM interface always remains in the synchronized state, in terminal equipment both clock states can be selected.

The transition from idle state to clocked state will be automatically initiated by an incoming call from network side. An activation of the IOM interface from the subscriber end has to be programmed in this case by setting and resetting the SPU-bit in the SPCR register, before the IOM interface can be used (that is, for the activation/deactivation procedure at the S interface, see Operational Description section).

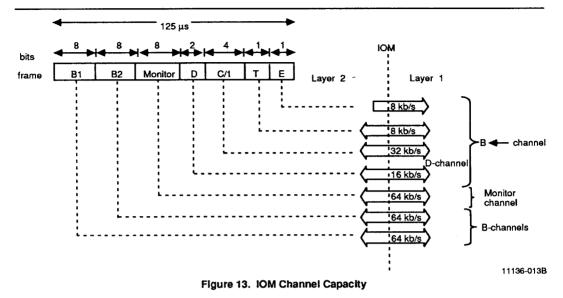

#### The IOM Channel Structure

The channel frame structure of the IOM interface and the related channel capacity are defined in Figure 13 as follows:

In the ISAC-S, the monitor channel supports the TIC bus access mechanism as well as the indication of the S-bus status (D-channel access). The ISAC-S indicates by means of monitor bit 3 (BAC) whether or not it occupies the TIC bus (B-channel).

The control of the Layer 1 functions, especially the activation/deactivation procedure at the S interface, will be done by the exchange of special 4-bit C/I-codes in the C/I channel.

The T-channel, which is fully transparent, and the E-channel are reserved for future use.

#### **TIC Bus**

The TIC bus is operated in point-multipoint configuration. It uses a wired-OR connection of the data outputs to enable the TIC bus access mechanism. Therefore the ISAC-S contains an internal pull-up resistor at the SDI pin.

The TIC bus is controlled by a collision resolution mechanism in the monitor channel similar to the D-channel access on the S-bus.

#### Individual Functions

Distinctive functions for the ISDN basic access realized in the ISAC-S are:

- B-channel switching

- Layer 1 functions

- Layer 2 functions

- Terminal-specific functions

- Test functions

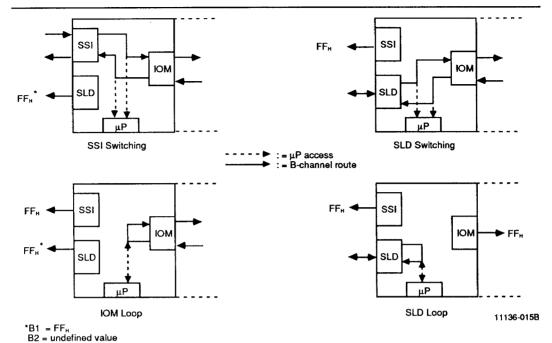

## **B-Channel Switching**

The ISAC-S contains two serial synchronous interfaces which can serve as interfaces to B-channel sources/ destinations.

- SSI -> 128 kb/s data rate, B1 and B2

- --> one data line per direction

- SLD —> 256 kb/s data rate, B1 and B2 (and also FC and SIG)

- one data line for both directions (ping-pong)

Both channels B1 and B2 can be switched independently of one another to the IOM interface and to the four-wire S interface. Furthermore, it is possible to program a loop for B-channel data received from the IOM or SLD interface. The microcontroller can select the B-channel routes in the SPCR register and has access to the B-channels by writing or reading the BCR/BCR2 and BCX1/BCX2 registers (Figure 14). Synchronization to the 8-kHz frame is done by means of a Synchronous Transfer programmed in the STCR register (SIN Interrupt indicated in the ISTA register and SOV interrupt in EXIR).

1-156 Am2085

Figure 14. Principle of B-channel Switching

In Figure 15 all possible selections of the B-channel routes and access to B-channel data via the micoprocessor interface are illustrated.

Figure 15. B-channel Routes and Access to B-channel Data

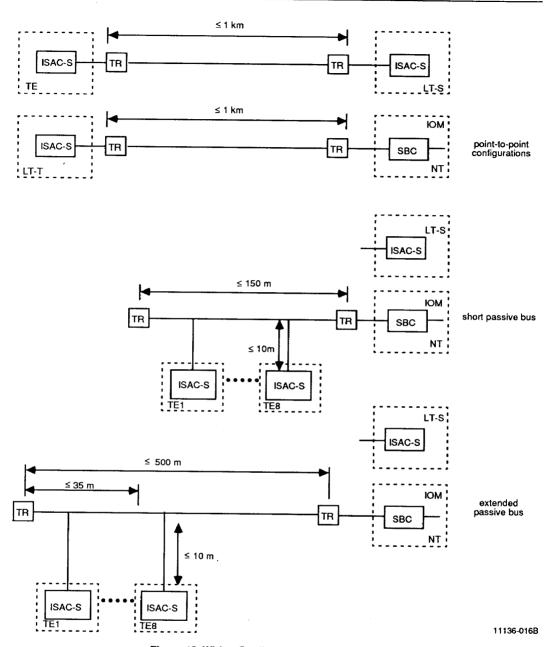

## Layer 1 Functions for the ISDN Basic Access

The S-bus interface circuit in the ISAC-S performs the Layer 1 functions for the S/T interface of the ISDN basic access according to CCITT I.430. The distinctive functions are listed below:

- S-bus transceiver according to CCITT I.430

- Recovery of clock and frame in all applications

- Frame alignment for trunk line termination

- Implementation of activation/deactivation procedures

- Switching of test loops

- Level detection in power-down state

The wiring configurations in user premises, in which the ISAC-S can be used, are illustrated in Figure 16.

1-158 Am2085

Figure 16. Wiring Configurations in User Premises

# "S" Interface

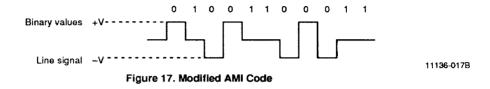

According to CCITT recommendation I.430, a modified AMI code with 100% pulse width is used on the S interface. A logical 1 corresponds to a neutral level (no current), whereas logical 0s are coded as alternating positive and negative pulses. An example of a modified AMI code is shown in Figure 17.

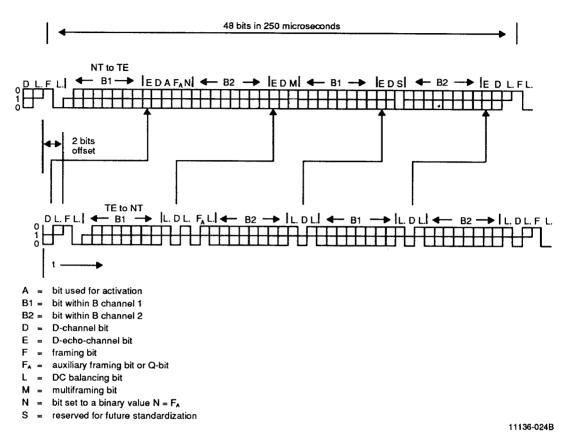

One S-frame consists of 48 bits at a nominal bit rate of 192 kb/s. Thus each frame carries two octets of B1, two octets of B2, and four D-bits, according to the B1+B2+D structure defined for the ISDN basic access (total useful data rate: 144 kb/s). Frame beginning is marked using a code violation. The frame structures (from network to subscriber and subscriber to network) are shown in Figure 18.

1-160 Am2085

# ISDN APPLICATIONS System Integration

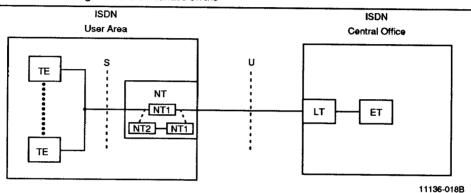

The basic architecture for the ISDN basic access according to CCITT I series recommendations consists of

- an exchange and trunk line termination in the central office (ET, LT)

- a remote network termination in the user area (NT)

- a two-wire loop (U interface) between NT and LT

- a four-wire link (S interface) which connects subscriber terminals, PABX system and the NT in the user area as depicted in Figure 18.

The NT equipment simply serves as a link between the U interface on the exchange and the S interface on the

user side. The NT itself may consist of either an NT1 only or an NT1 together with an NT2 connected via the T interface which is physically identical to the S interface. The NT1 is a direct transformation between Layer 1 of S and Layer 1 of U. NT2 also includes the complex functions like multiplex and exchange functions in higher layer OSI functions.

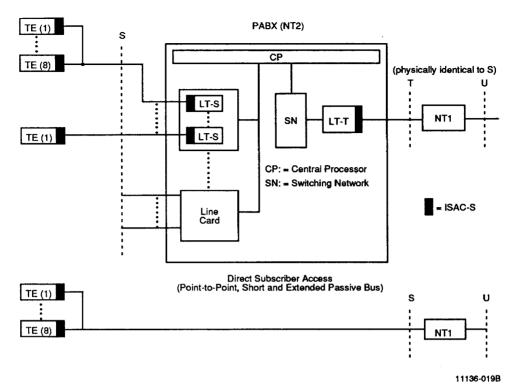

The ISAC-S is specifically designed for the user area of the ISDN basic access, especially Terminal and PABX exchange equipment. Figure 19 illustrates the general subscriber access architecture in the user area of the ISDN basic access including Terminal and PABX equipment.

Figure 18. ISDN Architecture for the Basic Access

Figure 19. ISAC-S Applications in the User Area (ISDN Basic Access)

The concept of the ISDN basic access is based on two circuit-switched 64 kb/s B-channels and a message-oriented 16 kb/s D-channel for packetized data, signaling, and telemetry information.

The two serial interfaces of the ISAC-S, SLD, and SSI can be used as interfaces for B-channel sources/destinations, and the IOM interface in TIC-bus configuration provides the possibility of connecting further D-channel link entities to the S-bus.

Via the microprocessor interface, the microcomputer system can select the B-channel switching, can transmit/receive data packets in the D-channel, and has control over various functions (Layer 2, Layer 1, diagnostic, . . .).

To get a general idea, the following figures illustrate the ISAC-S integration into typical ISDN applications.

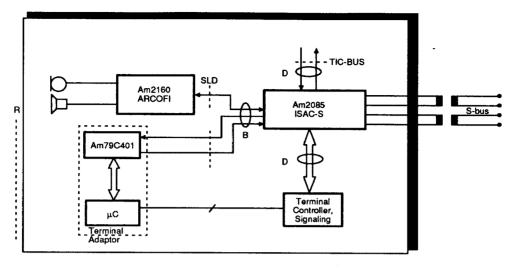

Figure 20. Extended ISDN Terminal (Voice/Data Workstation)

11136-020B

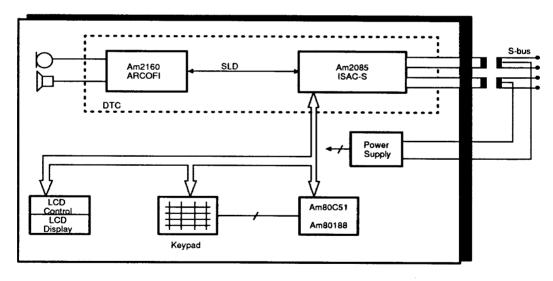

Figure 21. Basic ISDN Feature Telephone

11136-021B

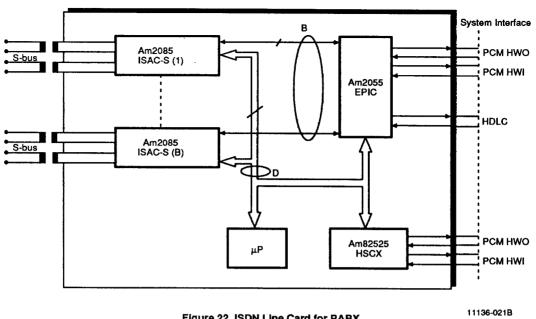

Figure 22. ISDN Line Card for PABX

1-164 Am2085

# Microprocessor Environment

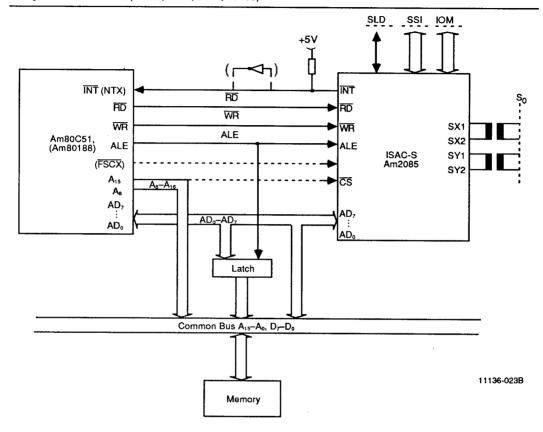

The ISAC-S is especially suitable for cost-sensitive applications with single-chip microcontrollers (that is, Am8031, Am8051). Due to its bus structure (8-bit multiplexed address/data bus) and non-critical bus timing, it also fits perfectly into almost every 8-bit microprocessor system environment (that is, 8085, 8088, 80188).

With minimum hardware or software expense, it is also possible to use the ISAC-S with 16-bit microprocessors (that is, 8086, 80186). Figure 23 gives an example of the integration of ISAC-S in an 80C51 or 80188 system.

Figure 23. Example of Integration of ISAC-S in an Am80C51 or Am80188 System

Note: Dots demarcate those parts of the frame that are independently DC-balanced.

Figure 24. Frame Structure at Reference Points S and T (CCITT I.430)

1-166 Am2085

## **Analog Functions**

The full-bauded AMI pulse shaping is achieved with the integrated transmitter which is realized as a voltage limited current source. A current of 7.5 mA is delivered over SX1-SX2, which yields a voltage of 1.5 V over 200 ohms.

The receiver is designed as a threshold detector with adaptively switched threshold levels. Pin SR1 delivers 2.5 V as an output, which is the virtual ground of the input signal on pin SR2.

An external transformer of ratio 2:1 is needed in both receive and transmit directions to provide for isolation and to transform voltage levels according to CCITT recommendations.

# Level Detection Power Down (TE mode)

In power-down state, only an analog level detector is active. All clocks, including the IOM interface, are stopped. The data lines are High, whereas the clocks are Low.

An activation initiated from the exchange side (Info 2 on S-bus detected) will have the consequence that a clock signal is provided automatically. From the terminal side, an activation must be started by setting and resetting the SPU-bit in the SPCR register (see Detailed Register Description section).

#### **Timing Recovery**

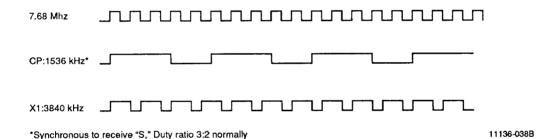

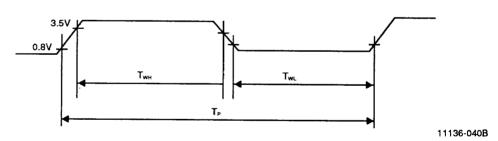

A DPLL circuitry working with a frequency of 7.68 MHz  $\pm 100$  ppm serves to generate the 192-kHz line clock from the reference clock delivered by the network and to extract the 192-kHz line clock from the receive data stream.

The 7.68-MHz clock may be generated with the help of an external crystal between pins XTAL1 and XTAL2. It may also be provided by an external oscillator.

The buffer memory serves to adapt the different bit rates of the S and the IOM interface. In addition, in trunk line applications it absorbs the possible deviation between two system clocks, according to CCITT Q.503.

#### Activation/Deactivation

An incorporated finite state machine controls ISDN Layer 1 activation/deactivation according to CCITT.

#### **D-Channel Access**

The D-channel access procedure according to CCITT I.430, including priority management, is fully implemented in the ISAC-S. When used in LT-S (NT) mode in a multipoint configuration, the device generates the echo bits necessary for D-channel collision detection.

#### Q-Channel Support

Interminal applications (TE), the Q-channel as specified by I.430 is supported. In case the ISAC-S in the terminal has received a binary one in FA-bit position, it will reflect this binary one in the next S frame (also FA-bit position) from TE to NT. This allows another terminal to use the extra transmission capacity.

## Control of Layer 1

The control of the Layer 1 functions, especially the activation/deactivation procedure at the S interface, will be done by the exchange of special 4-bit Command/Indication codes in the C/I channel (see Operational Description section).

# Layer 2 Functions for the ISDN Basic Access

LAPD, Layer 2 of the D-channel protocol (CCITT I.441) includes functions for :

- Provision of one or more data link connections on a D-channel (multiple LAP). Discrimination between the data link connections is performed by means of a data link connection identifier (DLCI = SAPI + TEI).

- HDLC-framing

- Application of a balanced class of procedure in point-multipoint configuration.

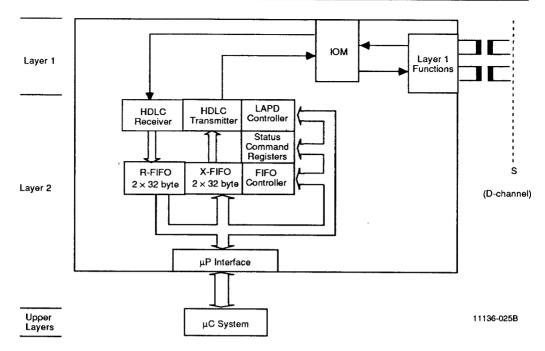

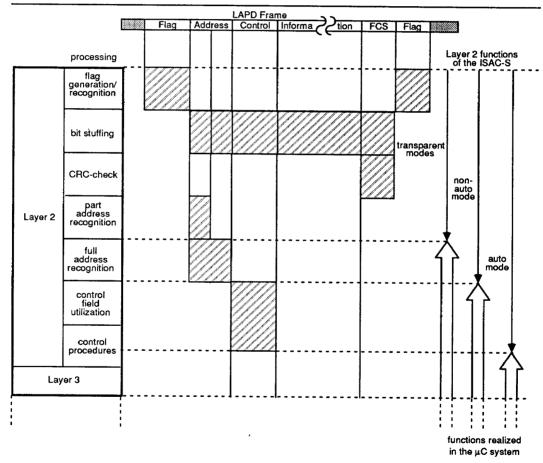

The simplified block diagram in Figure 25 shows the functional blocks of the ISAC-S which support the LAPD protocol.

Figure 25. D-Channel Processing of the ISAC-S

For the support of LAPD, the ISAC-S contains an HDLC transceiver which is responsible for flag generation/recognition, bit stuffing, CRC-check and address recognition. In the auto mode, the LAPD controller handles the control field utilization and parts of LAPD procedures (information transfer in multiple frame operation with window size of 1).

A FIFO structure with two 64-byte pools for transmit and receive directions and an intelligent FIFO controller permits flexible transfer of protocol data units to and from the microcontroller system. Programming of the several modes and control of message transfer is done

via status, command, and mode registers (see Operational Description and Detailed Register Description sections).

For the address recognition, the ISAC-S contains the registers SAP1, SAP2 for an individual SAPI address (fixed value for Group SAPI) and TEI1, TEI2 for an individual TEI address. The C/R-bit interpretation can be programmed according to network or user side in the SAP1 register (CRI-bit). The control field format for the optional modulo 128 operation can be selected in the SAP2 register (MCS-bit).

1-168

#### Message Transfer Modes

The ISAC-S supports Layer 2 of the D-channel protocol (LAPD) with different capabilities depending on the selected message transfer mode.

#### Auto mode

The ISAC-S processes all S- and I-frames of a logical link fully autonomously, according to CCITT 1.441.

During the "communication procedure," dialogue between the ISAC-S and processor is not necessary. The ISAC-S reports the status of the procedure to the processor. The Layer 2 software remaining in the microcontroller system is used for initialization and error recovery. As a prerequisite for this mode, window size 1 must be used between transmitted and acknowledged frames.

#### Non-auto mode

In this mode the control field and the information field of an HDLC frame is forwarded directly to the processor. The Layer 2 address recognition is still performed.

### Transparent modes

The address field is either partly checked by the ISAC-S (SAPI) or completely forwarded to the processor. The Layer 2 headers are either stored in special purpose registers (transparent mode) or, together with the information field, in the FIFO buffer (extended transparent mode).

The three major types of message transfer mode and the corresponding Layer 2 functions in the ISAC-S are illustrated in Figure 26 in relation to the ISO's OSI reference model.

Figure 26. D-channel Protocol Support of the ISAC-S

11136-026B

Am2085

1-169

#### Reception of Frames

Depending on the selected message transfer mode, the protocol data (address, control and information field) of a received frame will be stored in the RFIFO as well as in additional registers (RHCR, TEI1). The processor will be informed by an appropriate interrupt and must react within a corresponding reaction time.

The RFIFO and the FIFO-controller have been so designed that the maximum microprocessor reaction time is 16 ms for messages of more than 32 octets. The processor will be informed about the receiver operation (stalus) chiefly by means of the two interrupts:

- RPF (Receive Pool Full)

- RME (Receive Message End) —> ISTA (see Detailed Register Description)

When one of the two receive pools is filled up completely, the ISAC-S generates an RPF interrupt.

If the processor wants to save the frame, it should, as a consequence, react by reading the 32 bytes out of the RFIFO within the maximum reaction time.

During a handshake procedure between ISAC-S and microcontroller system, the processor has to acknowledge the reading by means of the RMC (Receive Message Complete) command.

When the end of a frame is detected, an RME interrupt will be generated, indicating that the remainder of the current frame is now available in one of the two receive pools. The reception of the last part of a frame must also be completed with an RMC command (see Operational Description).

With respect to the RME interrupt, the ISAC-S provides additional information about the received frame in its internal registers, according to Table 10.

#### Transmission of Frames

The processor initiates the transmission of a message with one of the two commands:

- XTF (Transmit Transparent Frame)

- XIF (Transmit I-frame, in auto mode only)

CMDR

after it has written up to 32 bytes in one of the two 32-byte pools of the XFIFO.

When one pool is empty an XPR interrupt alerts the processor. The processor can then write further data to the XFIFO and enable the continuation of frame transmission according to a handshake procedure with the appropriate transmit command XIF of XTF (see also Interrupt List).

The microcontroller must indicate the message end with an XME command (together with the appropriate transmit command XIF or XTF) for the following cases:

- The message length is shorter than or equal to 32 bytes and all data is entered into the XFIFO or

- The last part of a longer message is written into the XFIFO

Table 10. Received Frame Information Saved in the Internal Registers

| Information                                        | Register | Bit | Mode                        |

|----------------------------------------------------|----------|-----|-----------------------------|

| SAPI of LAPD address field                         | TEI1     |     | Extended transparent mode 0 |

| TEI of LAPD address field                          | TEI1     |     | Extended transparent mode 1 |

|                                                    |          |     | Transparent mode            |

|                                                    | RHCR     |     | Extended transparent mode 0 |

| LAPD control field                                 | RHCR     |     | Auto mode                   |

|                                                    |          |     | Non-auto mode               |

|                                                    |          |     | Transparent mode            |

|                                                    |          |     | Extended transparent mode 1 |

| Type of frame (Command/Response)                   | RSTA     | C/R | <u> </u>                    |

| Result of CRC-check (positive/negative)            | RSTA     | CRC | _                           |

| Data available in RFIFO (yes/no)                   | RSTA     | RDA | <del>_</del>                |

| Abort condition detected (yes/no)                  | RSTA     | RAB |                             |

| Data overflow during reception of a frame (yes/no) | RSTA     | RD0 | _                           |

| Recognition of Data Link Connection                | RSTA     | SAO | Auto mode                   |

| Identifier (DLCI = SAPI + TEI)                     |          | SA1 | Non-auto mode               |

|                                                    |          | TA  |                             |

| Number of bytes received in RFIFO                  | RFBC     | 50  | <del>-</del>                |

| Message length (≤ 223 )                            | RFBC     | 7-0 | <del></del>                 |

1-170 Am2085

An XPR interrupt will also be generated subsequent to:

- The complete transmission of a transparent frame after the XTF and XME command or

- The reception of a positive acknowledge after the XIF and XME command or

- When no frame transmission is in progress and the microprocessor gives the XRES command

The message will be aborted automatically:

- When there is no more data in the XFIFO ready to be transmitted or

- When the processor gives an XRES command

The ISAC-S then transmits an abort sequence and generates an XDU interrupt.

Collisions that occur on the S-bus (D-channel) up to the 32nd data byte of a frame are treated without microprocessor interaction. The ISAC-S will retransmit the frame automatically. If the collision is detected later than the 32nd data byte of a frame, the ISAC-S aborts the frame and requests the processor to repeat the frame with an XMR (Transmit Message Repeat) interrupt.

In every mode, the start flag will be inserted automatically, as are likewise the end flag and the frame check sequence (CRC-16 according to LAPD) which are appended after an XME command.

When auto-mode I-frames are transmitted, the LAPD controller of the ISAC-S generates in addition to the delimiting flags and the FCS field, the address and control field autonomously. In this mode the XFIFO contains only the data for the information field.

The status of the XFIFO can also be read from the STAR register (XFW-bit: XFIFO write enable). This allows for a polling procedure instead of or in addition to the XPR interrupt and can be useful when there is no need to transmit a high quantity of messages (referred to the D-channel capacity).

#### Layer 2 Functions in the Auto Mode

In addition to address recognition, all S- and I-frames are processed independently by the ISAC-S in the auto mode with window size 1. The control field format may be either for basic (modulo 8) or extended (modulo 128) operation. The following functions are performed:

- Update of transmit and receive counter

- Evaluation of transmit and receive counter

- Processing of S commands

- Flow control with RR/RNR

- Response generation

- Recognition of protocol errors

- Transmitting of S commands, if an acknowledgment is not received

- Continuous status query of remote station after RNR has been received

- Programmable timer/repeater functions

#### **Terminal-Specific Functions**

In addition to the ISAC-S standard functions supporting the ISDN basic access, the ISAC-S contains optional functions, useful in various terminal configurations:

- Subscriber Awake (using SIP/SAW line)

- Watchdog Timer

The terminal-specific functions, STCR, SPCR, and CIXR registers (see Detailed Register Description), make it possible to generate a Reset signal as well as the appropriate interrupt in the following cases:

- Power Down

- Subscriber Awake—initiated by a falling edge on the SAW line (SAW interrupt)

- —Exchange Awake—initiated by a message from Layer 1 (CIC interrupt)

- Power Up

- —Watchdog Timer—after expiration of the internal watchdog timer (WOV interrupt)

The reset pulse generated by the ISAC-S has a pulse width of 5 ms and is an active High signal. During one time period of 128 ms, the WTC1- and WTC2-bit of the ADFR register must be set consecutively in the following manner:

| Steps      | WTC1 | WTC2 |  |

|------------|------|------|--|

| <b>' 1</b> | 1    | 0    |  |

| 2          | 0    | 1    |  |

As a result, the watchdog timer is reset and restarted.

Am2085 1-171

#### **Test Functions**

The ISAC-S provides several test and diagnostic functions which can be grouped as follows:

- Closing loops in the transmission path; that is:

- loop internally inside the B-channel switching circuit (B-channel IOM loop) see B-Channel Switching)

- —loop internally at the IOM interface, with reduced timer resolution (IOM interface loop), SPCR: TLP-bit, (see Detailed Register Description)

- —loop at the analog end of the S interface (see Interrupt List)

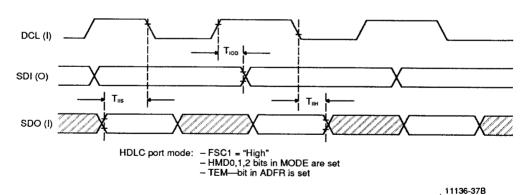

- Using the IOM interface as an HDLC port without IOM frame structure (D-channel splitting) and no Layer 1, MODE and ADFR: TEM-bit, (see Detailed Register Description)

- Sending of special test signals on the S-bus, according to the modified AMI code; that is;

- -single zeros (SSZ, 2 kHz repetition rate)

- —continuous zeros (SCZ, 96 kHz repetition rate) (see Layer 1 Functions for the ISDN Basic Access; also see Processing)

#### **DETAILED REGISTER DESCRIPTION**

The parameterization of the ISAC-S as well as transfer of data and control information between the microprocessor and ISAC-S is performed with the R- and XFIFO and two register sets (Figure 27). The two FIFOs are accessed with the addresses 00—1FH which are of equal value and are referenced to the respective actual byte in the FIFO.

The special purpose registers of the address range 20-2FH pertain to the HDLC transceiver and LAPD controller as well as to higher-ranking functions in the ISAC-S.

The serial interfaces are controlled and monitored with the register record 30–3FH.

| Register<br>Address | Read                    |                            |       | Write                     | ]                        |

|---------------------|-------------------------|----------------------------|-------|---------------------------|--------------------------|

| [1]                 | Name Description        |                            | Name  | Description               | 1                        |

| 00<br><br>1F        | RFIFO                   | Receive FIFO               |       | Transmit FIFO             | FIFO<br>Buffer           |

| 20                  | ISTA                    | Interrupt Status Register  | MASK  | Mask Register             | † <u>:</u>               |

| 21                  | STAR                    | Status Register            | CMDR  | Command Register          | 1 :                      |

| 22                  | MODE                    | MODE Register              |       |                           | 1 :                      |

| 23                  | TIMR                    |                            | Timer | Register                  | 1 ;                      |

| 24                  | EXIR                    | Extended Interrupts        | XAD1  | Transmit Address 1        | HDLC- !<br>Transceiver ! |

| 25                  | RFBC                    | Receive Frame Byte Counter | XAD2  | Transmit Address 2        | LADP-                    |

| 26                  |                         | [2]                        | SAP1  | SAPI Address 1            | Controller,              |

| 27                  | RSTA R                  | eceive Status Register     | SAP2  | SAPI Address 2            | 1 !                      |

| 28                  | TEI1                    | TEI Address 1              |       | [3]                       | 1 :                      |

| 29                  | RHCR F                  | leceive HDLC Control       | TEI2  | TEI Address 1             | 1 ;                      |

| 2A                  |                         |                            |       |                           | † <i></i>                |

| 2F                  |                         | [4]                        |       |                           |                          |

| 30                  | SPCR                    | Serial Port Control        |       |                           | † <sub>1</sub>           |

| 31                  | CIRR                    | Command/Indicate Receive   | CIXR  | Command/Indicate Transmit | <b>!</b>                 |

| 32                  | MDNR                    | Monitor Register           | •     |                           | <b>†</b> :               |

| 33                  | SSGR                    | SLD Signaling Receive      | SSGX  | SLD Signaling Transmit    | Serial                   |

| 34                  | SFCR                    | SLD Feature Contr          | ol    |                           | Interface                |

| 35                  | BCX1                    |                            | l j   |                           |                          |

| 36                  | BCX2                    |                            |       |                           |                          |

| 37                  | BCR1 B1-Channel Receive |                            | STCR  | Synchr. Transfer Control  |                          |

| 38                  | BCR2                    | 32-Channel Receive         | ADFR  | Additional Features       | 1 :                      |

| 39<br><br>3F        |                         |                            |       |                           |                          |

Notes: 1) Hexadecimal representation of ADO 7

- 2) Inverted contents of SAP1 when reading

- 3) Inverted contents of TEI1 when reading auto

- 4) Invalid address range (data value "00" when reading)

11136-027B

Figure 27. Register Address Arrangement

Am2085

For quick reference, the page numbers for all registers are listed below:

#### **Internal Events and Conditions**

| ISTA | 41 |

|------|----|

| MASK | 42 |

| EXIR | 43 |

| STAR | 44 |

#### LAPD/(HDLC) Operation Control

| CMDR | 45 |

|------|----|

| MODE | 46 |

| TIMR | 47 |

| RFBC | 48 |

| RSTA | 49 |

#### LAPD/(HDLC) Address Variables

| XAD1 | 50 |

|------|----|

| XAD2 | 51 |

| SAP1 | 51 |

| SAP2 | 52 |

| TEI1 | 52 |

| TEI2 | 53 |

#### LAPD/(HDLC) Control Data

RHCR 53

#### LAPD/(HDLC) Information Data

| RFIFO | 54 |

|-------|----|

| XFIFO | 54 |

#### Serial Interface Control

| SPCR | 55 |

|------|----|

| STCR | 56 |

| CIXR | 57 |

| CIRR | 58 |

| MONR | 58 |

| BCX1 | 59 |

| BCX2 | 59 |

| BCR1 | 60 |

| BCR2 | 60 |

| SSGX | 60 |

| SSGR | 61 |

| SFCR | 61 |

#### Special Functions

ADFR 62

1-174 Am2085

#### Internal Events and Conditions

# ISTA-Interrupt Status Register—(Read)

Value after Reset: 00H

Address: 20H

|         | 7   |     |     |     |     |     |     | 0   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Format: | RME | RPF | RSC | XPR | TIN | CIC | SIN | EXI |

| Bit Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RME      | Receive Message End The receive message is now complete. Either one complete message, shorter than 32 bytes, or the remaining part of a longer message has been received. The contents are now available in the RFIFO. The actual message length and additional information may be obtained from the RFBC and the RSTA register.                                                                                                                                                                          |

| RPF      | Receive Pool Full  A 32 byte block of a message, greater than 32 bytes has been received and is now available in the RFIFO. The message is not yet complete.                                                                                                                                                                                                                                                                                                                                              |

| RSC      | Receive Status Change (used in auto mode only) A status change in the receiver of the remote station (receiver ready/receiver not ready) has been detected, due to a received "RR","RNR" S-Frame (according to HDLC and LAPD). The current status can be read from the STAR register (RRNR-bit).                                                                                                                                                                                                          |

| XPR      | Transmit Pool Ready A data block of up to 32 bytes can be written to the XFIFO. An XPR interrupt will be generated in the following cases: after an XTF or XIF command, when one transmit pool is emptied and the frame is not yet complete after an XTF together with an XME command, when the whole transparent frame has been transmitted after an XIF together with an XME command, when the whole I-frame has been transmitted and a positive acknowledge from the remote station has been received. |

| TIN      | Timer Interrupt The internal timer and repeat counter has expired (see also TIMR register).                                                                                                                                                                                                                                                                                                                                                                                                               |

| CIC      | C/I Code Change A change in C/I code has been recognized. The same C/I code, which differs from the prior subsequent received C/I code, has been received at least twice. The actual C/I code can be read from the CIRR register.                                                                                                                                                                                                                                                                         |

| SIN      | Synchronous Transfer Register The beginning or the center of an IOM-frame has been indicated, as programmed in the STCR register.                                                                                                                                                                                                                                                                                                                                                                         |

| EXI      | Extended Interrupt This interrupt signifies that one of eight non-critical interrupts, indicated in the extended interrupt register EXIR, has been generated. The exact cause must be read from EXIR.                                                                                                                                                                                                                                                                                                     |

Note: Reading of the EXIR register by the processor clears the EXI-bit, and reading of the ISTA register clears all other bits of ISTA.

#### MASK-Mask Register-(Write)

Value after Reset: 00H (all interrupts enabled)

Address: 20H

Format: RME RPF RSC XPR TIN CIC SIN EXI

| Bit Name | Description                                                                                                                                                            |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RME      | Each bit of the MASK register relates to the corresponding bits of the ISTA register.  Each interrupt can be selectively masked by setting the respective bit in MASK. |

| EXI      | Masked interrupts are not indicated when reading ISTA. Instead, they remain internally stored and will be indicated after the respective MASK is reset.                |

Note: In the event of an extended interrupt, no interrupt request (INT = Low) will be generated with a masked EXI-bit, although this bit is set in ISTA.

1-176 Am2085

# EXIR—Extended Interrupt Register—(Read)

Value after Reset: 00H

Address: 24H

Format: XMR XDU PCE RFO SOV MOR SAW WOV

| Bit Name | Description                                                                                                                                                                                                                                                                                                                                                |