# ADSP-TS201 TigerSHARC® Processor Programming Reference

Revision 1.1, April 2005

Part Number 82-000810-01

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

### **Copyright Information**

© 2005 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

## **Trademark and Service Mark Notice**

The Analog Devices logo, Blackfin, EZ-ICE, EZ-KIT Lite, SHARC, TigerSHARC, the TigerSHARC logo, and VisualDSP++ are registered trademarks of Analog Devices, Inc.

Superscalar is a trademark of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

### PREFACE

| Purpose of This Manual xxi                    |

|-----------------------------------------------|

| Intended Audience xxi                         |

| Manual Contents xxii                          |

| What's New in This Manual xxiv                |

| Technical or Customer Support xxiv            |

| Supported Processors xxv                      |

| Product Information xxvi                      |

| MyAnalog.com xxvi                             |

| Processor Product Information xxvi            |

| Related Documents xxvii                       |

| Online Technical Documentation xxviii         |

| Accessing Documentation From VisualDSP++ xxix |

| Accessing Documentation From Windows xxix     |

| Accessing Documentation From the Web xxx      |

| Printed Manuals               | xxx  |

|-------------------------------|------|

| VisualDSP++ Documentation Set | cxxi |

| Hardware Tools Manuals        | cxxi |

| Processor Manuals             | cxxi |

| Data Sheets                   | cxxi |

| Conventions x                 | xxii |

### **INTRODUCTION**

| Processor Architecture 1                | <b>I-</b> 7 |

|-----------------------------------------|-------------|

| Compute Blocks 1-                       | 10          |

| Arithmetic Logic Unit (ALU) 1-          | -10         |

| Communications Logic Unit (CLU) 1-      | 12          |

| Multiply Accumulator (Multiplier) 1-    | 12          |

| Bit Wise Barrel Shifter (Shifter) 1-    | 13          |

| Integer Arithmetic Logic Unit (IALU) 1- | 13          |

| Program Sequencer 1-                    | 15          |

| Quad Instruction Execution 1-           | -17         |

| Relative Addresses for Relocation 1-    | 18          |

| Nested Call and Interrupt 1-            | 18          |

| Context Switching 1-                    | 18          |

| Internal Memory and Buses 1-            | 19          |

| Internal Buses 1-                       | 19          |

| Internal Transfer 1-                    | 20          |

| Data Accesses 1-                        | ·21         |

| Quad Data Access1-                      | -21         |

| Booting                                | 1-21 |

|----------------------------------------|------|

| Scalability and Multiprocessing        | 1-22 |

| Emulation and Test Support             | 1-22 |

| Instruction Line Syntax and Structure  | 1-23 |

| Instruction Notation Conventions       | 1-24 |

| Unconditional Execution Support        | 1-26 |

| Conditional Execution Support          | 1-27 |

| Instruction Parallelism Rules          | 1-27 |

| General Restriction                    | 1-38 |

| Compute Block Instruction Restrictions | 1-39 |

| IALU Instruction Restrictions          | 1-43 |

| Sequencer Instruction Restrictions     | 1-48 |

|                                        |      |

### **COMPUTE BLOCK REGISTERS**

| Register File Registers                               |

|-------------------------------------------------------|

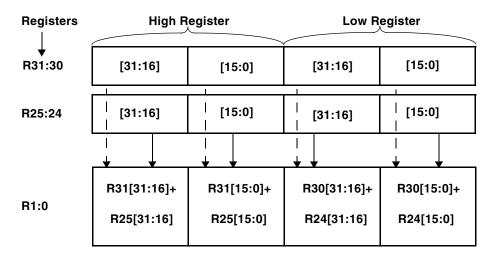

| Compute Block Selection 2-7                           |

| Register Width Selection 2-9                          |

| Operand Data Type Selection 2-10                      |

| Registers File Syntax Summary 2-12                    |

| Numeric Formats                                       |

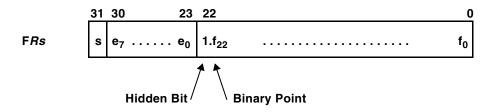

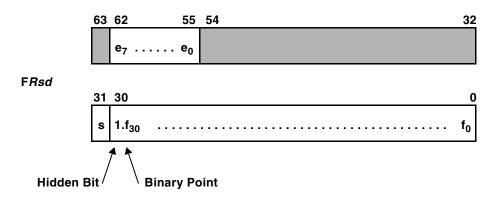

| IEEE Single-Precision Floating-Point Data Format 2-16 |

| Extended-Precision Floating-Point Format 2-19         |

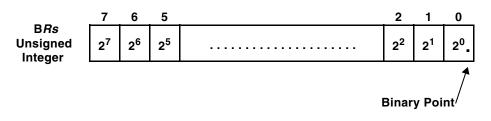

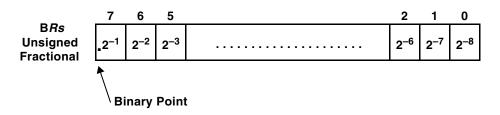

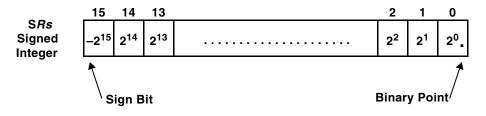

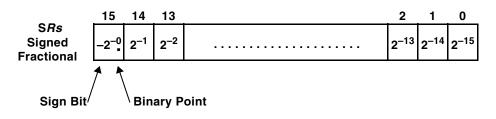

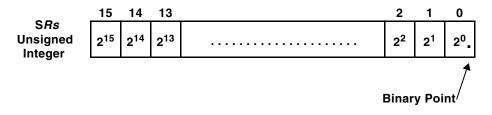

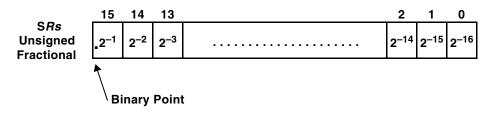

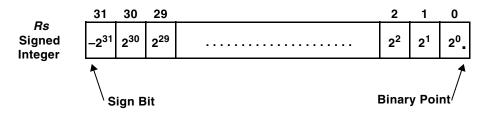

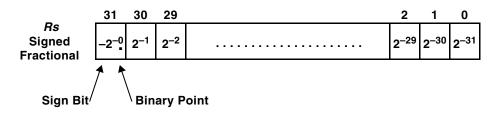

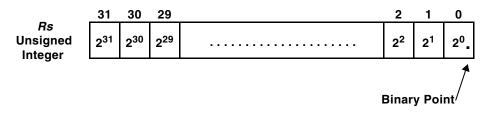

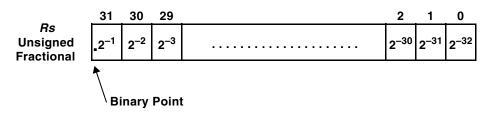

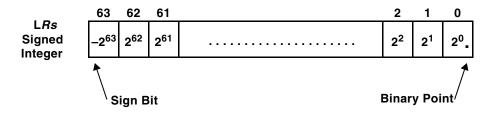

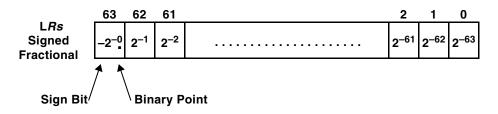

| Fixed-Point Formats                                   |

# ALU

| ALU Operations                                   |

|--------------------------------------------------|

| ALU Instruction Options 3-6                      |

| Signed/Unsigned Option 3-7                       |

| Saturation Option                                |

| Extension (ABS) Option 3-9                       |

| Truncation Option 3-9                            |

| Return Zero (MAX/MIN) Option 3-10                |

| Fractional/Integer Option 3-10                   |

| No Flag Update Option 3-11                       |

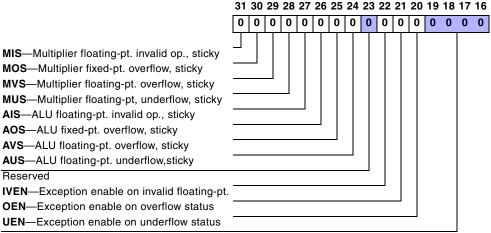

| ALU Execution Status 3-11                        |

| AZ – ALU Zero                                    |

| AN – ALU Negative 3-13                           |

| AV – ALU Overflow                                |

| AI – ALU Invalid 3-14                            |

| AC – ALU Carry 3-15                              |

| ALU Execution Conditions 3-15                    |

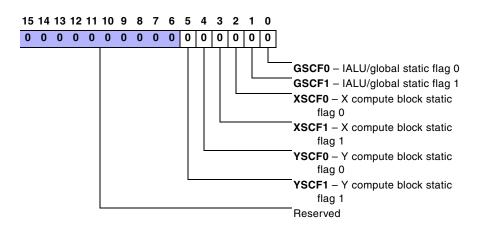

| ALU Static Flags                                 |

| ALU Examples                                     |

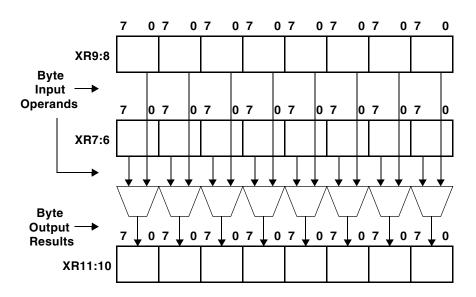

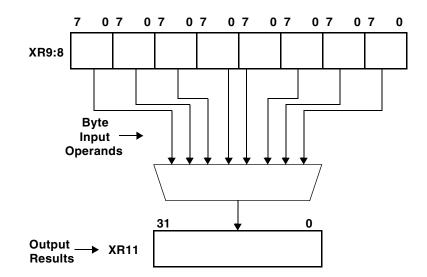

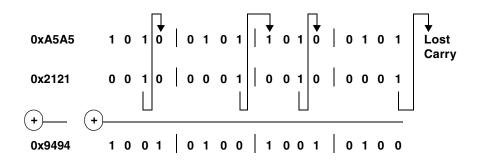

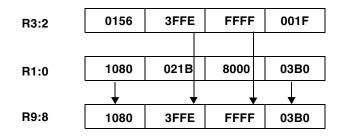

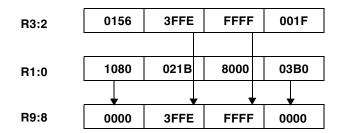

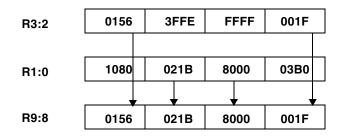

| Example Parallel Addition of Byte Data 3-18      |

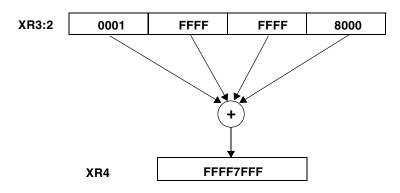

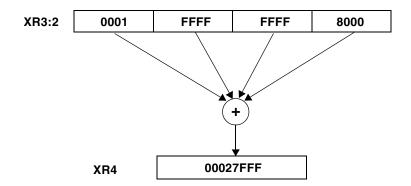

| Example Sideways Sum of Byte Data 3-19           |

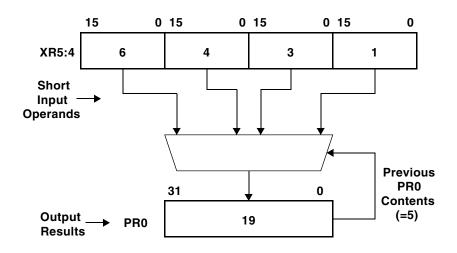

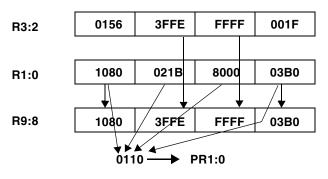

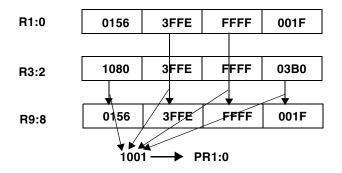

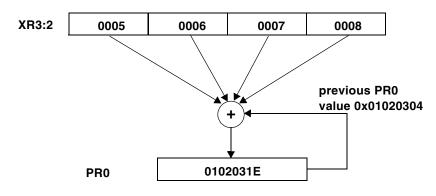

| Example Parallel Result (PR) Register Usage 3-20 |

| ALU Instruction Summary                          |

# CLU

| CLU Operations 4-4                                                              |

|---------------------------------------------------------------------------------|

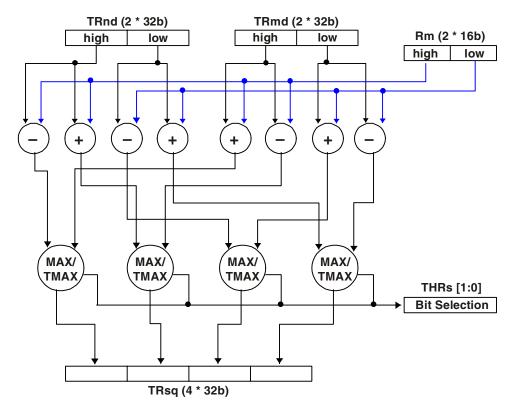

| TMAX Function                                                                   |

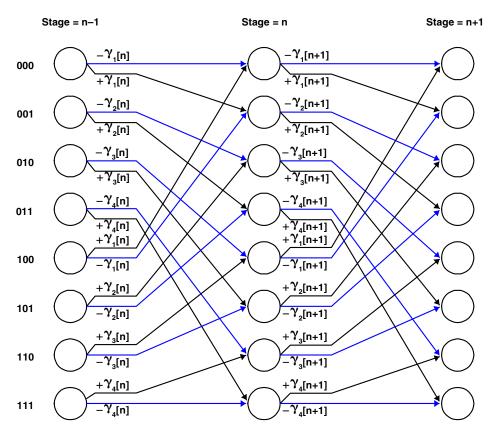

| Trellis Function                                                                |

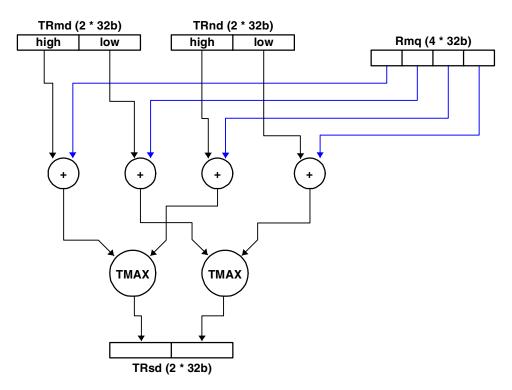

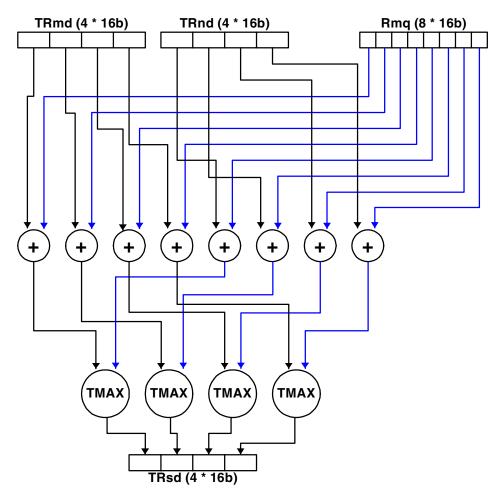

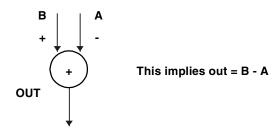

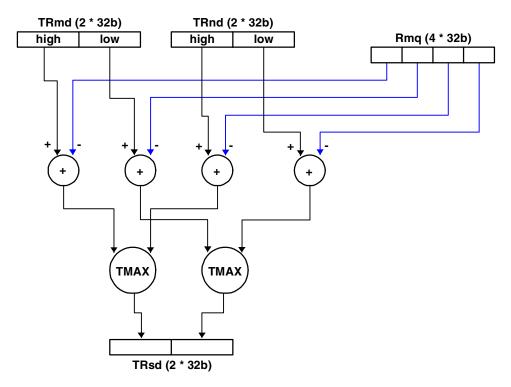

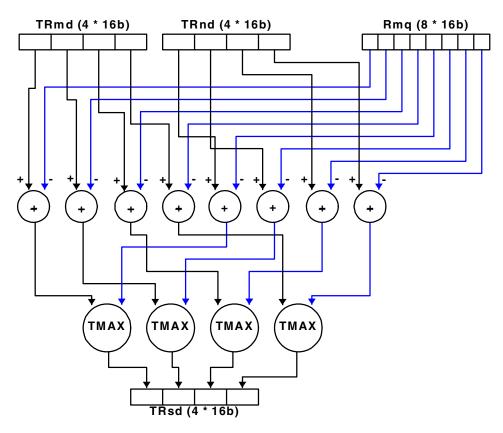

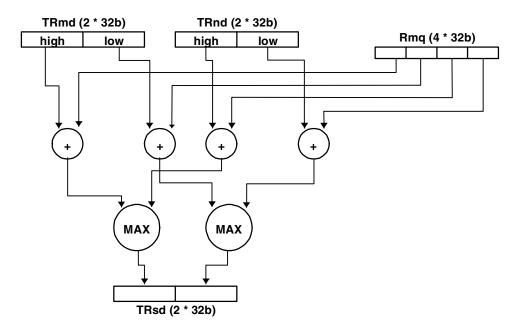

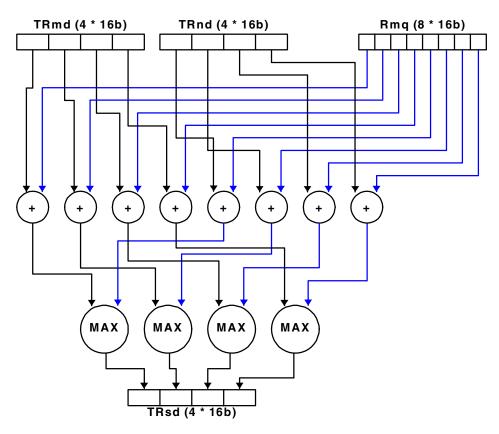

| Trellis Function of the Form<br>STRsd = TMAX(TRmd + Rmq_h, TRnd + Rmq_l) ; 4-10 |

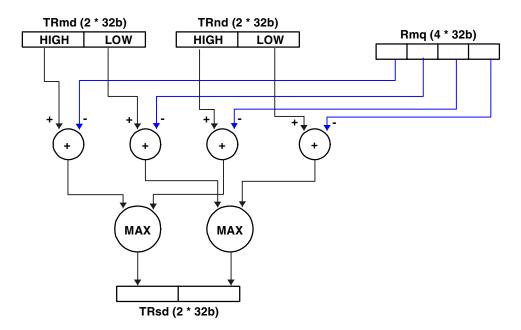

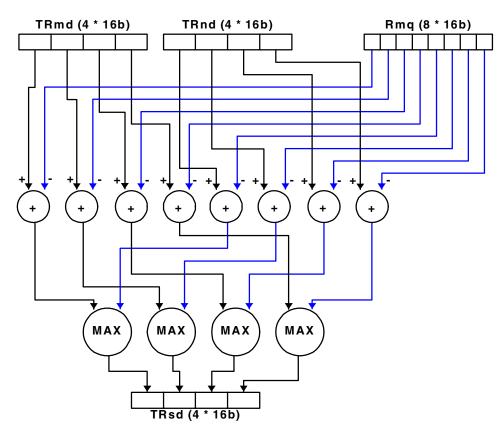

| Trellis Function of the Form<br>STRsd = TMAX(TRmd - Rmq_h, TRnd - Rmq_l) ; 4-13 |

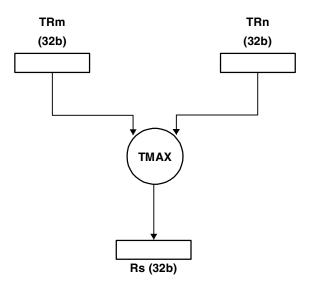

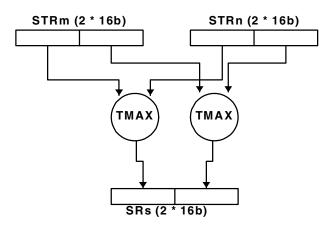

| Trellis Function of the Form<br>SRs = TMAX(TRm, TRn) ;                          |

| Trellis Function of the Form<br>STRsd = MAX(TRmd + Rmq_h, TRnd + Rmq_l) ; 4-18  |

| Trellis Function of the Form<br>STRsd = MAX(TRmd - Rmq_h, TRnd - Rmq_l) ; 4-20  |

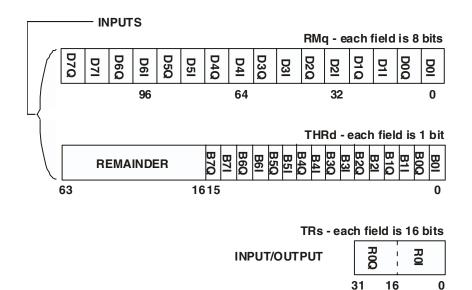

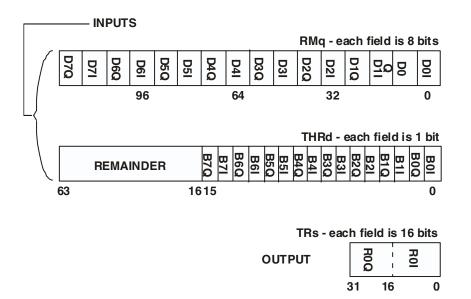

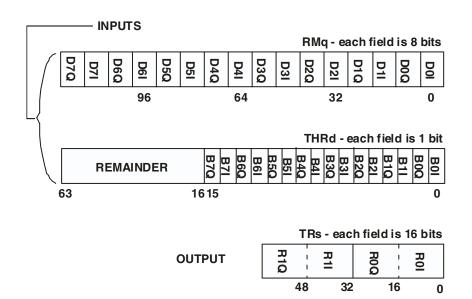

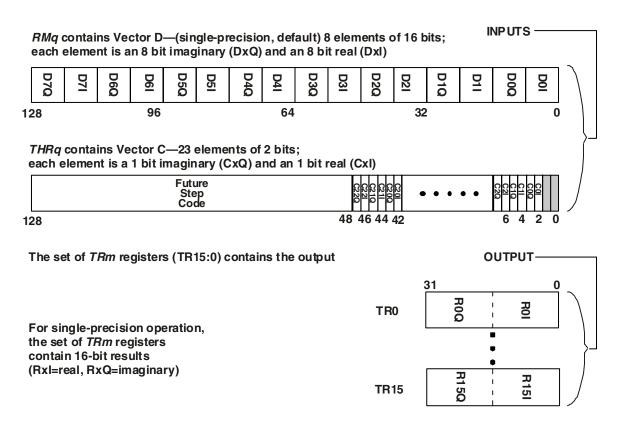

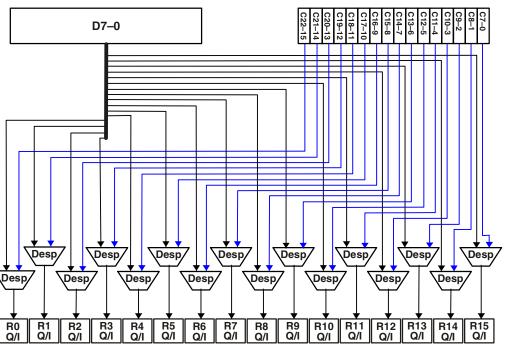

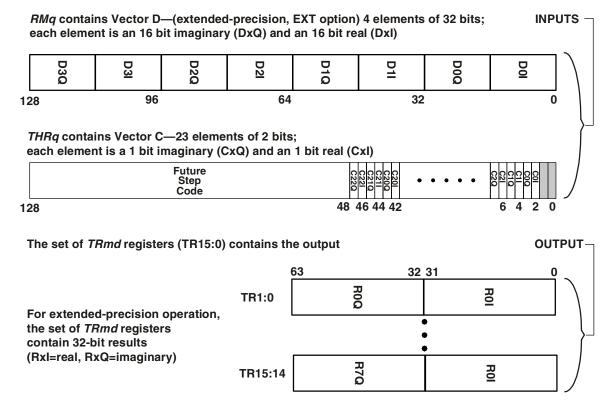

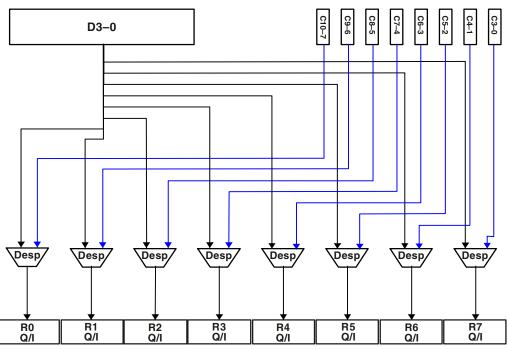

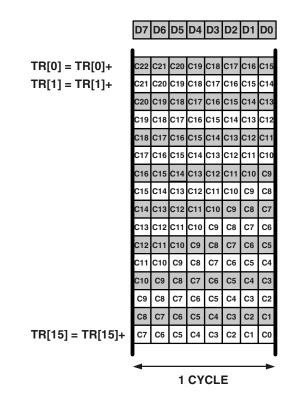

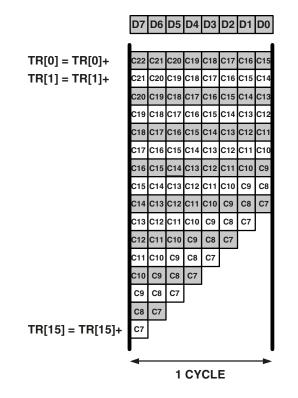

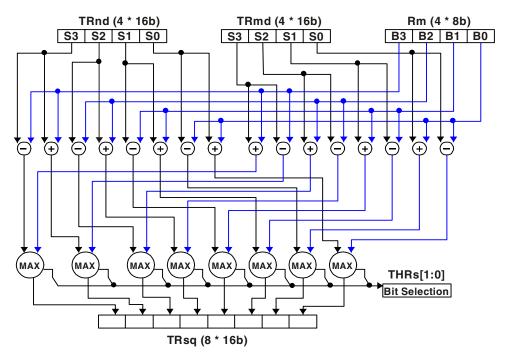

| Despread Function 4-22                                                          |

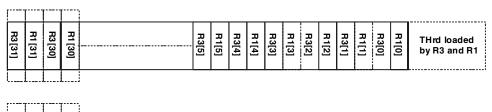

| Despread Function of the Form<br>TRs += DESPREAD (Rmq, THRd) ;                  |

| Despread Function of the Form<br>Rs = TRs, TRs = DESPREAD (Rmq, THRd) ; 4-26    |

| Despread Function of the Form<br>Rsd = TRsd, TRsd = DESPREAD (Rmq, THRd) ; 4-28 |

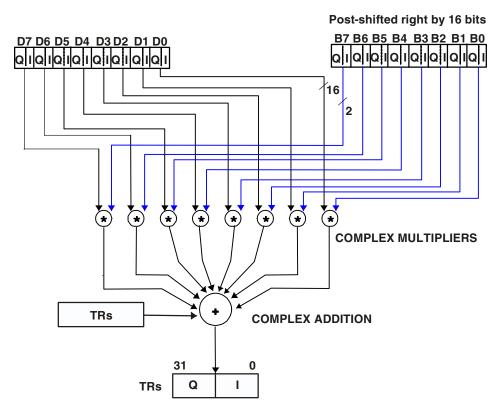

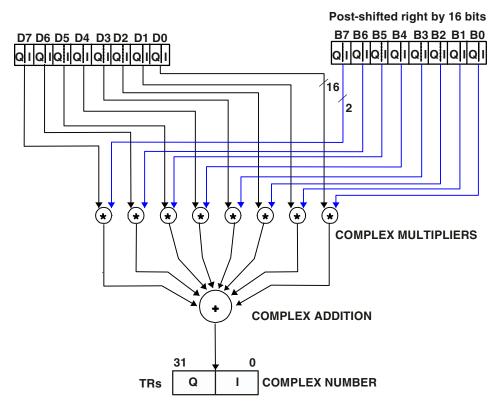

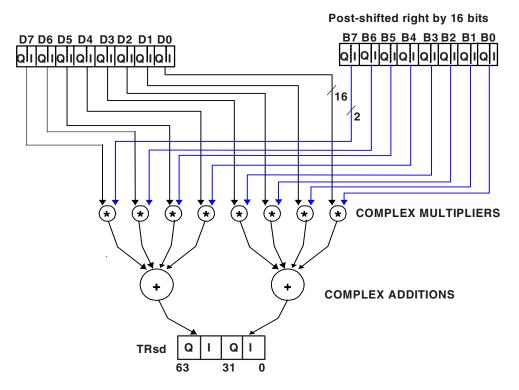

| Cross Correlations Function 4-30                                                |

| Add/Compare/Select Function 4-39                                                |

| CLU Instruction Options 4-41                                                    |

| CLU Execution Status 4-42                                                       |

| CLU Examples                              | 4-43 |

|-------------------------------------------|------|

| CLU Instruction Summary                   | 4-46 |

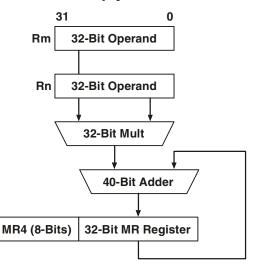

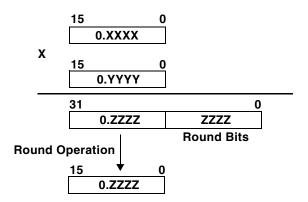

| MULTIPLIER                                |      |

| Multiplier Operations                     | 5-5  |

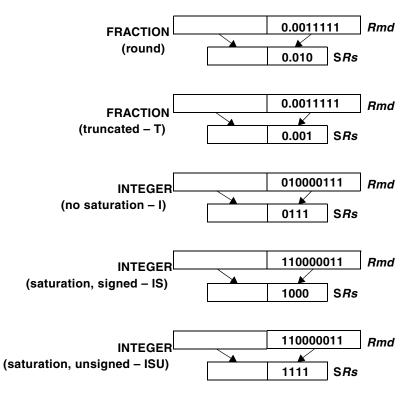

| Multiplier Instruction Options            | 5-11 |

| Signed/Unsigned Option                    | 5-12 |

| Fractional/Integer Option                 | 5-13 |

| Saturation Option                         | 5-13 |

| Truncation Option                         | 5-15 |

| Clear/Round Option                        | 5-17 |

| Complex Conjugate Option                  | 5-19 |

| No Flag Update Option                     | 5-19 |

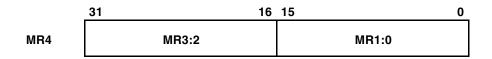

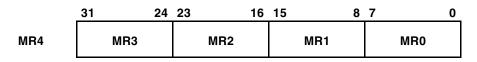

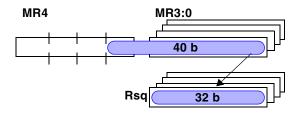

| Multiplier Result Overflow (MR4) Register | 5-19 |

| Multiplier Execution Status               | 5-20 |

| Multiplier Execution Conditions           | 5-22 |

| Multiplier Static Flags                   | 5-23 |

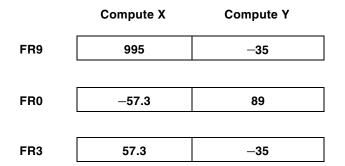

| Multiplier Examples                       | 5-24 |

| Multiplier Instruction Summary            | 5-26 |

| SHIFTER                                   |      |

| Shifter Operations                        | 6-4  |

| Logical Shift Operation                   | 6-6  |

| Arithmetic Shift Operation                | 6-7  |

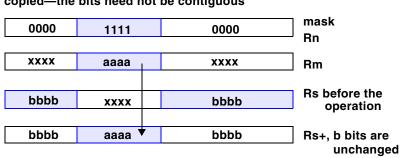

| Bit Manipulation Operations               | 6-8  |

|                                           |      |

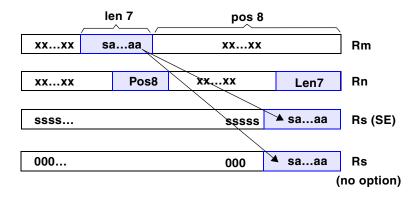

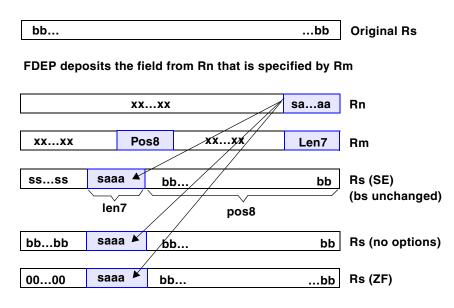

| Bit Field Manipulation Operations  | 6-9  |

|------------------------------------|------|

| Bit Field Analysis Operations      | 6-12 |

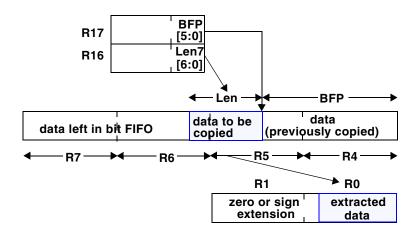

| Bit Stream Manipulation Operations | 6-12 |

| Shifter Instruction Options        | 6-17 |

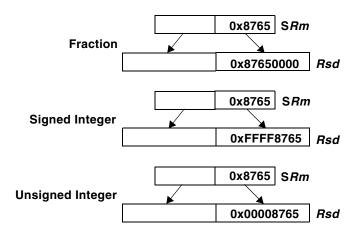

| Sign-Extended Option               | 6-18 |

| Zero-Filled Option                 | 6-18 |

| No Flag Update Option              | 6-18 |

| Shifter Execution Status           | 6-18 |

| Shifter Execution Conditions       | 6-19 |

| Shifter Static Flags               | 6-20 |

| Shifter Examples                   | 6-20 |

| Shifter Instruction Summary        | 6-22 |

|                                    |      |

# IALU

| IALU Operations                                | 7-6  |

|------------------------------------------------|------|

| IALU Integer (Arithmetic and Logic) Operations | 7-6  |

| IALU Instruction Options                       | 7-7  |

| IALU Data Types                                | 7-8  |

| Signed/Unsigned Option                         | 7-8  |

| Circular Buffer Option                         | 7-8  |

| Bit Reverse Option                             | 7-9  |

| Computed Jump Option                           | 7-10 |

| No Flag Update Option                          | 7-10 |

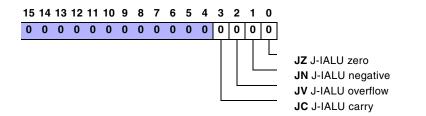

| IALU Execution Status                            | 7-10 |

|--------------------------------------------------|------|

| JZ/KZ–IALU Zero                                  | 7-11 |

| JN/KN–IALU Negative                              | 7-12 |

| JV/KV–IALU Overflow                              | 7-12 |

| JC/KC–IALU Carry                                 | 7-12 |

| IALU Execution Conditions                        | 7-13 |

| IALU Static Flags                                | 7-14 |

| IALU Load, Store, and Transfer Operations        | 7-14 |

| Direct and Indirect Addressing                   | 7-15 |

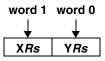

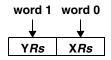

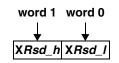

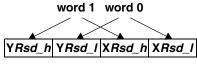

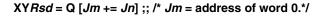

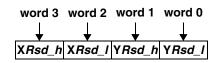

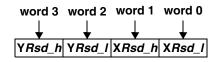

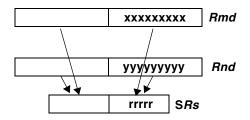

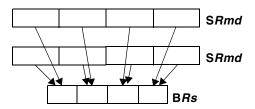

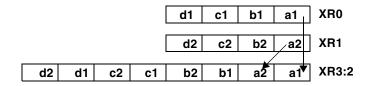

| Normal, Merged, and Broadcast Memory Accesses    | 7-17 |

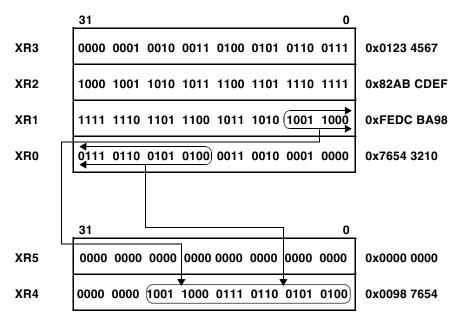

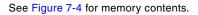

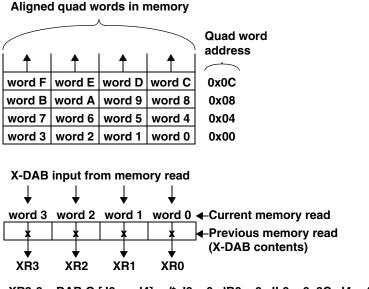

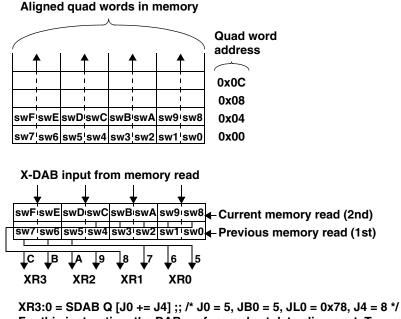

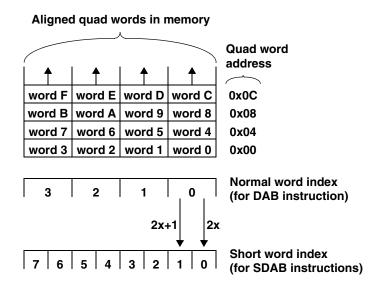

| Data Alignment Buffer (DAB) Accesses             | 7-26 |

| Data Alignment Buffer (DAB) Accesses With Offset | 7-30 |

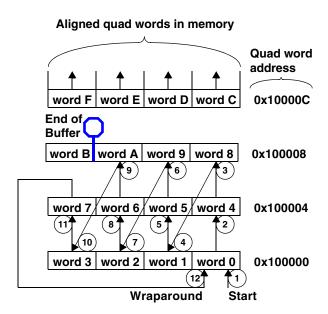

| Circular Buffer Addressing                       | 7-33 |

| Bit Reverse Addressing                           | 7-38 |

| Universal Register Transfer Operations           | 7-42 |

| Immediate Extension Operations                   | 7-42 |

| IALU Examples                                    | 7-43 |

| IALU Instruction Summary                         | 7-47 |

# PROGRAM SEQUENCER

| Sequencer Operations   | 8-8  |

|------------------------|------|

| Conditional Execution  | 8-14 |

| Branching Execution    | 8-19 |

| Looping Execution      | 8-22 |

| Interrupting Execution | 8-26 |

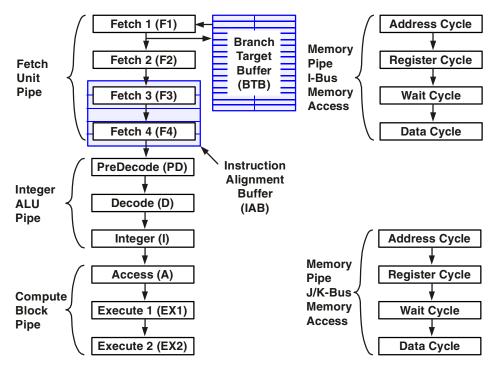

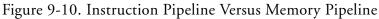

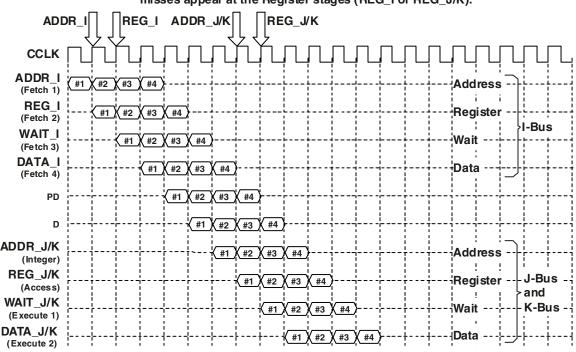

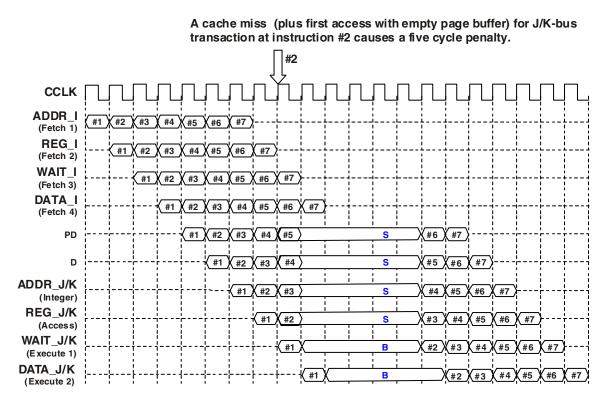

| Instruction Pipeline Operations                        | 4 |

|--------------------------------------------------------|---|

| Instruction Alignment Buffer (IAB) 8-39                | 9 |

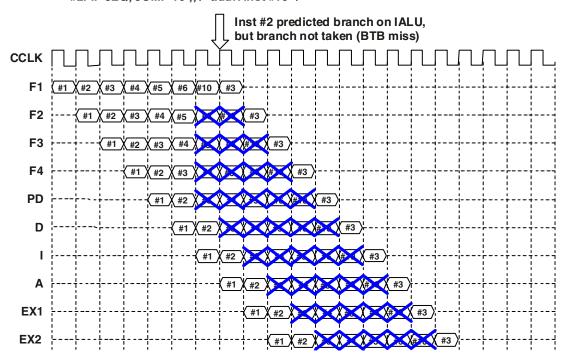

| Branch Target Buffer (BTB) 8-4                         | 2 |

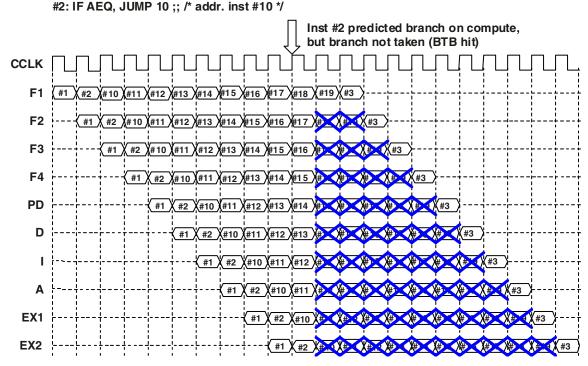

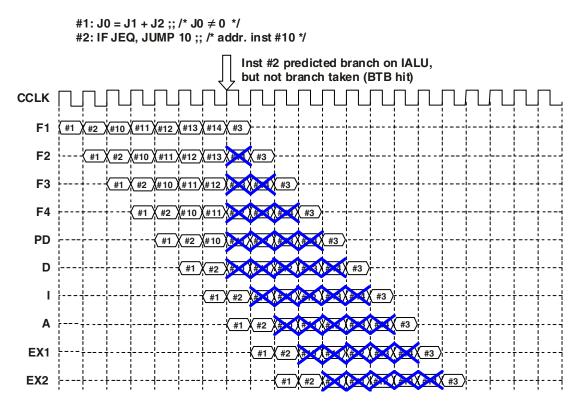

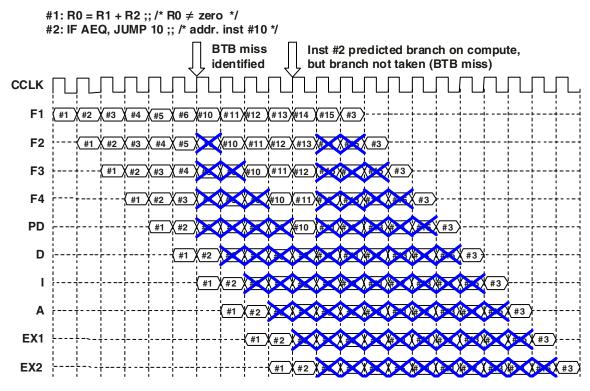

| Conditional Branch Effects on Pipeline 8-5.            | 3 |

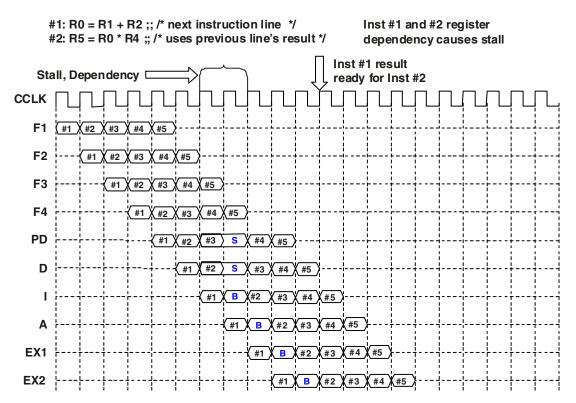

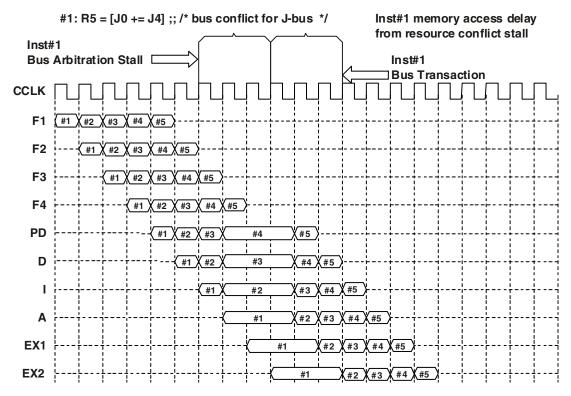

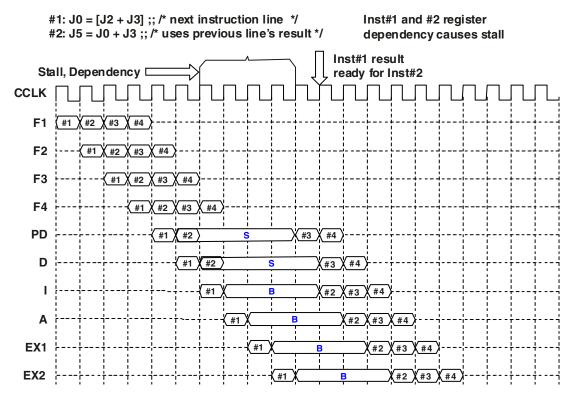

| Dependency and Resource Effects on Pipeline            | 4 |

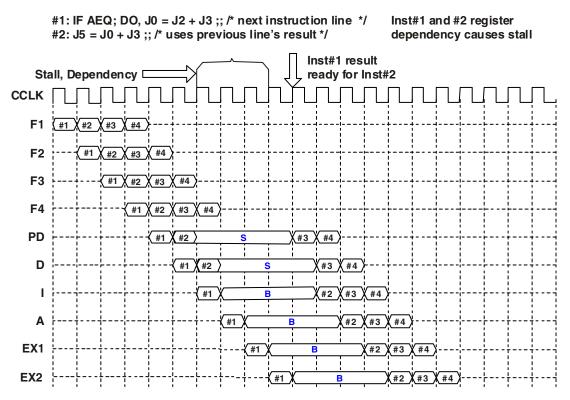

| Stall From Compute Block Dependency 8-7                | 7 |

| Stall From Bus Conflict 8-80                           | 0 |

| Stall From Compute Block Load Dependency               | 3 |

| Stall From IALU Load Dependency 8-8-                   | 4 |

| Stall From Load (From External Memory) Dependency 8-8- | 4 |

| Stall From Conditional IALU Load Dependency            | 5 |

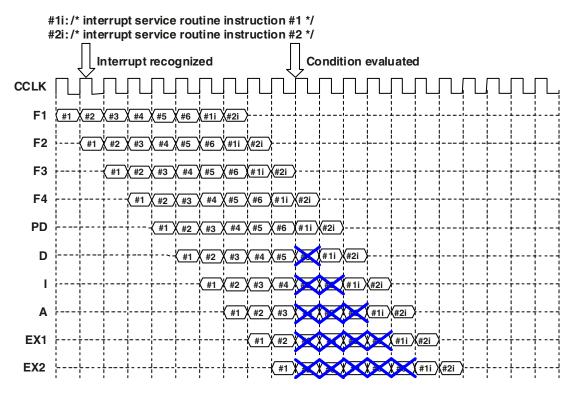

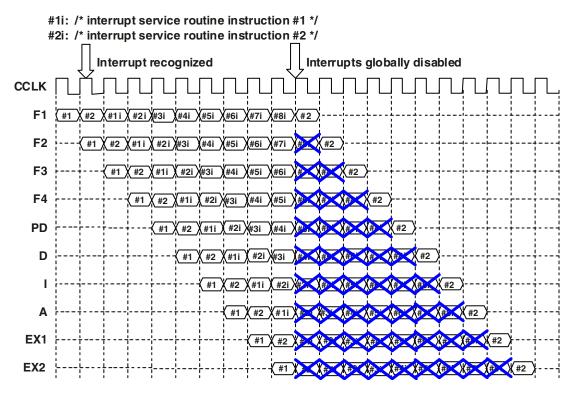

| Interrupt Effects on Pipeline 8-80                     | 6 |

| Interrupt During Conditional Instruction 8-88          | 8 |

| Interrupt During Interrupt Disable Instruction         | 0 |

| Exception Effects on Pipeline 8-9                      | 0 |

| Sequencer Examples                                     | 2 |

| Sequencer Instruction Summary                          | 7 |

### MEMORY AND BUSES

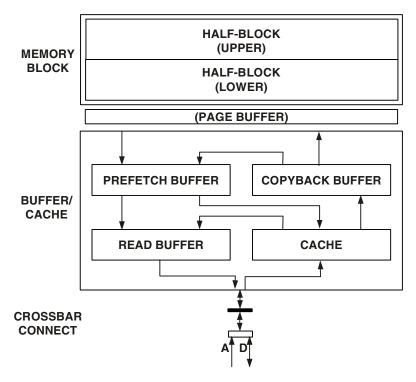

| Memory Block Physical Structure |      |

|---------------------------------|------|

| Prefetch Buffer                 |      |

| Read Buffer                     | 9-10 |

| Cache                           | 9-11 |

| Copyback Buffer                 | 9-11 |

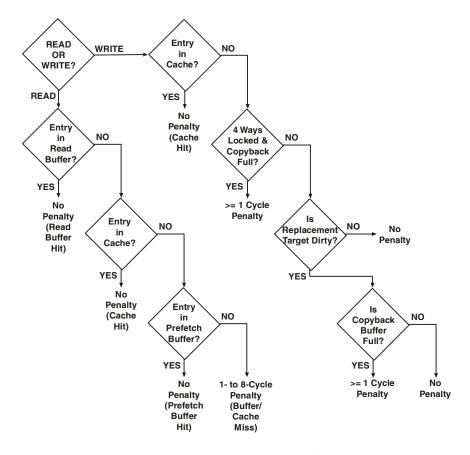

| Buffer   | /Cache Hit                            | 9-12 |

|----------|---------------------------------------|------|

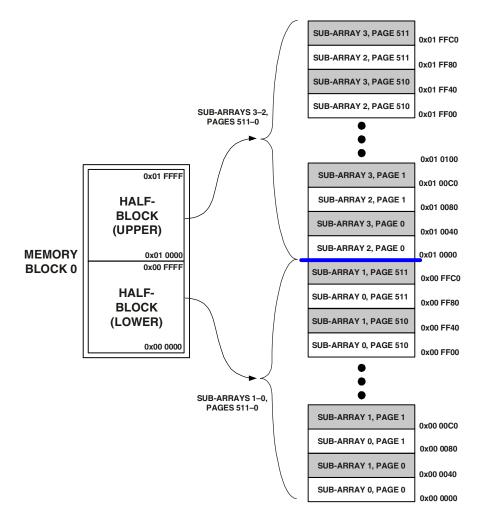

| Memo     | ry Block Terms, Sizes, and Addressing | 9-13 |

| Memory B | Block Logical Organization            | 9-14 |

| Block    |                                       | 9-15 |

| Half-B   | Block                                 | 9-15 |

| Sub-A    | ггау                                  | 9-15 |

| Page     |                                       | 9-16 |

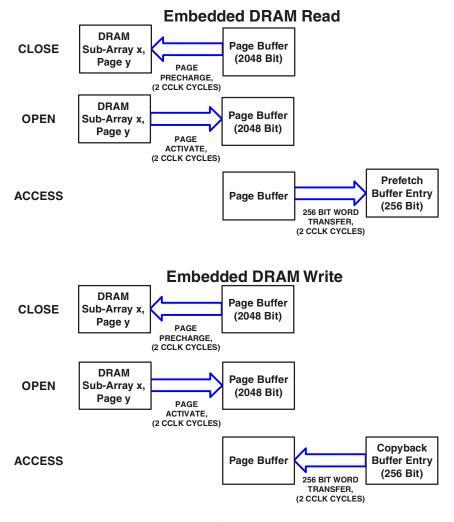

| Memory B | Block Accesses                        | 9-16 |

| Activa   | te                                    | 9-18 |

| Precha   | rge                                   | 9-18 |

| Refres   | h                                     | 9-19 |

| Memo     | ry System Controls and Status         | 9-19 |

| Cache    | Operation                             | 9-25 |

| Data A   | Access on Read                        | 9-30 |

| Data A   | Access on Write                       | 9-32 |

| Memo     | ry Bus Arbitration                    | 9-33 |

| Memory F | Pipeline                              | 9-35 |

| Cache    | Miss Transaction                      | 9-38 |

| Cache    | Miss (With No Buffer Hit) Transaction | 9-38 |

| Prefeto  | ch Sequence                           | 9-41 |

| Prefeto  | ch Sequence Interrupted               | 9-43 |

| Memo     | ry Access Penalty Summary             | 9-44 |

| Memory Programming Guidelines               | 9-46 |

|---------------------------------------------|------|

| Sequential Access Policy                    | 9-48 |

| Local Access Policy                         | 9-49 |

| Cache Usage Policy                          | 9-50 |

| Cache Enable (After Reset and Boot)         | 9-50 |

| Cache Disable                               | 9-50 |

| Read and Write Cacheability                 | 9-51 |

| Instruction Caching                         | 9-51 |

| Double Sequence Flow                        | 9-52 |

| Block Orientation                           | 9-52 |

| Memory Access Examples                      | 9-53 |

| Memory System Command Summary               | 9-56 |

| Memory System Commands                      | 9-58 |

| Refresh Rate Select                         | 9-60 |

| Cache Enable                                | 9-62 |

| Cache Disable                               | 9-63 |

| Set Bus/Cacheability (for Bus Transactions) | 9-64 |

| Cache Lock Start                            | 9-68 |

| Cache Lock End                              | 9-69 |

| Cache Initialize (From Memory)              | 9-70 |

| Cache Copyback (to Memory)                  | 9-74 |

| Cache Invalidate                            | 9-78 |

## **INSTRUCTION SET**

| ALU Instructions                                   | . 10-2 |

|----------------------------------------------------|--------|

| Add/Subtract                                       | . 10-3 |

| Add/Subtract With Carry/Borrow                     | . 10-6 |

| Add/Subtract With Divide by Two                    | . 10-9 |

| Absolute Value/Absolute Value of Sum or Difference | 10-11  |

| Two's Complement                                   | 10-14  |

| Maximum/Minimum                                    | 10-15  |

| Viterbi Maximum/Minimum                            | 10-18  |

| Increment/Decrement                                | 10-21  |

| Compare                                            | 10-23  |

| Clip                                               | 10-25  |

| Sideways Sum                                       | 10-27  |

| Ones Counting                                      | 10-29  |

| Load/Transfer PR (Parallel Result) Register        | 10-30  |

| Bit FIFO Increment                                 | 10-31  |

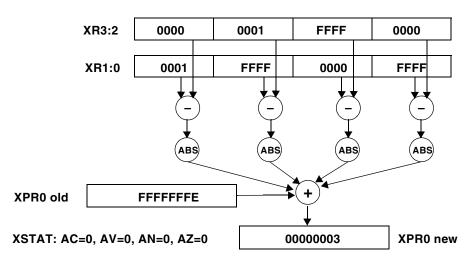

| Absolute Value With Parallel Accumulate            | 10-33  |

| Sideways Sum With Parallel Accumulate              | 10-35  |

| Add/Subtract (Dual Operation)                      | 10-37  |

| Pass                                               | 10-38  |

| Logical AND/AND NOT/OR/XOR/NOT                     | 10-39  |

| Expand                                             | 10-41  |

| Compact                                            | 10-46  |

| Merge                                              | 10-50  |

| Permute (Byte Word)                                                     | 10-52 |

|-------------------------------------------------------------------------|-------|

| Permute (Short Word)                                                    | 10-54 |

| Add/Subtract (Floating-Point)                                           | 10-56 |

| Add/Subtract With Divide by Two (Floating-Point)                        | 10-58 |

| Maximum/Minimum (Floating-Point)                                        | 10-60 |

| Absolute Value/<br>Absolute Value of Sum or Difference (Floating-Point) | 10-62 |

| Complement Sign (Floating-Point)                                        | 10-65 |

| Compare (Floating-Point)                                                | 10-67 |

| Floating- to Fixed-Point Conversion                                     | 10-69 |

| Fixed- to Floating-Point Conversion                                     | 10-71 |

| Floating-Point Normal to Extended Word Conversion                       | 10-73 |

| Floating-Point Extended to Normal Word Conversion                       | 10-75 |

| Clip (Floating-Point)                                                   | 10-77 |

| Copysign (Floating-Point)                                               | 10-79 |

| Scale (Floating-Point)                                                  | 10-81 |

| Pass (Floating-Point)                                                   | 10-83 |

| Reciprocal (Floating-Point)                                             | 10-85 |

| Reciprocal Square Root (Floating-Point)                                 | 10-87 |

| Mantissa (Floating-Point)                                               | 10-90 |

| Logarithm (Floating-Point)                                              | 10-92 |

| Add/Subtract (Dual Operation, Floating-Point)                           | 10-94 |

| CLU Instructions                                                        | 10-96 |

| Trellis Maximum (CLU)                                                   | 10-97 |

| Maximum (CLU)                                                           | 10-98 |

| Transfer TR (Trellis), THR (Trellis History), or<br>CMCTL (Communications Control) Registers | . 10-99 |

|----------------------------------------------------------------------------------------------|---------|

| Despread With Transfer Trellis Register<br>(Dual Operation, CLU)                             | 10-101  |

| Cross Correlations With Transfer Trellis Register<br>(Dual Operation, CLU)                   | 10-103  |

| Add/Compare/Select (CLU)                                                                     | 10-105  |

| Multiplier Instructions                                                                      | 10-107  |

| Multiply (Normal Word)                                                                       | 10-108  |

| Multiply-Accumulate (Normal Word)                                                            | 10-111  |

| Multiply-Accumulate With Transfer MR Register<br>(Dual Operation, Normal Word)               | 10-117  |

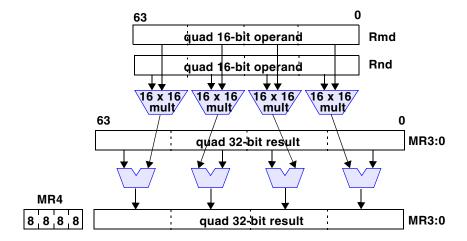

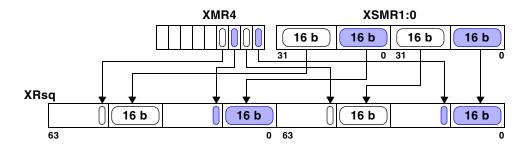

| Multiply (Quad-Short Word)                                                                   | 10-124  |

| Multiply-Accumulate (Quad-Short Word)                                                        | 10-127  |

| Multiply-Accumulate With Transfer MR Register<br>(Dual Operation, Quad-Short Word)           | 10-133  |

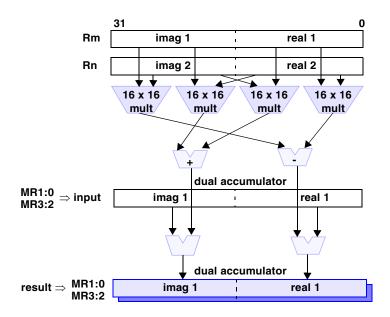

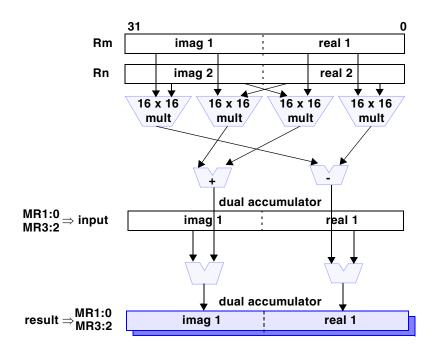

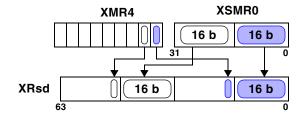

| Complex Multiply-Accumulate (Short Word)                                                     | 10-139  |

| Complex Multiply-Accumulate With Transfer MR Register<br>(Dual Operation, Short Word)        | 10-143  |

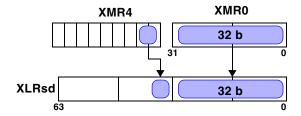

| Multiply (Floating-Point, Normal/Extended Word)                                              | 10-150  |

| Load/Transfer MR (Multiplier Result) Register                                                | 10-152  |

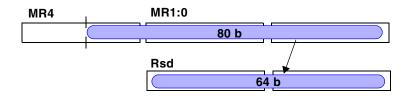

| Extract Words From MR (Multiplier Result) Register                                           | 10-160  |

| Compact MR (Multiplier Result) Register                                                      | 10-165  |

| Shifter Instructions                                                                         | 10-170  |

| Arithmetic/Logical Shift                                                                     | 10-171  |

| Rotate                                                                                       | 10-174  |

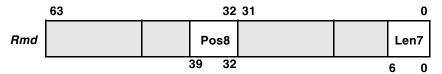

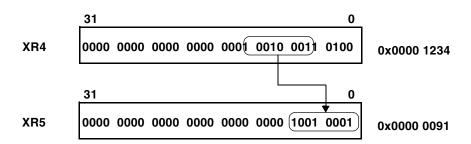

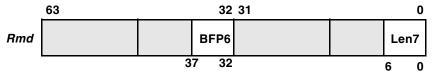

| Field Extract                                                                                  | 10-176 |

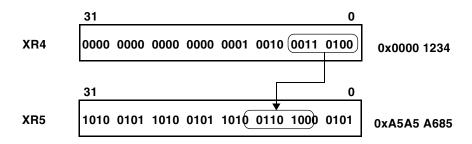

|------------------------------------------------------------------------------------------------|--------|

| Field Deposit                                                                                  | 10-178 |

| Field/Bit Mask                                                                                 | 10-180 |

| Get Bits                                                                                       | 10-182 |

| Put Bits                                                                                       | 10-184 |

| Bit Test                                                                                       | 10-187 |

| Bit Clear/Set/Toggle                                                                           | 10-188 |

| Extract Leading Zeros                                                                          | 10-190 |

| Extract Exponent                                                                               | 10-191 |

| Block Floating-Point                                                                           | 10-192 |

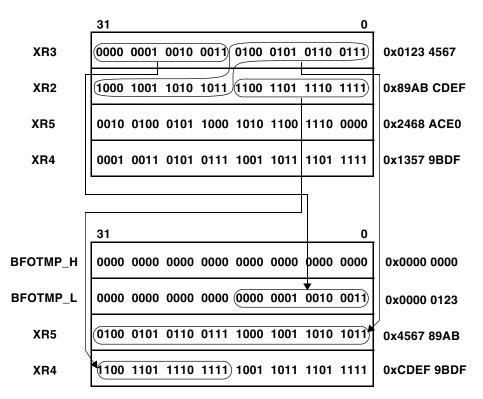

| Load/Transfer Bit FIFO Temporary (BFOTMP) Register                                             | 10-194 |

| Load/Transfer Compute Block Status (X/YSTAT) Registers                                         | 10-195 |

| Load TR (Trellis), TRH (Trellis History), or<br>CMCTL (Communications Control) Registers (CLU) | 10-196 |

| IALU (Integer) Instructions                                                                    | 10-199 |

| Add/Subtract (Integer)                                                                         | 10-201 |

| Add/Subtract With Carry/Borrow (Integer)                                                       | 10-203 |

| Add/Subtract With Divide by Two (Integer)                                                      | 10-205 |

| Compare (Integer)                                                                              | 10-207 |

| Maximum/Minimum (Integer)                                                                      | 10-209 |

| Absolute Value (Integer)                                                                       | 10-211 |

| Logical AND/AND NOT/OR/XOR/NOT (Integer)                                                       | 10-213 |

| Arithmetic Shift/Logical Shift (Integer)                                                       | 10-215 |

| Left Rotate/Right Rotate (Integer)                                                             | 10-217 |

| IALU (Load/Store/Transfer) Instructions                                                        | 10-218 |

| Load Ureg (Universal) Register (Data Addressing)               | 10-220 |

|----------------------------------------------------------------|--------|

| Store Ureg (Universal) Register (Data Addressing)              | 10-222 |

| Load Dreg (Data) Register With DAB/SDAB<br>(Data Addressing)   | 10-223 |

| Load Dreg (Data) Register With DAB Offset<br>(Data Addressing) | 10-225 |

| Store Dreg (Data) Register (Data Addressing)                   | 10-227 |

| Transfer Ureg (Universal) Register                             | 10-229 |

| Sequencer Instructions                                         | 10-232 |

| Jump/Call                                                      | 10-234 |

| Computed Jump/Call                                             | 10-236 |

| Return (From Interrupt)                                        | 10-238 |

| Reduce (Interrupt to Subroutine)                               | 10-240 |

| If – Do (Conditional Execution)                                | 10-241 |

| If – Else (Conditional Sequencing and Execution)               | 10-242 |

| Load Condition Into Static Condition Flag                      | 10-243 |

| Idle                                                           | 10-244 |

| BTB Enable/Disable                                             | 10-245 |

| BTB Lock/End Lock                                              | 10-246 |

| BTB Invalid                                                    | 10-247 |

| Trap                                                           | 10-248 |

| Emulator Trap                                                  | 10-249 |

| No Operation                                                   | 10-250 |

# QUICK REFERENCE

| ALU Quick Reference          | A-2  |

|------------------------------|------|

| CLU Quick Reference          | A-6  |

| Multiplier Quick Reference   | A-7  |

| Shifter Quick Reference      | A-9  |

| IALU Quick Reference         | A-11 |

| Sequencer Quick Reference    | A-14 |

| Memory/Cache Quick Reference | A-16 |

## **REGISTER/BIT DEFINITIONS**

## **INSTRUCTION DECODE**

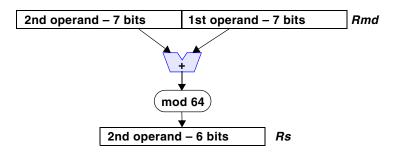

| C-1  |

|------|

| C-3  |

| C-5  |

| C-5  |

| C-7  |

| C-10 |

| C-12 |

| C-15 |

|      |

| Shifter Instructions                                          | . C-19 |

|---------------------------------------------------------------|--------|

| Single Normal Word Operands and Single Register               | . C-20 |

| Single Long or Dual Normal Word Operands and<br>Dual Register | . C-20 |

| Short or Bte Operands and Single or Dual Registers            | . C-22 |

| Single Operand                                                | . C-23 |

| CLU Registers                                                 | . C-25 |

| IALU Instructions                                             | . C-26 |

| IALU (Integer) Instruction Format                             | . C-26 |

| IALU Move Instruction Format                                  | . C-29 |

| IALU Load Data Instruction Format                             | . C-31 |

| IALU Load/Store Instruction Format                            | . C-32 |

| IALU Immediate Extension Format                               | . C-37 |

| Sequencer Instruction Format                                  | . C-38 |

| Sequencer Direct Jump/Call Instruction Format                 | . C-38 |

| Sequencer Indirect Jump Instruction Format                    | . C-40 |

| Condition Codes                                               | . C-43 |

| Compute Block Conditions                                      | . C-43 |

| IALU Conditions                                               | . C-44 |

| Sequencer and External Conditions                             | . C-45 |

| Sequencer Immediate Extension Format                          | . C-45 |

| Miscellaneous Instruction Format                              | . C-46 |

| GLOSSARY                                                      |        |

# INDEX

# PREFACE

Thank you for purchasing and developing systems using TigerSHARC® processors from Analog Devices.

# **Purpose of This Manual**

The ADSP-TS201 TigerSHARC Processor Programming Reference contains information about the DSP architecture and DSP assembly language for TigerSHARC processors. These are 32-bit, fixed- and floating-point digital signal processors from Analog Devices for use in computing, communications, and consumer applications.

The manual provides information on how assembly instructions execute on the TigerSHARC processor's architecture along with reference information about DSP operations.

# **Intended Audience**

The primary audience for this manual is a programmer who is familiar with Analog Devices processors. This manual assumes that the audience has a working knowledge of the appropriate processor architecture and instruction set. Programmers who are unfamiliar with Analog Devices processors can use this manual, but should supplement it with other texts (such as the appropriate hardware reference manuals and data sheets) that describe your target architecture.

# **Manual Contents**

The manual consists of:

• Chapter 1, Introduction

Provides a general description of the DSP architecture, instruction slot/line syntax, and instruction parallelism rules.

- Chapter 2, Compute Block Registers Provides a description of the compute block register file, register naming syntax, and numeric formats.

- Chapter 3, ALU

Provides a description of the arithmetic logic unit (ALU) operation, includes ALU instruction examples, and provides the ALU instruction summary.

• Chapter 4, CLU

Provides a description of the communications logic unit (CLU) operation, includes CLU instruction examples, and provides the CLU instruction summary.

• Chapter 5, Multiplier

Provides a description of the multiply-accumulator (multiplier) operation, includes multiplier instruction examples, and provides the multiplier instruction summary.

• Chapter 6, Shifter

Provides a description of the bit wise, barrel shifter (shifter) operation, includes shifter instruction examples, and provides the shifter instruction summary.

• Chapter 7, IALU

Provides a description of the integer arithmetic logic unit (IALU) and data alignment buffer (DAB) operation, includes IALU instruction examples, and provides the IALU instruction summary.

- Chapter 8, Program Sequencer Provides a description of the program sequencer operation, the instruction alignment buffer (IAB), the branch target buffer (BTB), and the instruction pipeline. This chapter also includes a program sequencer instruction summary.

- Chapter 9, Memory and Buses Provides a description of the internal embedded DRAM memory system (memory blocks, buffers, and cache) and internal busses. This chapter also includes a memory system command summary.

- Chapter 10, Instruction Set Describes the ADSP-TS201 processor instruction set in detail, starting with an overview of the instruction line and instruction types.

- Appendix A, Quick Reference Contains a concise description of the ADSP-TS201 processor assembly language. It is intended to be used as an assembly programming reference.

- Appendix B, Register/Bit Definitions Provides register and bit name definitions to be used in ADSP-TS201 processor programs.

- Appendix C, Instruction Decode Identifies operation codes (opcodes) for instructions. Use this chapter to learn how to construct opcodes.

This programming reference is a companion document to the ADSP-TS201 TigerSHARC Processor Hardware Reference.

# What's New in This Manual

Revision 1.1 of the ADSP-TS201 TigerSHARC Processor Programming Reference corrects all known document errata issues. The changes include updates to the e-mail contact addresses, the European fax number, and the FTP address. Also, the SQSTAT register's bit definitions have been corrected in the DEFTS201.H file. (See Listing B-1 on page B-1.)

# **Technical or Customer Support**

You can reach Analog Devices, Inc. Customer Support in the following ways:

- Visit the Embedded Processing and DSP products Web site at http://www.analog.com/processors/technicalSupport

- E-mail tools questions to dsptools.support@analog.com

- E-mail processor questions to processor.support@analog.com processor.europe@analog.com processor.china@analog.com

- Phone questions to 1-800-ANALOGD

- Contact your Analog Devices, Inc. local sales office or authorized distributor

- Send questions by mail to:

```

Analog Devices, Inc.

One Technology Way

P.O. Box 9106

Norwood, MA 02062-9106

USA

```

# **Supported Processors**

The following is the list of Analog Devices, Inc. processors supported in VisualDSP++<sup>®</sup>.

#### TigerSHARC (ADSP-TSxxx) Processors

The name *TigerSHARC* refers to a family of floating-point and fixed-point [8-bit, 16-bit, and 32-bit] processors. VisualDSP++ currently supports the following TigerSHARC processors:

ADSP-TS101, ADSP-TS201, ADSP-TS202, and ADSP-TS203

#### SHARC® (ADSP-21xxx) Processors

The name *SHARC* refers to a family of high-performance, 32-bit, floating-point processors that can be used in speech, sound, graphics, and imaging applications. VisualDSP++ currently supports the following SHARC processors:

ADSP-21020, ADSP-21060, ADSP-21061, ADSP-21062, ADSP-21065L, ADSP-21160, ADSP-21161, ADSP-21261, ADSP-21262, ADSP-21263, ADSP-21266, ADSP-21267, ADSP-21362, ADSP-21363, ADSP-21364, ADSP-21365, ADSP-21366, ADSP-21367, ADSP-21368, and ADSP-21369

Blackfin® (ADSP-BFxxx) Processors

The name *Blackfin* refers to a family of 16-bit, embedded processors. VisualDSP++ currently supports the following Blackfin processors:

ADSP-BF531, ADSP-BF532, ADSP-BF533, ADSP-BF534, ADSP-BF535, ADSP-BF536, ADSP-BF537, ADSP-BF538, ADSP-BF539, ADSP-BF561, and ADSP-BF566

# **Product Information**

You can obtain product information from the Analog Devices Web site, from the product CD-ROM, or from the printed publications (manuals).

Analog Devices is online at www.analog.com. Our Web site provides information about a broad range of products—analog integrated circuits, amplifiers, converters, and digital signal processors.

### MyAnalog.com

MyAnalog.com is a free feature of the Analog Devices Web site that allows customization of a Web page to display only the latest information on products you are interested in. You can also choose to receive weekly e-mail notifications containing updates to the Web pages that meet your interests. MyAnalog.com provides access to books, application notes, data sheets, code examples, and more.

#### Registration

Visit www.myanalog.com to sign up. Click Register to use MyAnalog.com. Registration takes about five minutes and serves as a means to select the information you want to receive.

If you are already a registered user, just log on. Your user name is your e-mail address.

### **Processor Product Information**

For information on embedded processors and DSPs, visit our Web site at www.analog.com/processors, which provides access to technical publications, data sheets, application notes, product overviews, and product announcements.

Preface

You may also obtain additional information about Analog Devices and its products in any of the following ways.

- E-mail questions or requests for information to processor.support@analog.com processor.europe@analog.com processor.china@analog.com

- Fax questions or requests for information to 1-781-461-3010 (North America) +49-89-76903-157 (Europe)

- Access the FTP Web site at ftp ftp.analog.com (or ftp 137.71.25.69) ftp://ftp.analog.com

### **Related Documents**

The following publications that describe the ADSP-TS201 TigerSHARC processor (and related processors) can be ordered from any Analog Devices sales office:

- ADSP-TS201S TigerSHARC Embedded Processor Data Sheet

- ADSP-TS202S TigerSHARC Embedded Processor Data Sheet

- ADSP-TS203S TigerSHARC Embedded Processor Data Sheet

- ADSP-TS201 TigerSHARC Processor Hardware Reference

- ADSP-TS201 TigerSHARC Processor Programming Reference

For information on product related development software and Analog Devices processors, see these publications:

- VisualDSP++ User's Guide for TigerSHARC Processors

- VisualDSP++ C/C++ Compiler and Library Manual for TigerSHARC Processors

- VisualDSP++ Assembler and Preprocessor Manual for TigerSHARC Processors

- VisualDSP++ Linker and Utilities Manual for TigerSHARC Processors

- VisualDSP++ Kernel (VDK) User's Guide

Visit the Technical Library Web site to access all processor and tools manuals and data sheets:

http://www.analog.com/processors/resources/technicalLibrary

### **Online Technical Documentation**

Online documentation comprises the VisualDSP++ Help system, software tools manuals, hardware tools manuals, processor manuals, the Dinkum Abridged C++ library, and Flexible License Manager (FlexLM) network license manager software documentation. You can easily search across the entire VisualDSP++ documentation set for any topic of interest. For easy printing, supplementary .PDF files of most manuals are also provided.

| File             | Description                                                                                                                                                                                        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .CHM             | Help system files and manuals in Help format                                                                                                                                                       |

| .HTM or<br>.HTML | Dinkum Abridged C++ library and FlexLM network license manager software doc-<br>umentation. Viewing and printing the .HTML files requires a browser, such as<br>Internet Explorer 4.0 (or higher). |

| .PDF             | VisualDSP++ and processor manuals in Portable Documentation Format (PDF).<br>Viewing and printing the .PDF files requires a PDF reader, such as Adobe Acrobat<br>Reader (4.0 or higher).           |

Each documentation file type is described as follows.

If documentation is not installed on your system as part of the software installation, you can add it from the VisualDSP++ CD-ROM at any time by running the Tools installation. Access the online documentation from the VisualDSP++ environment, Windows® Explorer, or the Analog Devices Web site.

#### Accessing Documentation From VisualDSP++

From the VisualDSP++ environment:

- Access VisualDSP++ online Help from the Help menu's Contents, Search, and Index commands.

- Open online Help from context-sensitive user interface items (toolbar buttons, menu commands, and windows).

#### **Accessing Documentation From Windows**

In addition to any shortcuts you may have constructed, there are many ways to open VisualDSP++ online Help or the supplementary documentation from Windows. Help system files (.CHM) are located in the Help folder, and .PDF files are located in the Docs folder of your VisualDSP++ installation CD-ROM. The Docs folder also contains the Dinkum Abridged C++ library and the FlexLM network license manager software documentation.

#### Using Windows Explorer

- Double-click the vdsp-help.chm file, which is the master Help system, to access all the other .CHM files.

- Double-click any file that is part of the VisualDSP++ documentation set.

#### Using the Windows Start Button

- Access VisualDSP++ online Help by clicking the **Start** button and choosing **Programs**, **Analog Devices**, **VisualDSP++**, and **VisualDSP++ Documentation**.

- Access the .PDF files by clicking the Start button and choosing **Programs**, **Analog Devices**, **VisualDSP++**, **Documentation for Printing**, and the name of the book.

### Accessing Documentation From the Web

```

Download manuals at the following Web site:

http://www.analog.com/processors/resources/technicalLibrary/

manuals

```

Select a processor family and book title. Download archive (.ZIP) files, one for each manual. Use any archive management software, such as WinZip, to decompress downloaded files.

# **Printed Manuals**

For general questions regarding literature ordering, call the Literature Center at 1-800-ANALOGD (1-800-262-5643) and follow the prompts.

### VisualDSP++ Documentation Set

To purchase VisualDSP++ manuals, call 1-603-883-2430. The manuals may be purchased only as a kit.

If you do not have an account with Analog Devices, you are referred to Analog Devices distributors. For information on our distributors, log onto http://www.analog.com/salesdir/continent.asp.

### Hardware Tools Manuals

To purchase EZ-KIT Lite® and In-Circuit Emulator (ICE) manuals, call **1-603-883-2430**. The manuals may be ordered by title or by product number located on the back cover of each manual.

### **Processor Manuals**

Hardware reference and instruction set reference manuals may be ordered through the Literature Center at 1-800-ANALOGD (1-800-262-5643), or downloaded from the Analog Devices Web site. Manuals may be ordered by title or by product number located on the back cover of each manual.

### Data Sheets

All data sheets (preliminary and production) may be downloaded from the Analog Devices Web site. Only production (final) data sheets (Rev. 0, A, B, C, and so on) can be obtained from the Literature Center at **1-800-ANALOGD** (**1-800-262-5643**); they also can be downloaded from the Web site.

To have a data sheet faxed to you, call the Analog Devices Faxback System at **1-800-446-6212**. Follow the prompts and a list of data sheet code numbers will be faxed to you. If the data sheet you want is not listed, check for it on the Web site.

# Conventions

Text conventions used in this manual are identified and described as follows.

| Example                      | Description                                                                                                                                                                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Close command<br>(File menu) | Titles in reference sections indicate the location of an item within the VisualDSP++ environment's menu system (for example, the <b>Close</b> command appears on the <b>File</b> menu).                                                                                                                                  |

| {this   that}                | Alternative items in syntax descriptions appear within curly brackets<br>and separated by vertical bars; read the example as this or that. One<br>or the other is required.                                                                                                                                              |

| [this   that]                | Optional items in syntax descriptions appear within brackets and sepa-<br>rated by vertical bars; read the example as an optional this or that.                                                                                                                                                                          |

| [this,]                      | Optional item lists in syntax descriptions appear within brackets delimited by commas and terminated with an ellipse; read the example as an optional comma-separated list of this.                                                                                                                                      |

| .SECTION                     | Commands, directives, keywords, and feature names are in text with letter gothic font.                                                                                                                                                                                                                                   |

| filename                     | Non-keyword placeholders appear in text with italic style format.                                                                                                                                                                                                                                                        |

| í                            | <b>Note:</b> For correct operation,<br>A Note: provides supplementary information on a related topic. In the<br>online version of this book, the word <b>Note</b> appears instead of this<br>symbol.                                                                                                                     |

| ×                            | Caution: Incorrect device operation may result if<br>Caution: Device damage may result if<br>A Caution: identifies conditions or inappropriate usage of the product<br>that could lead to undesirable results or product damage. In the online<br>version of this book, the word Caution appears instead of this symbol. |

| $\bigcirc$                   | <b>Warning:</b> Injury to device users may result if<br>A Warning: identifies conditions or inappropriate usage of the product<br>that could lead to conditions that are potentially hazardous for devices<br>users. In the online version of this book, the word <b>Warning</b> appears<br>instead of this symbol.      |

xxxiii

Additional conventions, which apply only to specific chapters, may appear throughout this document.

### Conventions

# **1 INTRODUCTION**

The ADSP-TS201 TigerSHARC Processor Programming Reference describes the ADSP-TS201 TigerSHARC processor architecture and instruction set. These descriptions provide the information required for programming TigerSHARC processor systems. This chapter introduces programming concepts for the processor with the following information:

- "Processor Architecture" on page 1-7

- "Instruction Line Syntax and Structure" on page 1-23

- "Instruction Parallelism Rules" on page 1-27

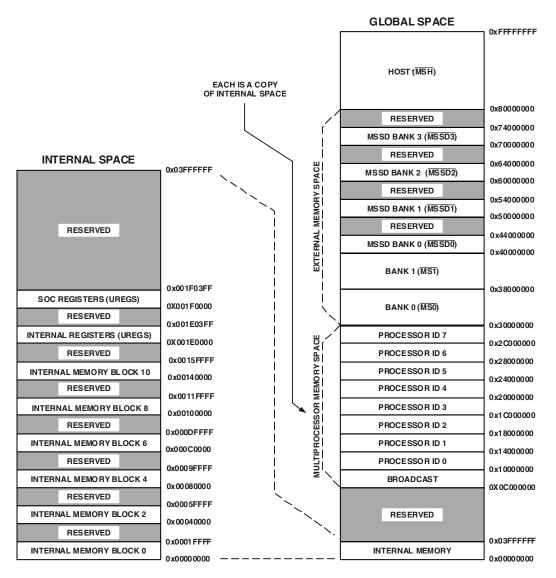

The ADSP-TS201 processor is a 128-bit, high performance TigerSHARC processor. The ADSP-TS201 processor sets a new standard of performance for digital signal processors, combining multiple computation units for floating-point and fixed-point processing as well as very wide word widths. The ADSP-TS201 processor maintains a 'system-on-chip' scalable computing design philosophy, including 24M bit of on-chip DRAM, six 4K word caches (one per memory block), integrated I/O peripherals, a host processor interface, DMA controllers, LVDS link ports, and shared bus connectivity for glueless multiprocessing.

In addition to providing unprecedented performance in DSP applications in raw MFLOPS and MIPS, the ADSP-TS201 processor boosts performance measures such as MFLOPS/Watt and MFLOPS/square inch in multiprocessing applications.

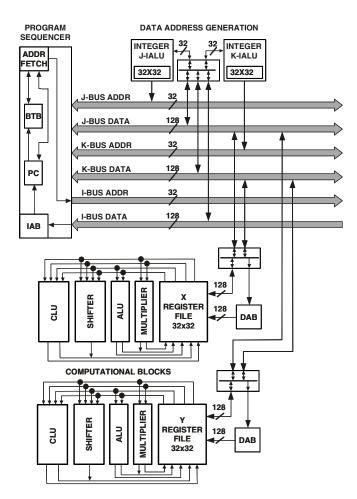

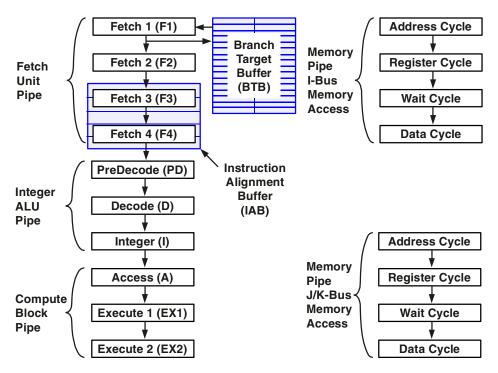

Figure 1-1. ADSP-TS201 TigerSHARC Processor Core Diagram

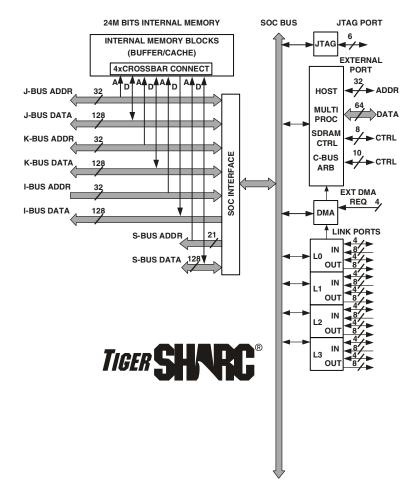

Figure 1-2. ADSP-TS201 TigerSHARC Processor Peripherals Diagram

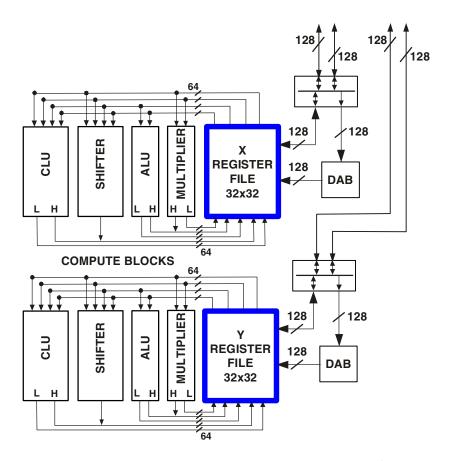

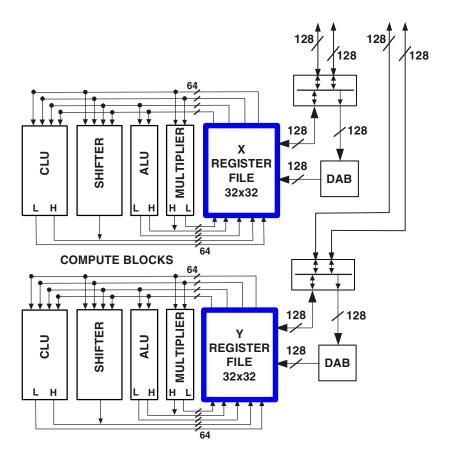

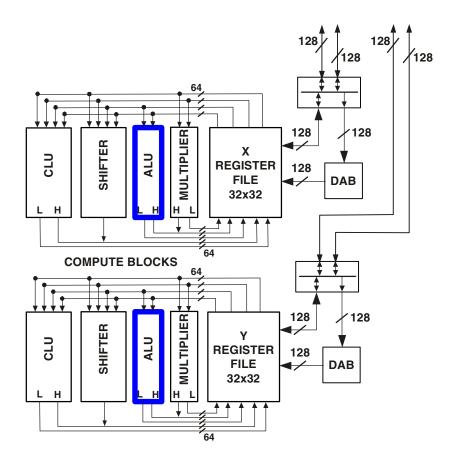

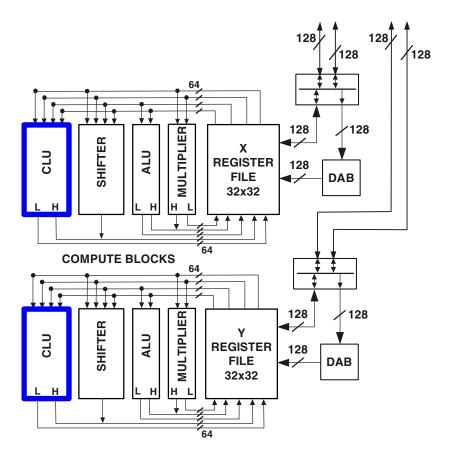

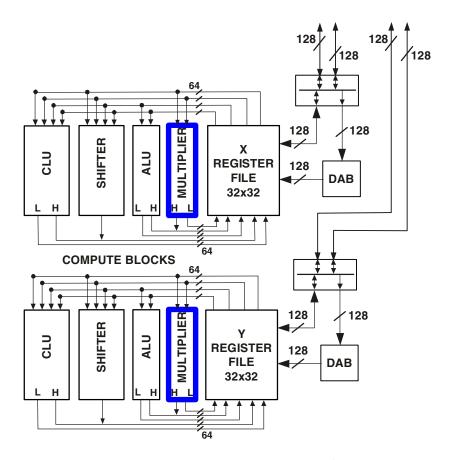

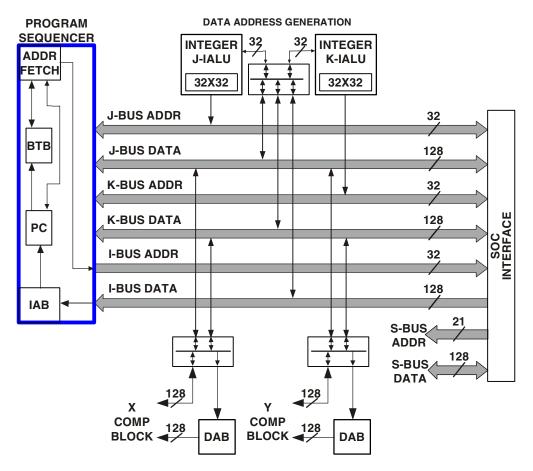

As shown in Figure 1-1 and Figure 1-2, the processor has the following architectural features:

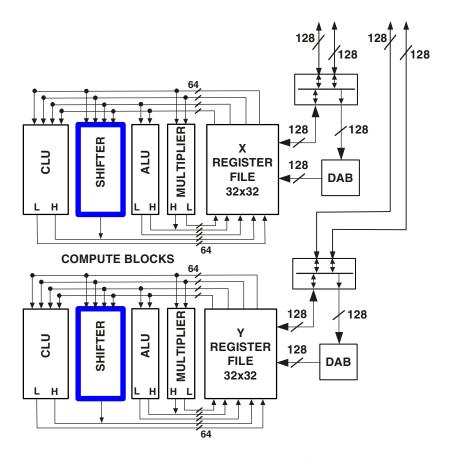

- Dual computation blocks: X and Y each consisting of a multiplier, ALU, CLU, shifter, and a 32-word register file

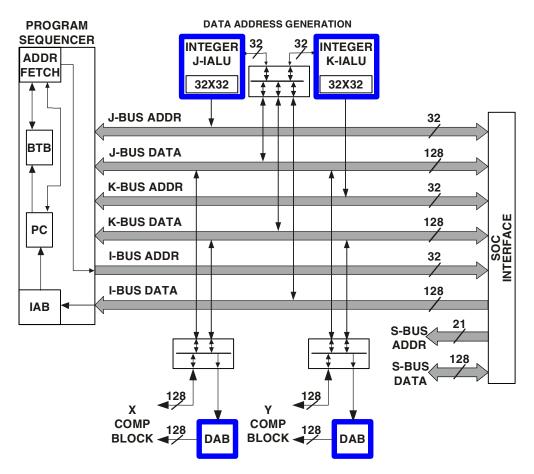

- Dual integer ALUs: J and K each containing a 32-bit IALU and 32-word register file

- Program sequencer Controls the program flow and contains an instruction alignment buffer (IAB) and a branch target buffer (BTB)

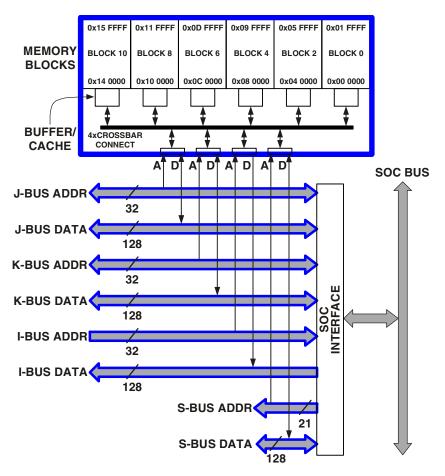

- Three 128-bit buses providing high bandwidth connectivity between internal memory and the rest of the processor core (compute blocks, IALUs, program sequencer, and SOC interface)

- A 128-bit bus providing high bandwidth connectivity between internal memory and external I/O peripherals (DMA, external port, and link ports)

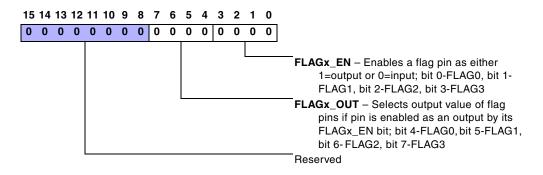

- External port interface including the host interface, SDRAM controller, static pipelined interface, four DMA channels, four LVDS link ports (each with two DMA channels), and multiprocessing support

- 24M bits of internal memory organized as six 4M bit blocks—each block containing 128K words x 32 bits; each block connects to the crossbar through its own buffers and a 128K bit, 4-way set associative cache

- Debug features

- JTAG Test Access Port

The TigerSHARC processor external port provides an interface to external memory, to memory-mapped I/O, to host processor, and to additional TigerSHARC processors. The external port performs external bus arbitration and supplies control signals to shared, global memory, SDRAM, and I/O devices.

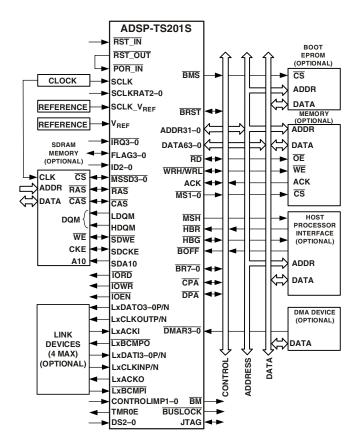

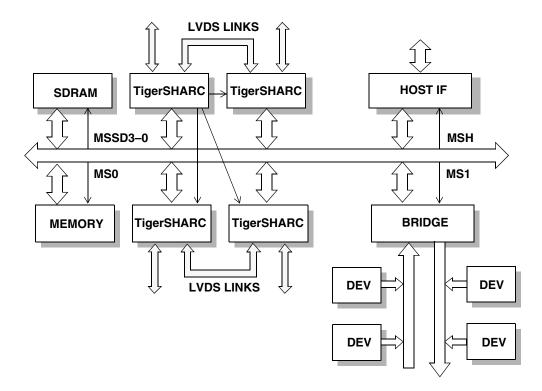

Figure 1-3 illustrates a typical single processor system. A multiprocessor system is illustrated in Figure 1-4 and is discussed later in "Scalability and Multiprocessing" on page 1-22.

Figure 1-3. Single Processor Configuration

Figure 1-4. Multiprocessing Cluster Configuration

The TigerSHARC processor includes several features that simplify system development. The features lie in three key areas:

- Support of IEEE floating-point formats

- IEEE Standard 1149.1 Joint Test Action Group (JTAG) serial scan path and on-chip emulation features

- Architectural features supporting high level languages and operating systems

The features of the TigerSHARC processor architecture that directly support high level language compilers and operating systems include:

- Simple, orthogonal instruction allowing the compiler to efficiently use the multi-instruction slots

- General-purpose data and IALU register files

- 32-bit (IEEE Standard 754/854) and 40-bit floating-point and 8-, 16-, 32-, and 64-bit fixed-point native data types

- Large address space

- Immediate address modify fields

- Easily supported relocatable code and data

- Fast save and restore of processor registers onto internal memory stacks

# **Processor Architecture**

As shown in Figure 1-1 on page 1-2 and Figure 1-2 on page 1-3, the processor architecture consists of two divisions: the processor core (where instructions execute) and the I/O peripherals (where data is stored and off-chip I/O is processed). The following discussion provides a high level description of the processor core and peripherals architecture. More detail on the core appears in other sections of this reference. For more information on I/O peripherals, see the *ADSP-TS201 TigerSHARC Processor Hardware Reference*.

This section describes:

- "Compute Blocks" on page 1-10

- "Integer Arithmetic Logic Unit (IALU)" on page 1-13

- "Program Sequencer" on page 1-15

- "Internal Memory and Buses" on page 1-19

- "Booting" on page 1-21

- "Scalability and Multiprocessing" on page 1-22g

- "Emulation and Test Support" on page 1-22

High performance is facilitated by the ability to execute up to four 32-bit wide instructions per cycle. The TigerSHARC processor uses a variation of a *Static Superscalar*<sup>TM</sup> architecture to allow the programmer to specify which instructions are executed in parallel in each cycle. The instructions do not have to be aligned in memory so that program memory is not wasted.

The 24M bit internal memory is divided into six 128K word memory blocks. Each of the four internal address/data bus pairs connect to all of the six memory blocks via a crossbar interface. The six memory blocks support up to four accesses every cycle where each memory block can perform a 128-bit access in a cycle. Each block's cache and prefetch mechanism improve access performance of internal memory (embedded DRAM).

The external port cluster bus is 64 bits wide. The high I/O bandwidth complements the high processing speeds of the core. To facilitate the high clock rate, the ADSP-TS201 processor uses a pipelined external bus with programmable pipeline depth for interprocessor communications and for Synchronous Flow-through SRAM (SSRAM) and SDRAM.

The four LVDS link ports support point-to-point high bandwidth data transfers. Each link port supports full-duplex communication.

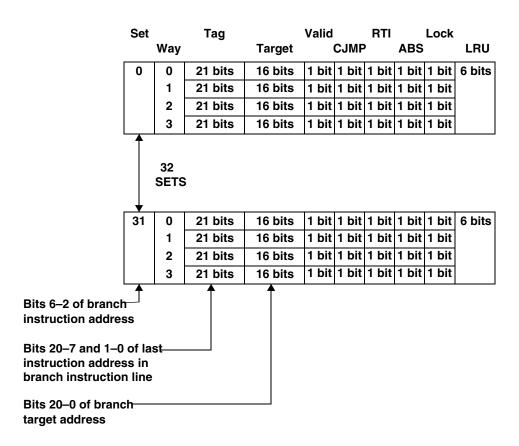

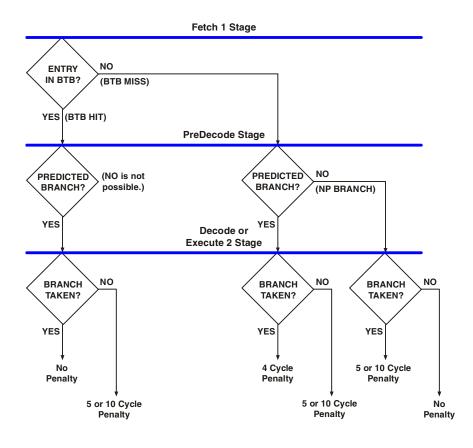

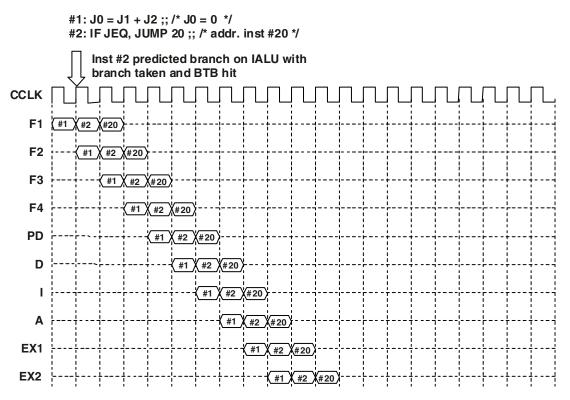

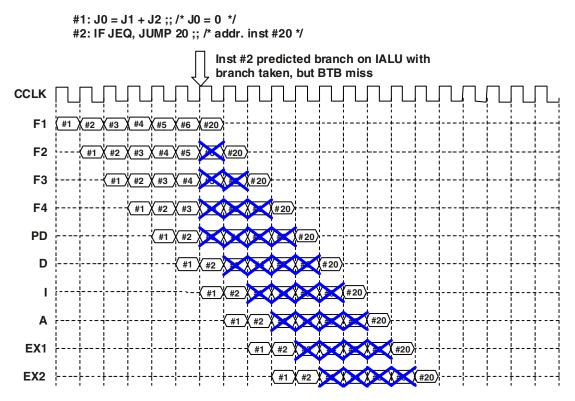

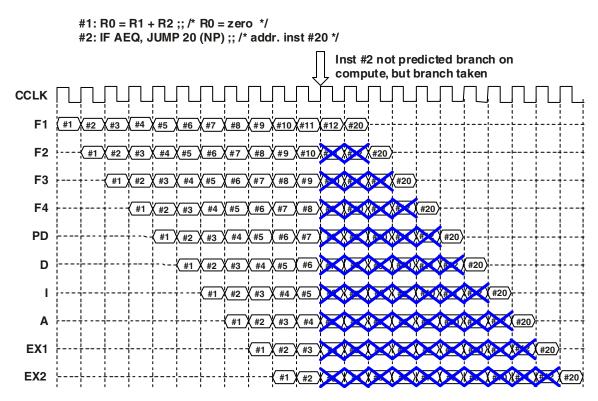

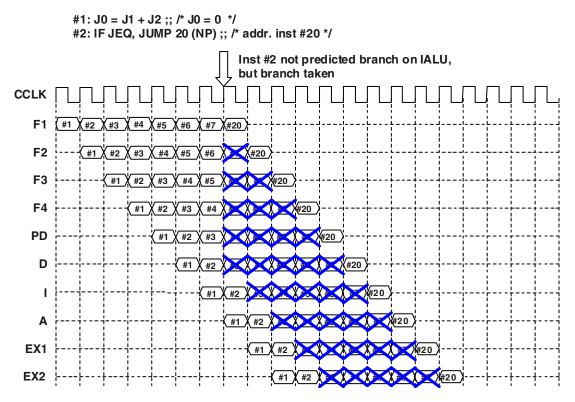

The processor operates with a two cycle arithmetic pipeline. The branch pipeline is four to ten cycles. A branch target buffer (BTB) is implemented to reduce branch delay.

During compute intensive operations, one or both integer ALUs compute or generate addresses for fetching up to two quad operands from two memory blocks, while the program sequencer simultaneously fetches the next quad instruction from a third memory block. In parallel, the computation units can operate on previously fetched operands while the sequencer prepares for a branch.

While the core processor is doing the above, the DMA channels can be replenishing the internal memories in the background with quad data from either the external port or the link ports.

The processing core of the ADSP-TS201 processor reaches exceptionally high DSP performance through using these features:

- Computation pipeline

- Dual computation units

- Execution of up to four instructions per cycle

- Access of up to eight words per cycle from memory

The two identical computation units support floating-point as well as fixed-point arithmetic. These units (compute blocks) perform up to 6 floating-point or 24 fixed-point operations per cycle.

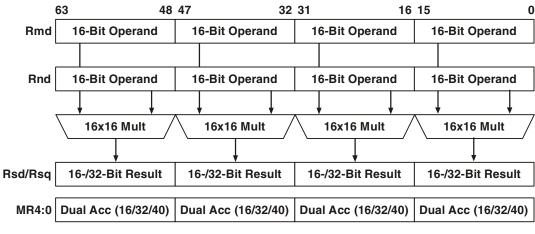

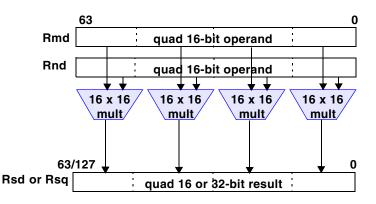

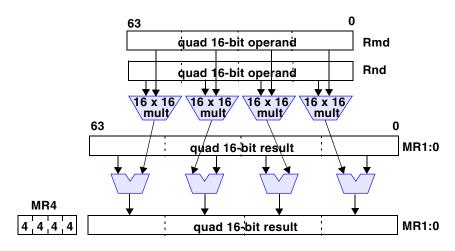

Each multiplier and ALU unit can execute four 16-bit fixed-point operations per cycle, using Single-Instruction, Multiple-Data (SIMD) operation. This operation boosts performance of critical imaging and signal processing applications that use fixed-point data.

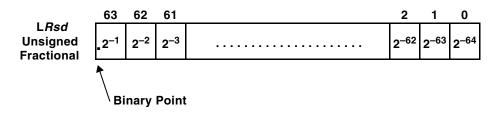

## **Compute Blocks**

The TigerSHARC processor core contains two computation units called *compute blocks*. Each compute block contains a register file and four independent computation units—an ALU, a CLU, a multiplier, and a shifter. For meeting a wide variety of processing needs, the computation units process data in several fixed- and floating-point formats.

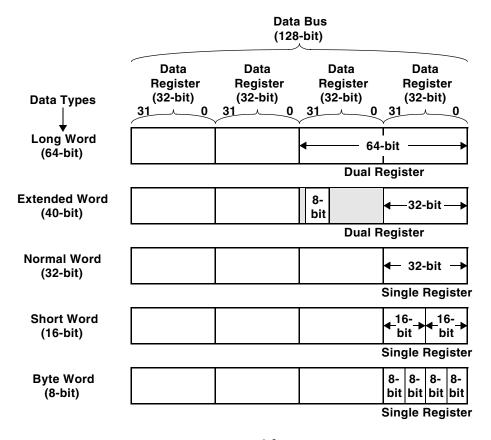

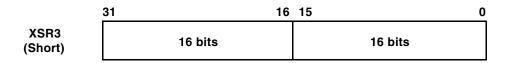

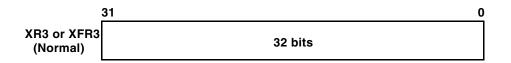

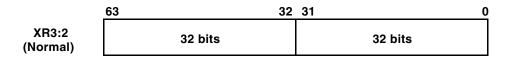

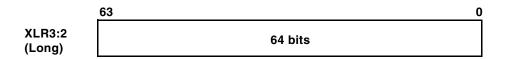

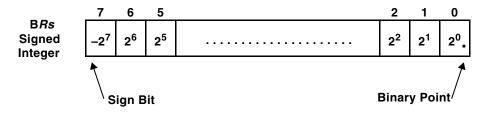

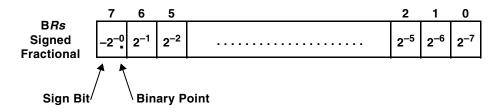

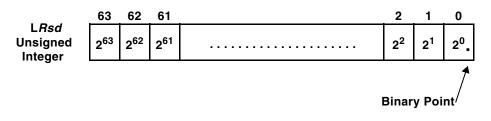

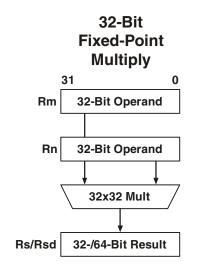

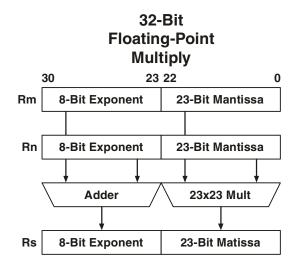

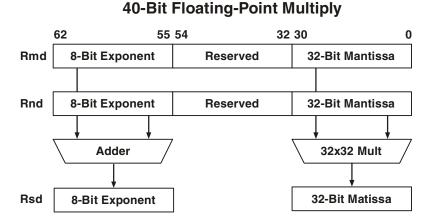

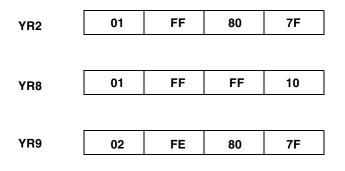

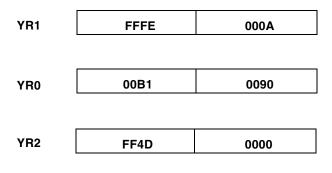

These formats are listed here and shown in Figure 1-5:

#### • Fixed-point format

These include 64-bit long word, 32-bit normal word, 32-bit complex (16-bit real and 16-bit imaginary), 16-bit short word, and 8-bit byte word. For short word fixed-point arithmetic, quad parallel operations on quad-aligned data allow fast processing of array data. Byte operations are also supported for octal-aligned data.

#### • Floating-point format

These include 32-bit normal word and 40-bit extended word. Floating-point operations are single or extended precision. The normal word floating-point format is the standard IEEE format, and the 40-bit extended-precision format occupies a double word (64 bits) with eight additional least significant bits (LSBs) of mantissa for greater accuracy.

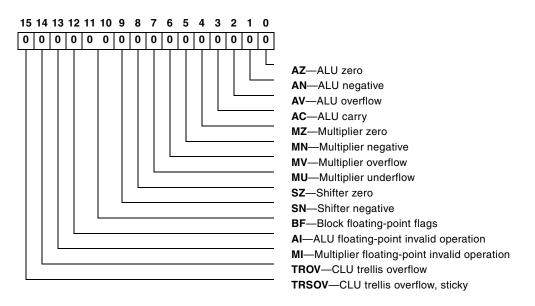

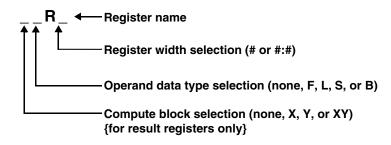

Each compute block has a general-purpose, multiport, 32-word data register file for transferring data between the computation units and the data buses and storing intermediate results. All of these registers can be accessed as single-, double-, or quad-aligned registers. For more information on the register file, see "Compute Block Registers" on page 2-1.

### Arithmetic Logic Unit (ALU)

The ALU performs arithmetic operations on fixed-point and floatingpoint data and logical operations on fixed-point data. The source and destination of most ALU operations is the compute block register file.

Figure 1-5. Word Format Definitions<sup>1,2</sup>

- 1 The TigerSHARC processor internal data buses are 128 bits (one quad word) wide. In a quad word, the processor can move 16 byte words, 8 short words, 4 normal words, or 2 long words over the bus at the same time.

- 2 For details on the numeric formats (fixed- and floating-point data formats) that can be used with each of the data types in Figure 1-5, see "Numeric Formats" on page 2-16.

## Communications Logic Unit (CLU)

On the ADSP-TS201 processor, there is a special purpose compute unit called the *communications logic unit (CLU)*. The CLU instructions are designed to support different algorithms used for communications applications. The algorithms that are supported by the CLU instructions are:

- Viterbi Decoding

- Turbo code Decoding

- Despreading for code division multiple access (CDMA) systems

- Cross correlations used for path search

For more information on the CLU features, see "CLU" on page 4-1.

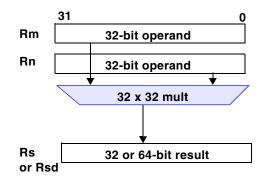

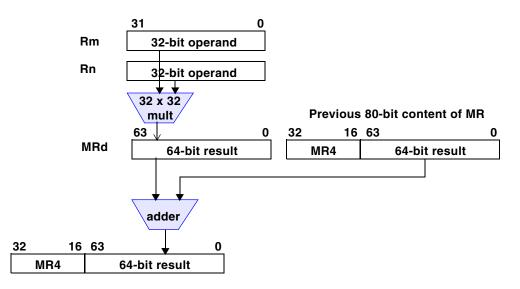

## Multiply Accumulator (Multiplier)

The multiplier performs fixed-point or floating-point multiplication and fixed-point multiply/accumulate operations. The multiplier supports several data types in fixed- and floating-point formats. The floating-point formats are float and float-extended, as in the ALU. The source and destination of most operations is the compute block register file.

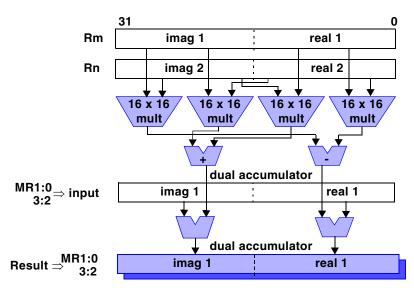

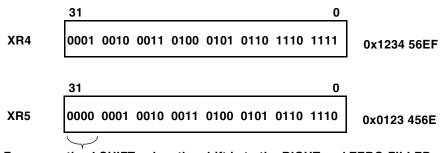

The ADSP-TS201 processor's multiplier supports complex multiply-accumulate operations. Complex numbers are represented by a pair of 16-bit short words within a 32-bit word. The LSBs of the input operand represent the real part, and the most significant bits (MSBs) of the input operand represent the imaginary part. For more information on the multiplier, see "Multiplier" on page 5-1.

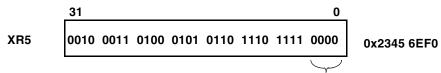

### Bit Wise Barrel Shifter (Shifter)

The shifter performs logical and arithmetic shifts, bit manipulation, field deposit, and field extraction. The shifter operates on one 64-bit, one or two 32-bit, two or four 16-bit, and four or eight 8-bit fixed-point operands. Shifter operations include:

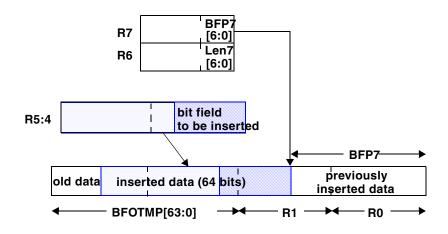

- Shifts and rotates from off-scale left to off-scale right

- Bit manipulation operations, including bit set, clear, toggle and test

- Bit field manipulation operations, including field extract and deposit, using register BFOTMP (which is internal to the shifter)

- Bit FIFO operations to support bit streams with fields of varying length

- Support for ADSP-21000 DSP family compatible fixedpoint/floating-point conversion operations (such as exponent extract, number of leading ones or zeros)

For more information on the shifter, see "Shifter" on page 6-1.

# Integer Arithmetic Logic Unit (IALU)

The IALUs can execute standard standalone ALU operations on IALU register files. The IALUs also execute register load, store, and transfer operations, providing memory addresses when data is transferred between memory and registers. The processor has dual IALUs (the J-IALU and the K-IALU) that enable simultaneous addresses for two transactions of up to 128 bits in parallel. The IALUs allow compute operations to execute with maximum efficiency because the computation units can be devoted exclusively to processing data.

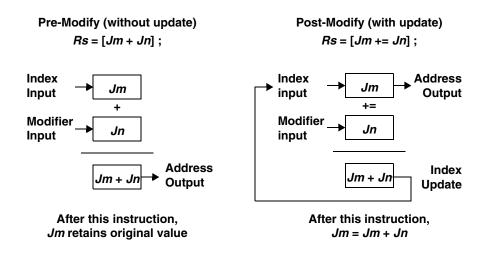

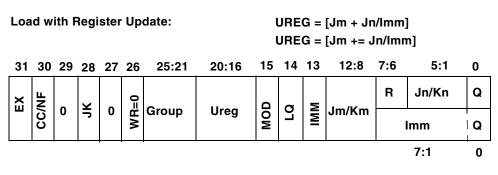

Each IALU has a multiport, 32-word register file. All IALU calculations are executed in a single cycle. The IALUs support pre-modify with no update and post-modify with update address generation. Circular data buffers are implemented in hardware. The IALUs support the following types of instructions:

- Regular IALU instructions

- Move Data instructions

- Load Data instructions

- Load/Store instructions with register update

- Load/Store instructions with immediate update

For indirect addressing (instructions with update), one of the registers in the register file can be modified by another register in the file or by an immediate 8- or 32-bit value, either before (pre-modify) or after (postmodify) the access. For circular buffer addressing, a length value can be associated with the first four registers to perform automatic modulo addressing for circular data buffers; the circular buffers can be located at arbitrary boundaries in memory. Circular buffers allow efficient implementation of delay lines and other data structures, which are commonly used in digital filters and Fourier transformations. The ADSP-TS201 processor circular buffers automatically handle address pointer wraparounds, reducing overhead and simplifying implementation.

The IALUs also support bit reverse addressing, which is useful for the FFT algorithm. Bit reverse addressing is implemented using a reverse carry addition that is similar to regular additions, but the carry is taken from the upper bits and is driven into lower bits.

The IALU provides flexibility in moving data as single, dual, or quad words. Every instruction can execute with a throughput of one per cycle. IALU instructions execute with a single cycle of latency. Normally, there are no dependency delays between IALU instructions, but if there are, four cycles of latency can occur.

For more information on the IALUs, see "IALU" on page 7-1.

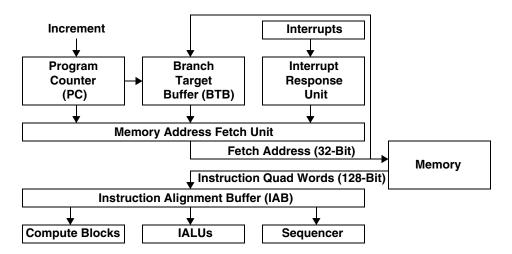

## **Program Sequencer**

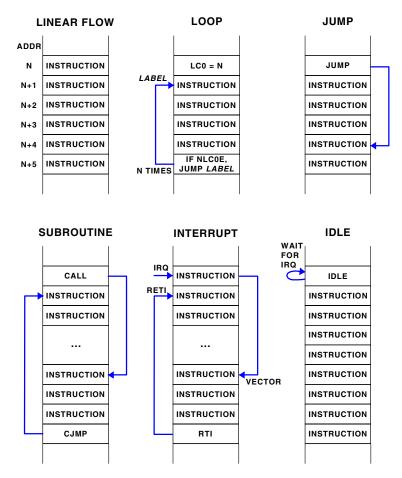

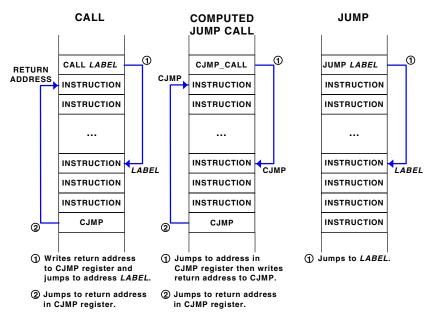

The program sequencer supplies instruction addresses to memory and, together with the IALUs, allows compute operations to execute with maximum efficiency. The sequencer supports efficient branching using the branch target buffer (BTB), which reduces branch delays for conditional and unconditional instructions. The two responsibilities of the sequencer are to decode fetched instructions—separating the instruction slots of the instruction line and sending each instruction to its execution unit (compute blocks, IALUs, or sequencer)—and to control the program flow. The sequencer's control flow instructions divide into two types:

- *Control flow instructions*. These instructions are used to direct program execution by means of jumps and to execute individual instructions conditionally.

- *Immediate extension instructions*. These instructions are used to extend the numeric fields used in immediate operands for the sequencer and the IALU.

Control flow instructions divide into two types:

- Direct jumps and calls based on an immediate address operand specified in the instruction encoding. For example, 'if <cond> jump 100;' always jumps to address 100, if the <cond> evaluates as true.

- Indirect jumps based on an address supplied by a register. The instructions used for specifying conditional execution of a line are a subcategory of indirect jumps. For example, 'if <cond> cjmp;' is a jump to the address pointed to by the CJMP register.

The control flow instruction must use the first instruction slot in the instruction line.

Immediate extensions are associated with IALU or sequencer (control flow) instructions. These instructions are not specified by the programmer, but are implied by the size of the immediate data used in the instructions. The programmer must place the instruction that requires an immediate extension in the first instruction slot and leave an empty instruction slot in the line (use only three slots), so the assembler can place the immediate extension in the second instruction slot of the instruction line.

Note that only one immediate extension may be in a single instruction line.

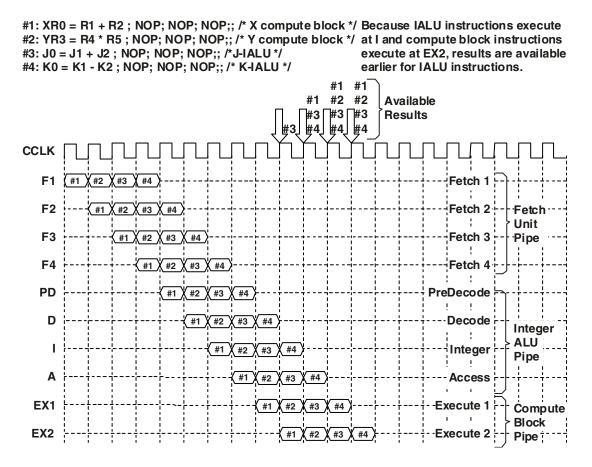

The ADSP-TS201 processor achieves its fast execution rate by means of a ten-cycle pipeline.

Two stages of the sequencer's pipeline actually execute in the computation units. The computation units perform single cycle operations with a twocycle computation pipeline, meaning that results are available for use two cycles after the operation is begun. Hardware causes a stall if a result is not available in a given cycle (register dependency check). Up to two computation instructions per compute block can be issued in each cycle, instructing the ALU, multiplier, or shifter to perform independent, simultaneous operations.

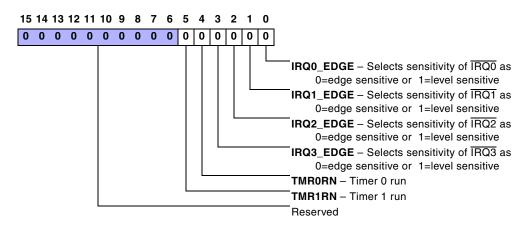

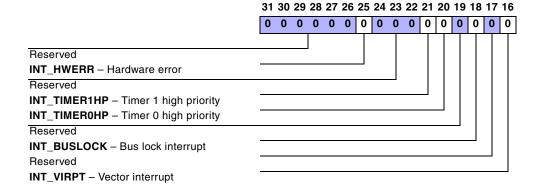

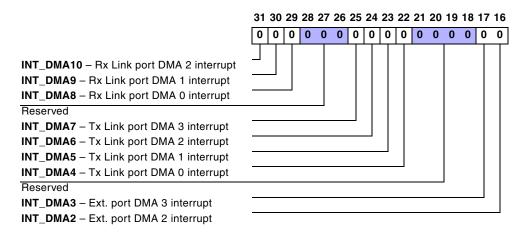

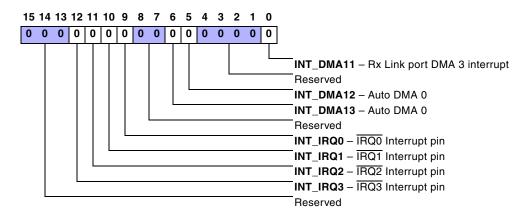

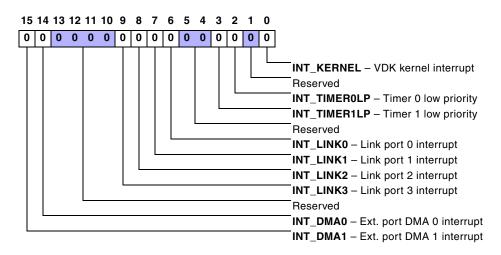

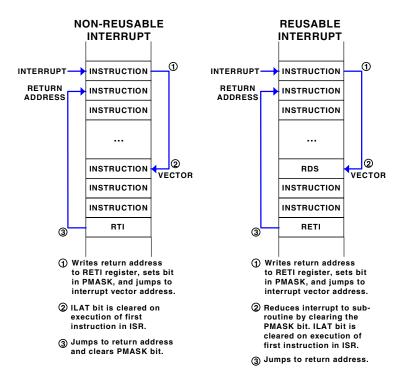

The ADSP-TS201 processor has four general-purpose external interrupts, TR03-0. The processor also has internally generated interrupts for the two timers, DMA channels, link ports, arithmetic exceptions, multiprocessor vector interrupts, and user-defined software interrupts. Interrupts can be nested through instruction commands. Interrupts have a short latency and do not abort currently executing instructions. Interrupts vector directly to a user-supplied address in the interrupt table register file, removing the overhead of a second branch.

The branch penalty in a deeply pipelined processor, such as the ADSP-TS201 processor, can be compensated for by using a branch target buffer (BTB) and branch prediction. The branch target address is stored in the BTB. When the address of a jump instruction, which is predicted by the user to be taken in most cases, is recognized (the tag address), the corresponding jump address is read from the BTB and is used as the jump address on the next cycle. Thus, the latency of a jump is reduced from five to nine wasted cycles to zero wasted cycles. If this address is not stored in the BTB, the instruction must be fetched from memory.

Other instructions also use the BTB to speed up these types of branches. These instructions are interrupt return, call return, and computed jump instructions.

For more information on the sequencer, BTB, and immediate extensions, see "Program Sequencer" on page 8-1.

### **Quad Instruction Execution**

The ADSP-TS201 processor can execute up to four instructions per cycle from a single memory block, due to the 128-bit wide access per cycle. The ability to execute several instructions in a single cycle derives from a static superscalar architectural concept. This is not strictly a superscalar architecture because the instructions executed in each cycle are specified in the instruction by the programmer or by the compiler, and not by the chip hardware. There is also no instruction reordering. Register dependencies are, however, examined by the hardware and stalls are generated where appropriate. Code is fully compacted in memory and there are no alignment restrictions for instruction lines.

#### **Relative Addresses for Relocation**

Most instructions in the ADSP-TS201 processor support PC relative branches to allow code to be relocated easily. Also, most data references are *register relative*, which means they allow programs to access data blocks relative to a base register.

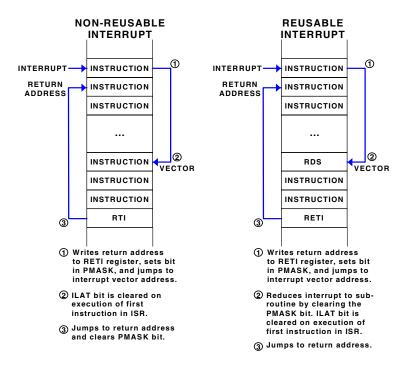

#### Nested Call and Interrupt

Nested call and interrupt return addresses (along with other registers as needed) are saved by specific instructions onto the on-chip memory stack, allowing more generality when used with high level languages. Non-nested calls and interrupts do not need to save the return address in internal memory, making these more efficient for short, non-nested routines.

### **Context Switching**

The ADSP-TS201 processor provides the ability to save and restore up to eight registers per cycle onto a stack in two internal memory blocks when using load/store instructions. This fast save/restore capability permits efficient interrupts and fast context switching. It also allows the ADSP-TS201 processor to dispense with on-chip PC stack or alternate registers for register files or status registers.

## **Internal Memory and Buses**

The on-chip memory consists of six blocks of 4M bits each. Each block is 128K words, thus providing high bandwidth sufficient to support both computation units, the instruction stream and external I/O, even in very intensive operations. The ADSP-TS201 processor provides access to program, two data operands, and a system access (over the SOC bus) to different memory blocks without memory or bus constraints. The memory blocks can store instructions and data interchangeably.

Each memory block is organized as 128K words of 32 bits each. The accesses are pipelined to meet one clock cycle access time needed by the core, DMA, or by the external bus. Each access can be up to four words. The six memory blocks are a resource that must be shared between the compute blocks, the IALUs, the sequencer, the external port, and the link ports. In general, if during a particular cycle more than one unit in the processor attempts to access the same memory, one of the competing units is granted access, while the other is held off for further arbitration until the following cycle—see "Bus Arbitration Protocol" in the *ADSP-TS201 TigerSHARC Processor Hardware Reference*. This type of conflict only has a small impact on performance due to the very high bandwidth afforded by the internal buses.

An important benefit of large on-chip memory is that by managing the movement of data on and off chip with DMA, a system designer can realize high levels of determinism in execution time. Predictable and deterministic execution time is a central requirement in the DSP and realtime systems.

### Internal Buses

The processor core has three buses (I-bus, J-bus, and K-bus), each connected to all of the internal memory blocks via a crossbar interface. These buses are 128 bits wide to allow up to four instructions, or four aligned data words, to be transferred in each cycle on each bus. On-chip system elements use these SOC bus and S-bus to access memory. Only one access to each memory block is allowed in each cycle, so if the application accesses a different memory segment for each purpose (instruction fetch, load/store J-IALU and K-IALU instructions and external accesses), all transactions can be executed with no stalls.

A separate system on chip (SOC) bus connects the external interfaces (external port, DMA, link ports, JTAG port, and others) to the memory system via the SOC interface and S-bus. This bus has a 128-bit wide data bus and a 32-bit wide address bus. It works at half the processor core clock rate. All data transferred between internal memory or core, and external port (cluster bus, link port, and others) passes through this bus.

Most registers of the ADSP-TS201 processor are classified as universal registers (*Ureg*). Instructions are provided for transferring data between any two *Ureg* registers, between a *Ureg* and memory, or for the immediate load of a *Ureg*. This includes control registers and status registers, as well as the data registers in the register files. These transfers occur with the same timing as internal memory load/store. All registers can be accessed by register-move instructions or by external master access (another ADSP-TS201 on the same cluster bus or host), but only the core registers can be accessed by load/store instructions or load-immediate instructions.

### Internal Transfer

Most registers of the ADSP-TS201 processor are classified as universal registers (*Ureg*). Instructions are provided for transferring data between any two *Ureg* registers, between a *Ureg* and memory, or for the immediate load of a *Ureg*. This includes control registers and status registers, as well as the data registers in the register files. These transfers occur with the same timing as internal memory load/store.

### Data Accesses

Each move instruction specifies the number of words accessed from each memory block. Two memory blocks can be accessed on each cycle because of the two IALUs. For a discussion of data and register widths and the syntax that specifies these accesses, see "Register File Registers" on page 2-6.

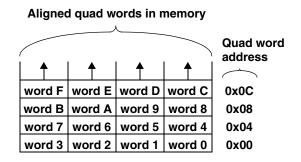

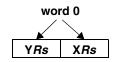

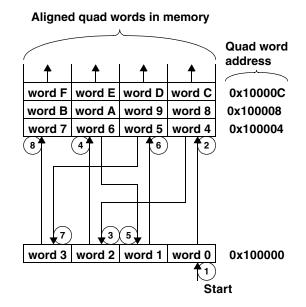

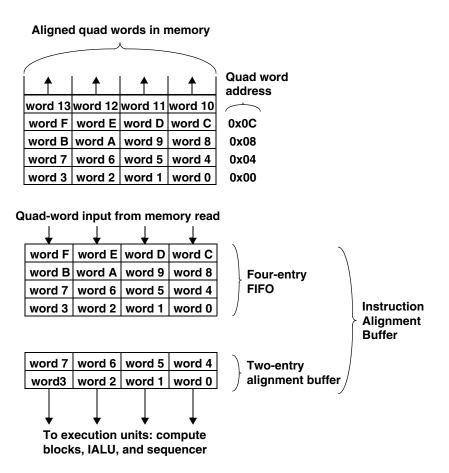

## Quad Data Access

Instructions specify whether one, two, or four words are to be loaded or stored. Quad words<sup>1</sup> can be aligned on a quad word boundary and long words aligned on a long word boundary. This, however, is not necessary when loading data to computation units because a data alignment buffer (DAB) automatically aligns quad words that are not aligned in memory.

Up to four data words from each memory block can be supplied to each computation unit, meaning that new data is not required on every cycle. This data throughput leaves alternate cycles for I/O to the memories. Using data access this way is beneficial in applications with high I/O requirements because it allows the I/O to occur without degrading core processor performance.

# Booting

The internal memory of the ADSP-TS201 processor can be loaded from an 8-bit EPROM using a boot mechanism at system powerup. The processor can also be booted using an external master or through one of the link ports. Selection of the boot source is controlled by external pins. For information on booting the processor, see the *ADSP-TS201 TigerSHARC Processor Hardware Reference* or the processor data sheet.

<sup>&</sup>lt;sup>1</sup> A memory quad word is comprised of four 32-bit words or 128 bits of data.

# **Scalability and Multiprocessing**

The ADSP-TS201 processor, like the ADSP-TS101 processor, is designed for multiprocessing applications. The primary multiprocessing architecture supported is a cluster of up to eight TigerSHARC processors that share a common bus, a global memory, and an interface to either a host processor or to other clusters. In large multiprocessing systems, this cluster can be considered an element and connected in configurations such as torroid, mesh, tree, crossbar, or others. The user can provide a personal interconnect method or use the on-chip communication ports.

The ADSP-TS201 processor includes the following multiprocessing capabilities:

- On-chip bus arbitration for glueless multiprocessing

- Globally accessible internal memory and registers

- Semaphore support

- Powerful, in-circuit multiprocessing emulation

# **Emulation and Test Support**

The ADSP-TS201 processor supports the IEEE Standard P1149.1 Joint Test Action Group (JTAG) port for system test. This standard defines a method for serially scanning the I/O status of each component in a system. The JTAG serial port is also used by the TigerSHARC processor EZ-ICE® to gain access to the processor's on-chip emulation features.

# Instruction Line Syntax and Structure

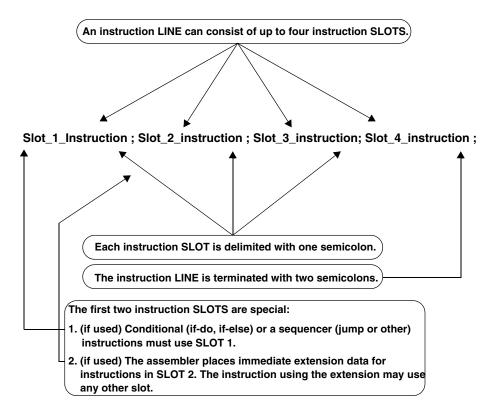

The TigerSHARC processor is a static superscalar DSP-type processor that executes from one to four 32-bit *instruction slots* in an *instruction line*. With few exceptions, instructions execute with a throughput of one instruction line (four instruction slots) per processor core clock (CCLK) cycle

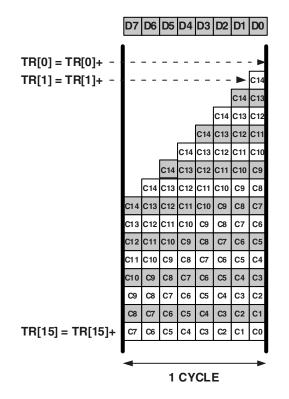

Figure 1-6 shows the instruction slot and line structure.

Figure 1-6. Instruction Line and Slot Structure

There are some important things to note about the instruction slot and instruction line structure and how this structure relates to instruction execution.

- Each instruction line consists of up to four 32-bit instruction slots.

- Instruction slots are delimited with one semicolon ";".

- Instruction lines are terminated with two semicolons ";;".

- Four instructions on an instruction line can be executed in parallel.

- Instructions that use 32-bit data (for example, 32-bit direct addresses or 32-bit immediate data) require two instruction slots to execute; one slot for the instruction and one slot for the immediate extensions.

- Program sequencer and immediate extension instructions require specific instruction slots. The immediate extension slot is assigned by the assembler; an immediate extension is not an instruction written specifically by the programmer.

An instruction is a 32-bit word that activates one or more of the Tiger-SHARC processor's execution units to carry out an operation. *The processor executes or stalls the instructions in the same instruction line together.* Although the processor fetches quad words from memory, instruction lines do not have to be aligned to quad word boundaries. Regardless of size (one to four instructions), instruction lines follow one after the other in memory with a new instruction line beginning one word from where the previous instruction line ended. The end of an instruction line is identified by the MSB in the instruction word.

# Instruction Notation Conventions

The TigerSHARC processor assembly language is based on an algebraic syntax for ease of coding and readability. The syntax for TigerSHARC processor instructions selects the *operation* that the processor executes and

### Introduction

the *option* in which the processor executes the operation. Operations include computations, data movements, and program flow controls. Options include Single-Instruction, Single-Data (SISD) versus Single-Instruction, Multiple-Data (SIMD) selection, data format selection, word size selection, enabling saturation, and enabling truncation. All controls on instruction execution are included in the processor's instruction syntax—there are no mode bits to set in control registers for this processor.

This book presents instructions in summary format. This format shows all the selectable items and optional items available for an instruction. The conventions for these are: