# **User's Manual**

# EB-V850ES/HG2-EE

**Demonstration Kit for the H\_Line Family**

- The information in this document is current as of date of its publication. The information is subject to change without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without prior

written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that

may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other

intellectual property rights of third parties by or arising from the use of NEC Electronics products listed

in this document or any other liability arising from the use of such NEC Electronics products. No

license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual

property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC Electronics no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics

products, customers agree and acknowledge that the possibility of defects thereof cannot be

eliminated entirely. To minimize risks of damage to property or injury (including death) to persons

arising from defects in NEC Electronics products, customers must incorporate sufficient safety

measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

The "Specific" quality grade applies only to NEC Electronics products developed based on a customerdesignated "quality assurance program" for a specific application. The recommended applications of NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

"Standard": Computers, office equipment, communications equipment, test and measurement

equipment, audio and visual equipment, home electronic appliances, machine tools,

personal electronic equipment and industrial robots.

"Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-

disaster systems, anti-crime systems, safety equipment and medical equipment (not

specifically designed for life support).

"Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems,

life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact NEC Electronics sales representative in advance to determine NEC Electronics's willingness to support a given application.

Notes: 1." NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

2. " NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.10

## **CAUTION**

This is a Test- and Measurement equipment with possibility to be significantly altered by user through hardware enhancements/modifications and/or test or application software. Thus, with respect to Council Directive 89/336/EEC (Directive on compliance with the EMC protection requirements), this equipment has no autonomous function. Consequently this equipment is not marked by the CE-symbol.

EEDT-ST-0005-10

Redemption of Waste Electrical and Electronic Equipment (WEEE) in accordance with legal regulations applicable in the European Union only: This equipment (including all accessories) is not intended for household use. After use the equipment cannot be disposed of as household waste. NEC Electronics (Europe) GmbH offers to take back the equipment. All you need to do is register at www.eu.necel.com/weee.

# **Revision History**

| Date       | Revision | Chapter | Description   |

|------------|----------|---------|---------------|

| 16-11-2005 | V1.00    |         | First release |

|            |          |         |               |

|            |          |         |               |

|            |          |         |               |

# **Table of Contents**

| 1.           | Introduction                                | 10 |

|--------------|---------------------------------------------|----|

| 1.1          | Main features of EB-V850ES/HG2-EE           | 10 |

| 1.2          |                                             |    |

| 1.3          |                                             |    |

| 1.4          |                                             |    |

| 2.           | EB-V850ES/HG2-EE system configuration       | 12 |

| 2.1          |                                             |    |

| 2.2          | ·                                           |    |

| 2.3          | Power supply via USB interface              | 12 |

| 3.           | EB-V850ES/HG2-EE board components           | 13 |

| 3.1          | User button SW1                             | 14 |

| 3.2          |                                             |    |

| 3.3          |                                             |    |

| 3.3.         |                                             |    |

| 3.3.         | 9                                           |    |

| 3.3.<br>3.3. |                                             |    |

| ა.ა.<br>3.3. |                                             |    |

| 3.4          |                                             |    |

| 3.5          |                                             |    |

| 3.6          |                                             |    |

| 3.7          |                                             |    |

| 3.8          | USB interface connector USB1                | 17 |

| 3.9          | •                                           |    |

| 3.10         |                                             |    |

| 3.11         |                                             |    |

| 3.12         |                                             |    |

| 3.13         | 3 V850ES/HG2 memory map                     | 25 |

| 4.           | EB-V850ES/HG2-EE installation and operation | 26 |

| 4.1          | Getting started                             | 26 |

| 4.1.         | .1 CD-ROM contents                          | 26 |

| 5.           | Hardware installation                       | 27 |

| 6.           | Software installation                       | 27 |

| 6.1          |                                             |    |

| 6.2          |                                             |    |

| 6.3          |                                             |    |

| 6.4          |                                             |    |

| 6.4.<br>6.4. |                                             |    |

| 6.4.<br>6.4. |                                             |    |

| 6.5          |                                             |    |

|              | · · · · · · · · · · · · · · · · · · ·       |    |

| 6.6              | Driver Uninstallation                     | 42 |

|------------------|-------------------------------------------|----|

| 7.               | FPL FLASH programming software            | 44 |

| 7.1              | Introduction                              | 44 |

| 7.2              | Starting up the GUI Software              |    |

| 7.3              | Toolbar                                   |    |

| 7.4              | Menu Bar                                  |    |

| 7.4.1            |                                           |    |

| 7.4.2            |                                           |    |

| 7.4.3            |                                           |    |

| 7.4.4            | <del></del>                               |    |

| 7.5              | Programmer Parameter Window               | 56 |

| 8.               | How to use FPL FLASH programming software | 57 |

| (1)              | Installing the FPL GUI software           | 57 |

| (2)              | Installing the driver                     |    |

| (3)              | Installing the parameter file             |    |

| (4)              | Connecting and starting                   |    |

| ( <del>5</del> ) | Setting the programming environment       |    |

| (6)              | Selecting a user program                  |    |

| (7)              | [Autoprocedure(EPV)] command execution    |    |

| (8)              | Terminating the GUI                       | 63 |

| (9)              | Execute "CountDownTimer" application      |    |

| (10)             | Restarting the GUI                        | 63 |

| 9.               | TROUBLESHOOTING                           | 64 |

|                  |                                           |    |

| 10.              | On-Board debugging                        | 66 |

| 10.1             | Monitor resources                         | 67 |

| 10.1             |                                           |    |

| 10.1             | ·                                         |    |

| 10.1             |                                           |    |

| 10.1             |                                           |    |

|                  | .5 Clock operation                        |    |

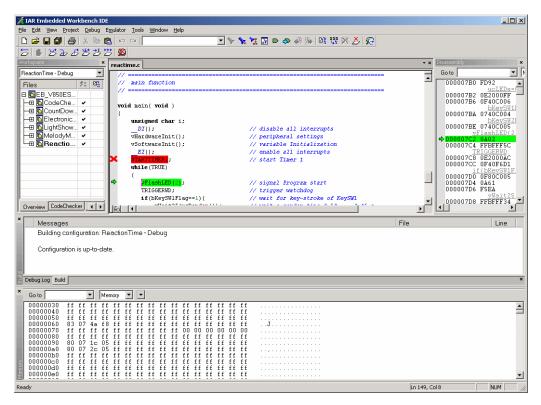

|                  | IAR sample session                        |    |

| 10.2             | IAK sample session                        | 09 |

| 11.              | Sample programs                           | 75 |

| 11.1             |                                           |    |

| 11.2             |                                           |    |

| 11.3             |                                           |    |

| 11.4             |                                           |    |

| 11.5             |                                           |    |

| 11.6             | ,                                         |    |

| 11.7             | Reaction time measurement                 | 78 |

| 12.              | Cables                                    | 79 |

|                  |                                           |    |

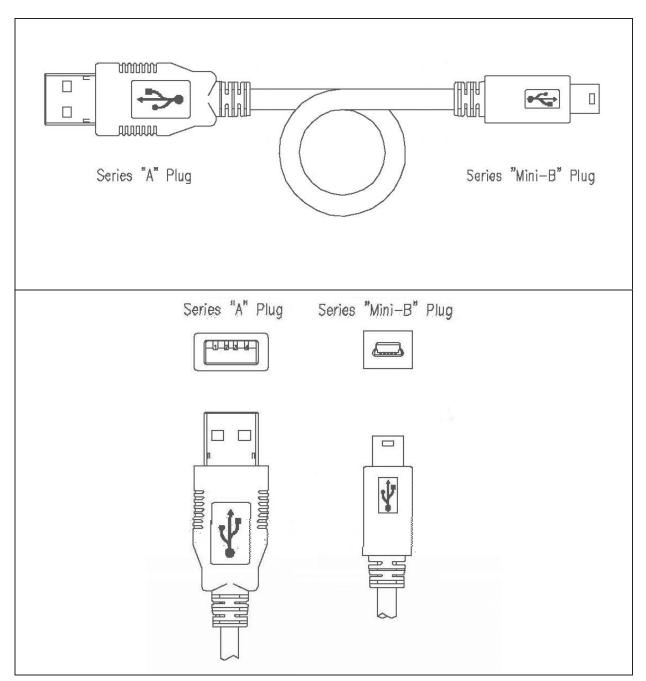

| 12.1             | USB interface cable (Mini-B type)         | 79 |

EB-V850ES/HG2-EE

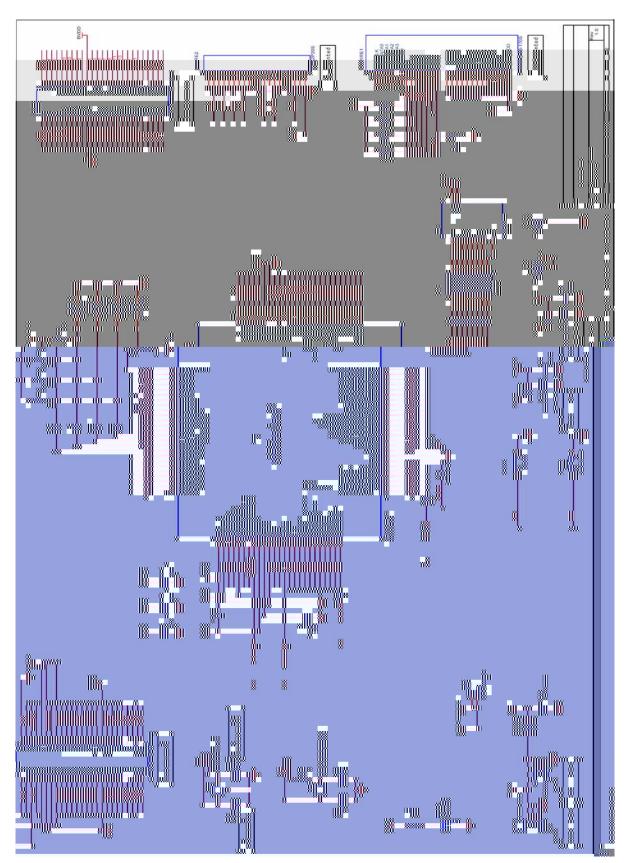

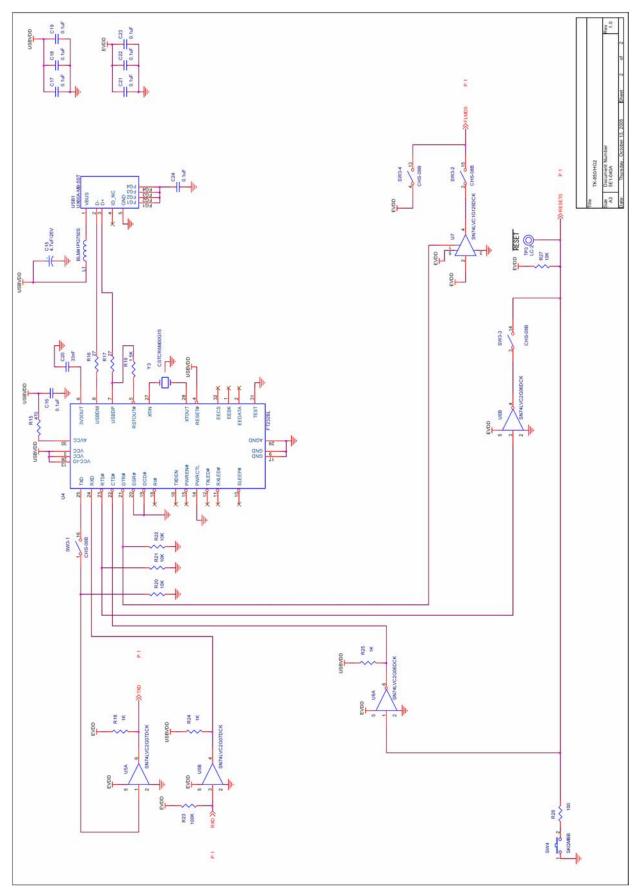

| 13. | Schematics | 80 |

|-----|------------|----|

**NEC**

# **List of Figures**

|             | EB-V850ES/HG2-EE system configuration                             |    |

|-------------|-------------------------------------------------------------------|----|

| Figure 2: E | EB-V850ES/HG2-EE board connectors, switches and LED's             | 13 |

| Figure 3: 0 | Connector USB1, USB Mini-B Type Host Connector Pin Configuration  | 17 |

| Figure 4: 0 | On-chip debugging system configuration                            | 18 |

|             | External connectors CN1 and CN2                                   |    |

|             | Placement of soldering bridges                                    |    |

|             | Add New Hardware Wizard (Windows 98SE)                            |    |

|             | Search Method (Windows 98SE)                                      |    |

|             | Search Location Specification (Windows 98SE)                      |    |

|             | Checking Driver to Be Installed (Windows 98SE)                    |    |

|             | Installation Completion (Windows 98SE)                            |    |

|             | Found New Hardware Wizard 1 (Windows 2000)                        |    |

|             | Search Method 1 (Windows 2000)                                    |    |

|             | Driver File Location 1 (Windows 2000)                             |    |

|             | Address Specification 1 (Windows 2000)                            |    |

|             | Driver File Search 1 (Windows 2000)                               |    |

|             | USB Driver Installation Completion 1 (Windows 2000)               |    |

|             | Found New Hardware Wizard 2 (Windows 2000)                        |    |

|             | Search Method 2 (Windows 2000)                                    |    |

|             | Driver File Location 2 (Windows 2000)                             |    |

|             | Address Specification 2 (Windows 2000)                            |    |

|             | Driver File Search 2 (Windows 2000)                               |    |

|             | USB Driver Installation Completion 2 (Windows 2000)               |    |

|             | Found New Hardware Wizard 1 (Windows XP)                          |    |

|             | Search Location Specification 3 (Windows XP)                      |    |

|             | Windows XP Logo Testing 3 (Windows XP)                            |    |

|             | USB Driver Installation Completion 1 (Windows XP)                 |    |

|             |                                                                   |    |

|             | Found New Hardware Wizard 2 (Windows XP)                          |    |

|             | Search Location Specification 2 (Windows XP)                      |    |

|             | Windows XP Logo Testing 2 (Windows XP)                            |    |

|             | USB Serial Port2 Driver Installation Completion (Windows XP)      |    |

|             | Device Manager                                                    |    |

|             | Driver Uninstallation                                             |    |

| Figure 34:  | Driver Uninstaller                                                | 42 |

| Figure 35:  | Completion of Driver Uninstallation.                              | 43 |

|             | GUI Software Main Window                                          |    |

|             | Toolbar Buttons                                                   |    |

|             | [ <u>File</u> ] Menu                                              |    |

|             | HEX File Selection Window                                         |    |

|             | [Device] Menu                                                     |    |

|             | Device Setup Window - Standard                                    |    |

|             | Setup Window - Parameter File Selection                           |    |

|             | Parameter File Selection Window                                   |    |

|             | Setup Window - Communication interface to device                  |    |

|             | Setup Window - Supply Oscillator Selection                        |    |

|             | Setup Window - Operation Mode                                     |    |

|             | Device Setup Window - Advance                                     |    |

|             | Setup Window - Command options                                    |    |

| Figure 49:  | [ <u>V</u> iew] Menu                                              | 54 |

|             | [ <u>H</u> elp] Menu                                              |    |

|             | About FPL Window                                                  |    |

| Figure 52:  | Programmer Parameter Window                                       | 56 |

|             | GUI Software Startup Screen                                       |    |

|             | <standard device="" setup=""> Dialog Box</standard>               |    |

|             | Parameter File Selection                                          |    |

|             | Port Selection                                                    |    |

|             | <standard device="" setup=""> Dialog Box after Setting</standard> |    |

|             | <advance device="" setup=""> Dialog Box</advance>                 |    |

#### 1. Introduction

*EB-V850ES/HG2-EE* is a demonstration kit for the NEC's H\_Line V850ES microcontroller family. It supports On-Board debugging, FLASH programming and real time execution of application programs. The board is prepared to be connected to user hardware parts such as digital I/O or analogue signals.

#### 1.1 Main features of EB-V850ES/HG2-EE

- Easy to use device demonstration capabilities

EB-V850ES/HG2-EE contains elements to easily demonstrate simple I/O-functions, i.e. push buttons,

7 segment LED output, AD reference voltage, I/O lines, UART serial interface.

- Power supply via USB interface

EB-V850ES/HG2-EE is powered via USB interface, no separate power supply is needed.

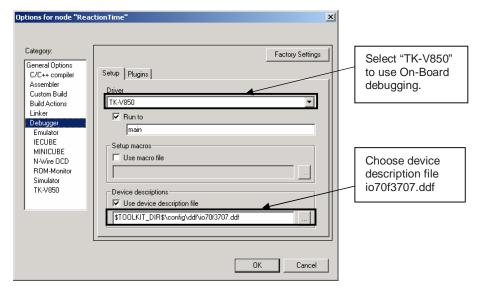

- On-Board debug function

The EB-V850ES/HG2-EE supports an On-Board debug function by using the IAR C-SPY debugger, without a need of additional debug hardware. It allows FLASH programming and supports standard debug functions i.e. code execution, single stepping, software breakpoints, memory manipulation etc.

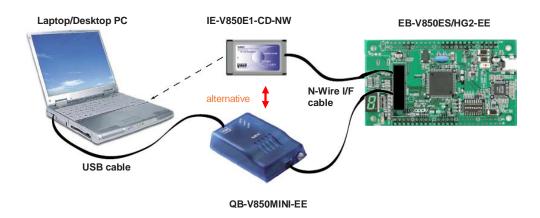

- N-Wire debugging

The EB-V850ES/HG2-EE is prepared to be equipped with a KEL adapter in order to connect the QB-V850MINI-EE or IE-V850E1-CD-NW On-Chip debug emulator to use On-Chip debug function of the V850ES/HG2 device. Please note, the QB-V850MINI-EE and IE-V850E1-CD-NW are separate products from NEC and there are not included in this starterkit package.

- FPL, FLASH programming software

A windows based FLASH programming software allows to select and download application programs to the EB-V850ES/HG2-EE board for evaluation purposes.

- Analogue to digital signal conversion is supported

- Various input / output signals available, such as

- All I/O ports prepared to be connected to user hardware

- Timer input / output signals

- ° Two or three wire serial I/O

- UART interface, via USB UART chip FT232

- 16 analogue input lines

- ° 7 segment LED

- ° 2 push buttons prepared for external interrupt generation

- The IAR Embedded Workbench for V850 and the IAR C-SPY debugger / simulator are included.

These packages are restricted in such that maximum program code size is limited to 16 kByte.

- Full documentation is included for the NEC V850ES/HG2 device, the IAR Systems Embedded Workbench, IAR Systems C-SPY debugger / simulator and the NEC FPL FLASH programming software.

EB-V850ES/HG2-EE is not intended for code development. NEC does not allow and does not support in any way any attempt to use EB-V850ES/HG2-EE in a commercial or technical product.

#### 1.2 System requirements

**HOST PC** A PC supporting Windows 98SE, Windows ME, Windows 2000 or

Windows XP is required for the IAR Systems Embedded Workbench

demo-version and the FPL FLASH programming software.

Pentium 166 MHz (at least), 128 MB of RAM, 256-color display (1024 \* 768), mouse, CD-ROM drive and 200 Mbytes of free hard disk space are

required to install the tool packages.

Above listed requirements are valid for the IAR Systems Embedded

Workbench and the FPL FLASH programming software.

Host interface USB interface that enables communication based on USB (Ver1.1 or

later)

# 1.3 Package contents

Please verify that you have received all parts listed in the package contents list attached to the EB-V850ES/HG2-EE package. If any part is missing or seems to be damaged, please contact the dealer from whom you received your EB-V850ES/HG2-EE starterkit.

Note: Updates to this User Manual, additional documentation and/or utilities for EB-V850ES/HG2-EE

starterkit, if available, may be downloaded from the NEC WEB page(s) at

http://www.eu.necel.com/updates.

#### 1.4 Trademarks

IAR Embedded Workbench, visualSTATE, IAR MakeApp and C-SPY are registered trademarks of IAR Systems AB. Microsoft and Windows are registered trademarks of Microsoft Corporation. Adobe and Acrobat Reader are registered trademarks of Adobe Systems Incorporated.

All other product names are trademarks or registered trademarks of their respective owners.

# 2. EB-V850ES/HG2-EE system configuration

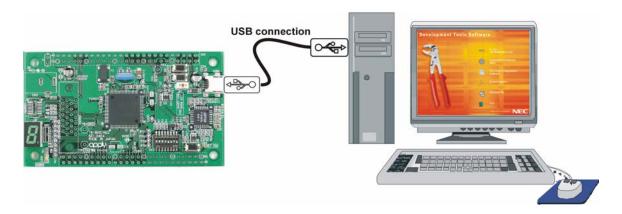

The EB-V850ES/HG2-EE system configuration is given in the diagram below:

Figure 1: EB-V850ES/HG2-EE system configuration

#### 2.1 EB-V850ES/HG2-EE

*EB-V850ES/HG2-EE* is a demonstration kit for the NEC H\_Line V850ES family devices. As a typical microcontroller from H\_Line family the V850ES/HG2 device (μPD70F3707) is used. The board is connected to the host system via a USB interface cable. The host system may be used for On-Board debugging or FLASH programming and to allow execution of application programs on the V850ES/HG2 device.

The *EB-V850ES/HG2-EE* board is equipped with an 5.0000 MHz oscillator, allows running the V850ES/HG2 microcontroller at 20MHz. Sub-clock is provided with 32.768 kHz.

#### 2.2 Host computer

The USB host interface enables communication to the *EB-V850ES/HG2-EE* board. The USB UART chip FT232 allows application software to access the USB device in the same way as it would access a standard RS232 interface. The FTDI's Virtual COM Port (VCP) driver appears to the windows system as an extra Com Port, in addition to any existing hardware Com Ports.

#### 2.3 Power supply via USB interface

*EB-V850ES/HG2-EE* is powered by USB interface, no separate power supply is needed. The USB interface provides the *EB-V850ES/HG2-EE* board with 5V supply voltage.

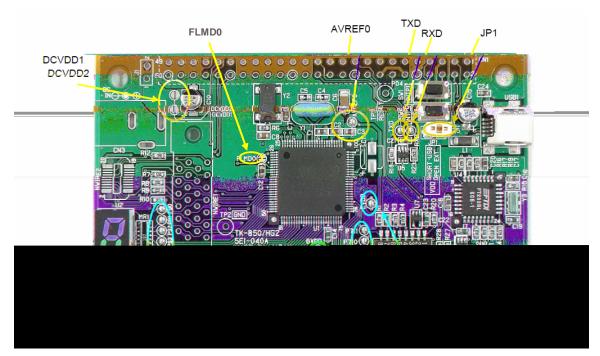

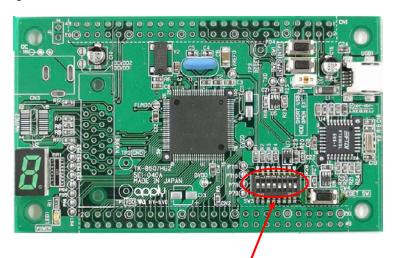

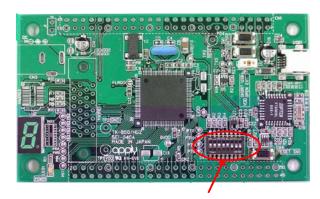

# 3. EB-V850ES/HG2-EE board components

The *EB-V850ES/HG2-EE* board is equipped with push buttons, a 7 segment LED and several connectors in order to be connected to user hardware or host computers.

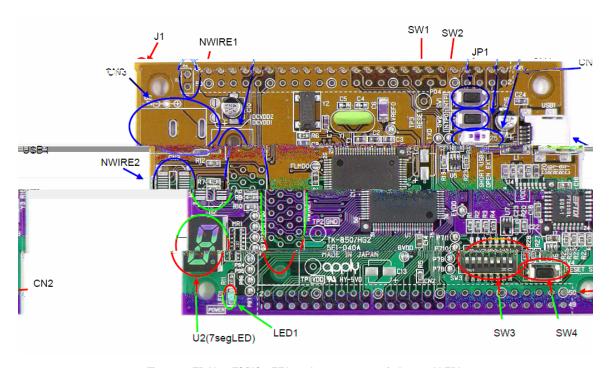

Figure 2: EB-V850ES/HG2-EE board connectors, switches and LED's

Some of the *EB-V850ES/HG2-EE* components are free for user application hardware and software. Please read the user's manual of the V850ES/HG2 device carefully to get information about the electrical specification of the available I/O ports before you connect any external signal to the *EB-V850ES/HG2-EE* board.

#### 3.1 User button SW1

SW1 is a push button connecting VSS to external interrupt input INTP1 of the microcontroller. This is equal to port P04 of the V850ES/HG2 device. The port may be programmed to generate interrupt INTP1. The necessary initialisation for this purpose is described in the user's manual of the V850ES/HG2 device. Please note, when using SW1 turn ON the built-in pull-up resistor of V850ES/HG2 device, register PU0.

## 3.2 User button SW2

SW2 is a push button connecting VSS to external interrupt input INTP0 of the microcontroller. This is equal to port P03 of the V850ES/HG2 device. The port may be programmed to generate interrupt INTP0. The necessary initialisation for this purpose is described in the user's manual of the V850ES/HG2 device. Please note, when using SW2 turn ON the built-in pull-up resistor of V850ES/HG2 device, register PU0.

## 3.3 Configuration switch SW3

The dip-switch SW3 (Bits 1-4) controls the different operating modes of the *EB-V850ES/HG2-EE* board. The Bits 5-8 of dip-switch SW3 are for general-purpose input and are connected to the ports P78~P711 of the microcontroller.

#### 3.3.3 FLASH programming mode

For programming of the built-in FLASH memory of the V850ES/HG2 device by using the FPL FLASH programming GUI please configure switch SW3 as following:

| SW3   | Configuration |

|-------|---------------|

| Bit 1 | ON            |

| Bit 2 | OFF           |

| Bit 3 | ON            |

| Bit 4 | ON            |

Table 3: SW3, FLASH programming mode

## 3.3.4 N-Wire debugging mode

To enable N-Wire On-Chip debugging by using the QB-V850MINI-EE or IE-V850E1-CD-NW On-Chip debug emulators please configure switch SW3 of the *EB-V850ES/HG2-EE* board as following:

| SW3   | Configuration |

|-------|---------------|

| Bit 1 | OFF           |

| Bit 2 | OFF           |

| Bit 3 | OFF           |

| Bit 4 | OFF           |

Table 4: SW3, N-Wire debugging mode

Please refer also to CHAPTER 3.9 N-WIRE CONNECTORS NWIRE1, NWIRE2 of this document.

# 3.3.5 General-purpose switches

The Bits 5-8 of dip-switch SW3 are for general-purpose inputs and are connected to the ports P78~P711 of the microcontroller. Switching Bits 5-8 to ON applies VSS to the corresponding port of the microcontroller. Switching Bits 5-8 to OFF applies VDD to the corresponding port.

| SW3   | V850ES/HG2 |

|-------|------------|

| Bit 5 | P78        |

| Bit 6 | P79        |

| Bit 7 | P710       |

| Bit 8 | P711       |

Table 5: SW3, general-purpose switches

#### 3.4 RESET button SW4

SW4 is a reset button. It activates the power on reset. It is connected to the reset circuit of the EB-V850ES/HG2-EE board.

# 3.5 Power LED LED1

LED1 is the Power LED. LED1 is activated if power is supplied to the EB-V850ES/HG2-EE board.

## 3.6 Power supply selector JP1

Jumper JP1 selects the power supply of the *EB-V850ES/HG2-EE* board. Closing jumper JP1 (default setting) supplies power (VCC = 5V) from the USB interface line. When opening JP1, external power can be supplied by using connectors CN3 or J1.

| JP1              | Mode                            |

|------------------|---------------------------------|

| closed (default) | Power supplied by USB interface |

| open             | External power supply           |

Table 6: Power supply selector, JP1

Note: When choosing external power supply, please open jumper JP1!

#### 3.7 External power supply

External power can be supply by connecting a 5V AC adapter to connector CN3 (not assembled). Per default, the external power is supplied to the connector CN1 only (pins 10, 12 and 16). To power the complete board via external power supply, the soldering bridges DCVDD1 and DCVDD2 must be closed.

| CN3        | Function |

|------------|----------|

| Center (1) | Vcc = 5V |

| Ring (2,3) | Gnd      |

Table 7: External power supply, connector CN3

Additionally a stabilizing 5V power supply can be connected directly to the connector J1 instead of using a 5V AC adapter. Also in this case the soldering bridges DCVDD1 and DCVDD2 must be closed.

| J1 | Function |

|----|----------|

| 1  | Vcc = 5V |

| 2  | Gnd      |

Table 8: External power supply, connector J1

Note: When using an external power supply, please open jumper JP1!

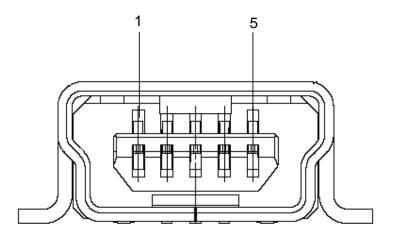

#### 3.8 USB interface connector USB1

USB1 connector allows connecting the IAR C-SPY debugger or the FPL FLASH programming software to the *EB-V850ES/HG2-EE* board in order to debug or program application software to the V850ES/HG2 device. The board power supply of 5V is also provided by this connector.

Additionally connector USB1 connects UARTA0 of the V850ES/HG2 device to the host system.

Figure 3: Connector USB1, USB Mini-B Type Host Connector Pin Configuration

| USB Connector<br>USB1 | Signal Name |

|-----------------------|-------------|

| 1                     | VBUS        |

| 2                     | D-          |

| 3                     | D+          |

| 4                     | N.C.        |

| 5                     | GND         |

Table 9: Pin Configuration of USB Connector USB1

For connection with the host machine, use a USB cable (Mini-B type). For confirmation, NEC Electronics used only the USB cable delivered with the *EB-V850ES/HG2-EE* board.

# 3.9 N-Wire connectors NWIRE1, NWIRE2

The NWIRE1 and NWIRE2 connectors (not assembled) do allow the connection of the QB-V850MINI-EE or alternative the IE-V850E1-CD-NW On-Chip debug emulators to the *EB-V850ES/HG2-EE* board in order to use On-Chip debug function (N-Wire) of the V850ES/HG2 device.

Figure 4: On-chip debugging system configuration

Please note that the QB-V850MINI-EE and IE-V850E1-CD-NW are separate products from NEC and are not included in this starterkit package.

To enable On-Chip debugging via N-Wire please configure switch SW3 of the *EB-V850ES/HG2-EE* board as following:

| SW3   | Configuration |

|-------|---------------|

| Bit 1 | OFF           |

| Bit 2 | OFF           |

| Bit 3 | OFF           |

| Bit 4 | OFF           |

| NWIRE1 | Signal<br>Name | description              | NWIRE1 | Signal<br>Name | description       |

|--------|----------------|--------------------------|--------|----------------|-------------------|

| A1     | TRCCLK         | not connected            | B1     | GND_0          | connected to VSS  |

| A2     | TRCDATA0       | not connected            | B2     | GND_1          | connected to VSS  |

| A3     | TRCDATA1       | not connected            | B3     | GND_2          | connected to VSS  |

| A4     | TRCDATA2       | not connected            | B4     | GND_3          | connected to VSS  |

| A5     | TRCDATA3       | not connected            | B5     | GND_4          | connected to VSS  |

| A6     | TRCEND         | not connected            | B6     | GND_5          | connected to VSS  |

| A7     | DDI            | connected to P52         | B7     | GND_6          | connected to VSS  |

| A8     | DCK            | connected to P54         | B8     | GND_7          | connected to VSS  |

| A9     | DMS            | connected to P55         | B9     | GND_8          | connected to VSS  |

| A10    | DDO            | connected to P53         | B10    | GND_9          | connected to VSS  |

| A11    | DRST_          | connected to P05         | B11    | GPIO2          | connected to VSS  |

| A12    | GPIO0          | connected to RESET0      | B12    | GPIO3          | connected to VSS  |

| A13    | GPIO1          | connected to FLMD0 logic | B13    | TRGT_VDD       | connected to EVDD |

Table 10: N-Wire connector NWIRE1

| NWIRE2 | Signal | description      | NWIRE2 | Signal Name | description        |

|--------|--------|------------------|--------|-------------|--------------------|

|        | Name   |                  |        |             |                    |

| 1      |        | VSS              | 11     |             | VSS                |

| 2      | DCK    | Connected to P54 | 12     | RESET0      | connected to RESET |

| 3      |        | VSS              | 13     |             | VSS                |

| 4      | DMS    | connected to P55 | 14     | FLMD0       | connected to FLMD0 |

| 5      |        | VSS              | 15     |             | VSS                |

| 6      | DDI    | connected to P52 | 16     |             | not connected      |

| 7      |        | VSS              | 17     |             | VSS                |

| 8      | DRST   | Connected to P05 | 18     | DDO         | connected to P53   |

| 9      |        | VSS              | 19     |             | VSS                |

| 10     |        | not connected    | 20     | EVDD        | connected to VDD   |

Table 11: N-Wire connector NWIRE2

# 3.10 External LED U2

The 7 segment LED U2 is connected to port P90-P97 of the V850ES/HG2 device. A low signal output at each port switches the corresponding LED on.

| Port V850ES/HG2 | Segment | LED U2 |

|-----------------|---------|--------|

| P90             | A       |        |

| P91             | В       |        |

| P92             | С       |        |

| P93             | D       |        |

| P94             | Е       |        |

| P95             | F       |        |

| P96             | G       |        |

| P97             | DP      |        |

Table 12: External LED U2

Example: The figures of 0 to 9 can be displayed by writing the following values to the port register P9.

| P9, register value | LED U2 | P9, register value | LED U2 |

|--------------------|--------|--------------------|--------|

| 0xC0               | 0      | 0x92               | 5      |

| 0xF9               | 1      | 0x83               | 6      |

| 0xA4               | 2      | 0xF8               | 7      |

| 0xB0               | 3      | 0x80               | 8      |

| 0x99               | 4      | 0x98               | 9      |

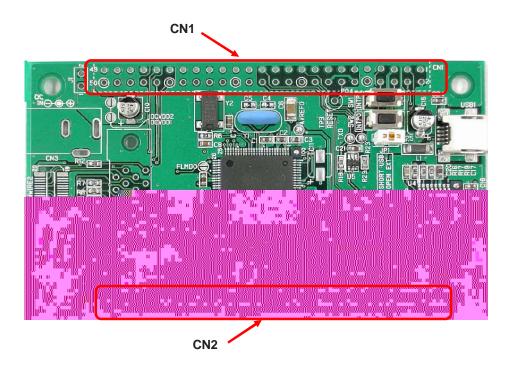

## 3.11 External connectors CN1 and CN2

CN1 and CN2 are connectors for external user hardware. Please read the user's manual of the V850ES/HG2 device carefully to get information about the electrical specification of the available I/O ports.

Figure 5: External connectors CN1 and CN2

| CN1      | Signal name | V850ES/HG2 Pin name                  | Comment                                                                              |

|----------|-------------|--------------------------------------|--------------------------------------------------------------------------------------|

| 1        | AVREF0      | AVREF0                               | Connected to VDD by soldering bridge                                                 |

| 2        | VSS         | AVSS, VSS, EVSS, BVSS                | , ,                                                                                  |

| 3        | P10         | P10/INTP9                            |                                                                                      |

| 4        | P11         | P11/INTP10                           |                                                                                      |

| 5        | EVDD        | EVDD                                 | Connected to VDD by soldering bridge                                                 |

| 6        | P78         | P78/ANI8                             | Connected to SW3-5 by soldering bridge                                               |

| 7        | P79         | P79/ANI9                             | Connected to SW3-6 by soldering bridge                                               |

| 8        | FLMD0       | FLMD0                                | Connected to FLMD0 control logic                                                     |

| 9        | VDD         | VDD                                  |                                                                                      |

| 10       | +12V        |                                      | Connected to CN3, J1                                                                 |

| 11       | VSS         | AVSS, VSS, EVSS, BVSS                |                                                                                      |

| 12       | +12V        |                                      | Connected to CN3, J1                                                                 |

| 13       | VDD         | VDD                                  |                                                                                      |

| 14       | RESET0      | RESET                                | Connected to reset circuit                                                           |

| 15       | VDD         | VDD                                  |                                                                                      |

| 16       | +12V        | 1                                    | Connected to CN3, J1                                                                 |

| 17       | P02         | P02 / NMI                            |                                                                                      |

| 18       | P03         | P03 / INTP0 / ADTRG                  | Connected to SW2                                                                     |

| 19       | P04         | P04 / INTP1                          | Connected to SW1                                                                     |

| 20       | P05         | P05 / INTP2 / DRST                   | Commoded to CVV I                                                                    |

| 21       | P06         | P06 / INTP3                          |                                                                                      |

| 22       | P40         | P40 / SIB0                           |                                                                                      |

| 23       | P41         | P41 / SOB0                           |                                                                                      |

| 24       | P42         | P42 / SCKB0                          |                                                                                      |

| 25       | P30         | P30 / TXDA0                          | Connected to RXD by soldering bridge                                                 |

| 26       | P31         | P31 / RXDA0 / INTP7                  | Connected to TXD by soldering bridge                                                 |

| 27       | P32         | P32 / ASCKA0 / TOP01 / TIP00 / TOP00 | Connected to TXD by soldering bridge                                                 |

| 28       | P33         | P33 / TIP01 / TOP01                  |                                                                                      |

| 29       | P34         | P34 / TIP10 / TOP10                  |                                                                                      |

| 30       | P35         | P35 / TIP11 / TOP11                  |                                                                                      |

| 31       | P36         | P36                                  |                                                                                      |

| 32       | P37         | P37                                  |                                                                                      |

| 33       | VSS         | AVSS, VSS, EVSS, BVSS                |                                                                                      |

| 34       | EVDD        | EVDD                                 | Connected to VDD by soldering bridge                                                 |

| 35       | P38         | P38 / TXDA2                          | Connected to VDD by soldering bridge                                                 |

| 36       | P39         | P39 / RXDA2 / INTP8                  |                                                                                      |

| 37       | P50         | P50 / KR0 / TIQ01 / TOQ01            |                                                                                      |

| 38       | P51         | P51 / KR1 / TIQ02 / TOQ02            |                                                                                      |

| -        | P52         | P52 / KR2 / TIQ03 / TOQ03 / DDI      | Connected to 4.7 kO pull up reciptor                                                 |

| 39<br>40 | P53         | P53 / KR3 / TIQ00 / TOQ00 / DDO      | Connected to 4.7 kΩ pull-up resistor  Connected to 4.7 kΩ pull-up resistor           |

| 41       | P54         | P54 / KR4 / DCK                      | · · ·                                                                                |

| 42       | P55         | P55 / KR5 / DMS                      | Connected to 4.7 kΩ pull-up resistor  Connected to 4.7 kΩ pull-up resistor           |

|          |             |                                      | Connected to 4.7 kg pull-up resistor  Connected to 7seg LED by soldering bridge      |

| 43       | P90<br>P91  | P90 / KR6 / TXDA1 P91 / KR7 / RXDA1  | Connected to 7seg LED by soldering bridge  Connected to 7seg LED by soldering bridge |

|          | -           | P92 / TIQ11 / TOQ11                  | Connected to 7seg LED by soldering bridge  Connected to 7seg LED by soldering bridge |

| 45       | P92         |                                      | 0 , 0 0                                                                              |

| 46       | P93         | P93 / TIQ12 / TOQ12                  | Connected to 7seg LED by soldering bridge                                            |

| 47       | P94         | P94 / TIQ13 / TOQ13                  | Connected to 7seg LED by soldering bridge                                            |

| 48       | P95         | P95 / TIQ10 / TOQ10                  | Connected to 7seg LED by soldering bridge                                            |

| 49       | P96         | P96 / TIP21 / TOP20                  | Connected to 7seg LED by soldering bridge                                            |

| 50       | P97         | P97 / SIB1 / TIP20 / TOP20           | Connected to 7seg LED by soldering bridge                                            |

Table 13: Connector CN1

| CN2 | Signal name  | V850ES/HG2 Pin name   | Comment                                  |

|-----|--------------|-----------------------|------------------------------------------|

| 1   | P98          | P98 / SOB1            | Comment                                  |

| 2   | P99          | P99 / SCKB1           |                                          |

| 3   | P910         | P910                  |                                          |

| 4   | P911         | P911                  |                                          |

| 5   | P912         | P912                  |                                          |

| 6   | P913         | P913 / INTP4 / PCL    |                                          |

| 7   | P914         | P914 / INTP5          |                                          |

| 8   | P915         | P915 / INTP6          |                                          |

| 9   | P710         | P710 / ANI10          | Connected to SW3-7 by soldering bridge   |

| 10  | P711         | P711 / ANI11          | Connected to SW3-8 by soldering bridge   |

| 11  | PCM0         | PCM0                  | Connected to SW 3-6 by soldering bridge  |

| 12  | PCM1         | PCM1                  |                                          |

| 13  | PCM2         | PCM2                  |                                          |

| 14  | PCM3         | PCM3                  |                                          |

|     | PCT0         | PCT0                  |                                          |

| 15  | PCT1         | PCT1                  |                                          |

| 16  |              |                       |                                          |

| 17  | PCT4<br>PCT6 | PCT4 PCT6             |                                          |

| 18  |              |                       |                                          |

| 19  | VSS          | AVSS, VSS, EVSS, BVSS | Open and the VDD by and design a beinder |

| 20  | BVDD         | BVDD                  | Connected to VDD by soldering bridge     |

| 21  | PDL0         | PDL0                  |                                          |

| 22  | PDL1         | PDL1                  |                                          |

| 23  | PDL2         | PDL2                  |                                          |

| 24  | PDL3         | PDL3                  |                                          |

| 25  | PDL4         | PDL4                  |                                          |

| 26  | PDL5         | PDL5 / FLMD1          | Connected to 10 kΩ pull-down resistor    |

| 27  | PDL6         | PDL6                  |                                          |

| 28  | PDL7         | PDL7                  |                                          |

| 29  | PDL8         | PDL8                  |                                          |

| 30  | PDL9         | PDL9                  |                                          |

| 31  | PDL10        | PDL10                 |                                          |

| 32  | PDL11        | PDL11                 |                                          |

| 33  | PDL12        | PDL12                 |                                          |

| 34  | PDL13        | PDL13                 |                                          |

| 35  | P715         | P715 / ANI15          |                                          |

| 36  | P714         | P714 / ANI14          |                                          |

| 37  | P713         | P713 / ANI13          |                                          |

| 38  | P712         | P712 / ANI12          |                                          |

| 39  | PCS0         | PCS0                  |                                          |

| 40  | PCS1         | PCS1                  |                                          |

| 41  | P00          | P00 / TIP31 / TOP31   |                                          |

| 42  | P01          | P01 / TIP30 / TOP30   |                                          |

| 43  | P77          | P77 / ANI7            |                                          |

| 44  | P76          | P76 / ANI6            |                                          |

| 45  | P75          | P75 / ANI5            |                                          |

| 46  | P74          | P74 / ANI4            |                                          |

| 47  | P73          | P73 / ANI3            |                                          |

| 48  | P72          | P72 / ANI2            |                                          |

| 49  | P71          | P71 / ANI1            |                                          |

| 50  | P70          | P70 / ANI0            |                                          |

Table 14: Connector CN2

# 3.12 Soldering Bridges

Some terminals of the V850ES/HG2 device can be customized by opening respectively closing the corresponding soldering bridge. By opening the soldering bridge the connection to the onboard circuit is cut. Accordingly, the corresponding signals can be used for external user hardware using the connectors CN1 and CN2. For more details please refer to the board schematics, pages 80-81.

Figure 6: Placement of soldering bridges

| Soldering bridge name | Factory setting | Comment                                                                                                                                                                               |

|-----------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P90 – P97             | Closed          | Connected to 7seg LED via 1 KΩ resistor                                                                                                                                               |

| P78 ~ P711            | Closed          | Connected to switch SW3, Bits 5-8                                                                                                                                                     |

| RXD, TXD              | Closed          | Connection of ports RXDA0 / P31 and TXDA0 / P30 to the FT232 UART/USB circuit.                                                                                                        |

| FLMD0                 | Open            | By closing the soldering bridge the FLMD0 pin is connected to port pin P37. This allows by using FLASH self-programming to enable or disable FLASH write operations via port pin P37. |

| AVREF0                | Closed          | Connected to VDD                                                                                                                                                                      |

| BVDD                  | Closed          | Connected to VDD                                                                                                                                                                      |

| EVDD                  | Closed          | Connected to VDD                                                                                                                                                                      |

| DCVDD1, DCVDD2        | Open            | When using external power supply, via connector CN3 or J1, the soldering bridges must be closed.                                                                                      |

Table 15: Soldering brigdes

# 3.13 V850ES/HG2 memory map

The V850ES/HG2 memory layout is shown in the table below.

|         | 0x3FFFFFF<br>0x3FFF000 | SFR Area                                                                                | Free for user application             |  |

|---------|------------------------|-----------------------------------------------------------------------------------------|---------------------------------------|--|

|         | 0x3FFEFFF<br>0x3FFC000 | 12 KB Internal RAM                                                                      | software                              |  |

| s area  | 0x3FFBFFF<br>0x3FF0000 | Access prohibited area                                                                  |                                       |  |

| Address | 0x3FEFFFF<br>0x0100000 | Programmable peripheral I/O area or use prohibited area (program fetch prohibited area) |                                       |  |

|         | 0x00FFFF<br>0x0040000  | Access prohibited area                                                                  |                                       |  |

|         | 0x003FFFF<br>0x0000000 | 256 KB Flash memory                                                                     | Free for user application<br>Software |  |

Table 16: V850ES/HG2 memory map

# 4. EB-V850ES/HG2-EE installation and operation

## 4.1 Getting started

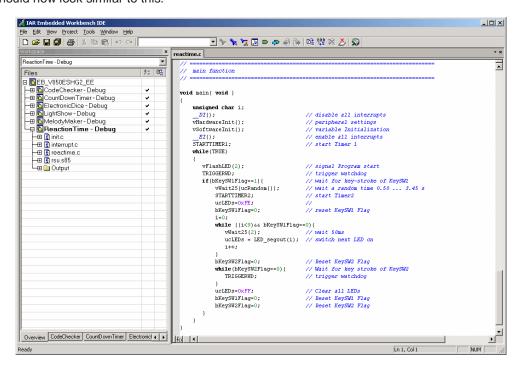

The IAR C-SPY debugger allows to download and debug application software on the *EB-V850ES/HG2-EE* starterkit hardware. Additionally the FPL FLASH programming software can be used for simple FLASH programming of the V850ES/HG2 internal FLASH memory. As communication interface between the host computer and the *EB-V850ES/HG2-EE* board a USB interface line is needed. Before you can download, debug or execute an application programs, hardware and software must be installed properly.

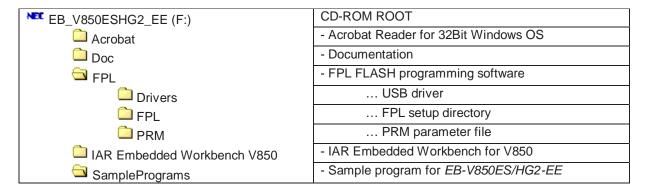

#### 4.1.1 CD-ROM contents

The CD-ROM shows following directory structure:

Table 17: EB-V850ES/HG2-EE CD-ROM directory structure

#### 5. Hardware installation

After unpacking *EB-V850ES/HG2-EE*, connect the board to your host computer by using the provided USB interface cable. When *EB-V850ES/HG2-EE* is connected, the USB driver needs to be installed on the host machine. Please refer to the following **CHAPTER 6 SOFTWARE INSTALLATION**.

#### 6. Software installation

The EB-V850ES/HG2-EE package comes with several software demo packages:

- IAR Systems Embedded Workbench for V850, including C compiler, assembler, linker, librarian and IAR C-SPY debugger / simulator

- FPL FLASH programming software

- Sample programs

The IAR Systems Embedded Workbench and the FPL FLASH programming GUI must be installed on your PC. For detailed installation hints, refer to the following chapters and to the corresponding documentation of the IAR Embedded Workbench.

#### 6.1 IAR Systems Embedded Workbench for V850 installation

To install the IAR Systems Embedded Workbench for V850 including the C-SPY debugger / simulator, select the SETUP program in the directory \IAR Embedded Workbench V850\ewv850\ of the CDROM. The setup dialogues will guide you through the installation process.

## 6.2 FPL FLASH programming GUI installation

To install the FPL FLASH programming GUI select the SETUP program in the directory \FPL\ of the CDROM. The setup dialogues will guide you through the installation process.

#### 6.3 Sample program installation

To install the demonstration programs for the *EB-V850ES/HG2-EE* board select the SETUP program in the directory \SampleProgram\ of the CDROM. The setup dialogues will guide you through the installation process.

#### 6.4 USB Driver Installation

When the *EB-V850ES/HG2-EE* board and FPL is used, the driver needs to be installed on the host machine. Install the driver according to the following procedure:

| Installation on Windows 98SE/Me | Page 28 |

|---------------------------------|---------|

| Installation on Windows 2000    | Page 30 |

| Installation on Windows XP      | Page 36 |

#### 6.4.1 Installation on Windows 98SE/Me

1. When the EB-V850ES/HG2-EE board is connected with the host machine, the board is recognized by Plug and Play, and the wizard for adding new hardware is started. Click Next>.

Figure 7: Add New Hardware Wizard (Windows 98SE)

2. The window below is displayed. So, check that "Search for a suitable driver ..." is selected, then click Next>.

Figure 8: Search Method (Windows 98SE)

3. Check the "Specify a location" check box only and enter "C:\Program Files\NECTools32\FPL\DRIVER" in the address bar, then click Next>.

Add New Hardware Wizard Windows will search for new drivers in its driver database on your hard drive, and in any of the following selected locations. Click Next to start the search. Floppy disk drives CD-ROM drive - I Microsoft-Windows Update <1> Check "Specify a location" only. C:\Program Files\NECTools32\ FPL\Di ₹. Browse... Next > Cancel < Back <3> Click. <2> Enter "C:\Program Files\NECTools32\FPL\DRIVER".

Figure 9: Search Location Specification (Windows 98SE)

Remark If the installation destination folder is changed at the time of GUI software installation, enter "new-folder\DRIVER".

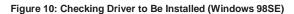

4. The window below is displayed. Click Next>.

5. When the window below is displayed, the installation of the USB driver is completed. Click Finish. The installation of the USB Serial Port driver is then automatically performed.

Figure 11: Installation Completion (Windows 98SE)

# 6.4.2 Installation on Windows 2000

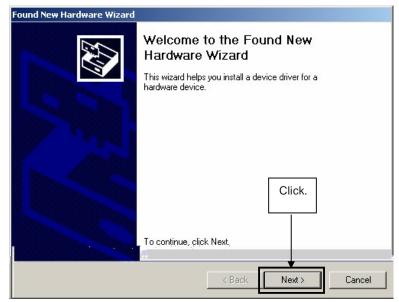

1. When the EB-V850ES/HG2-EE board is connected with the host machine, the board is recognized by Plug and Play, and the wizard for finding new hardware is started. Click Next>.

Figure 12: Found New Hardware Wizard 1 (Windows 2000)

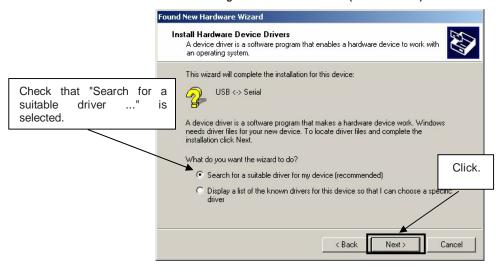

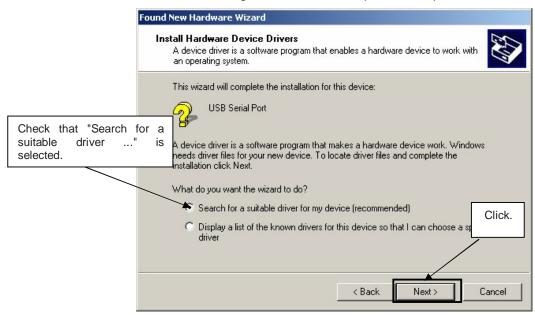

2. The window below is displayed. So, check that "Search for a suitable driver ..." is selected, then click Next>.

Figure 13: Search Method 1 (Windows 2000)

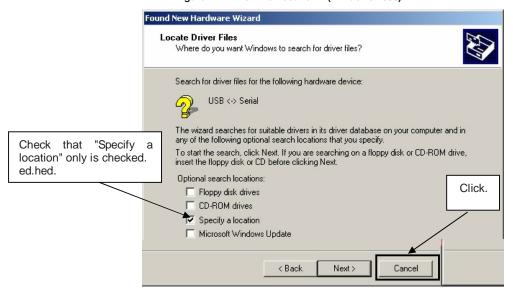

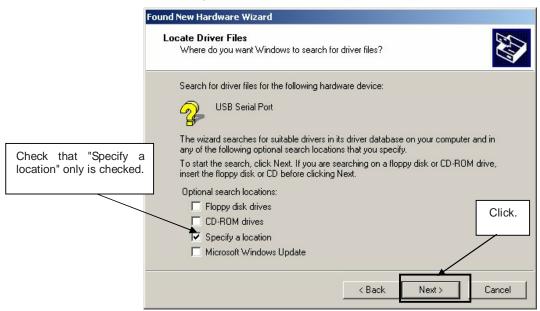

3. Check the "Specify a location" check box only, then click Next>

Figure 14: Driver File Location 1 (Windows 2000)

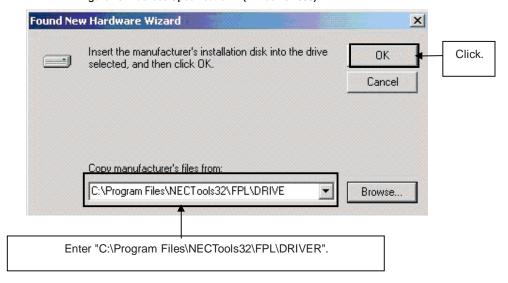

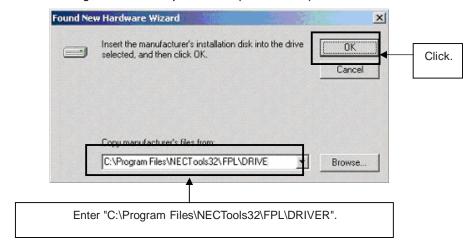

4. Enter "C:\Program Files\NECTools32\FPL\DRIVER" in the address bar, then click OK.

Figure 15: Address Specification 1 (Windows 2000)

Remark If the installation destination folder is changed at the time of GUI software installation, enter "new-folder\FPL\DRIVER".

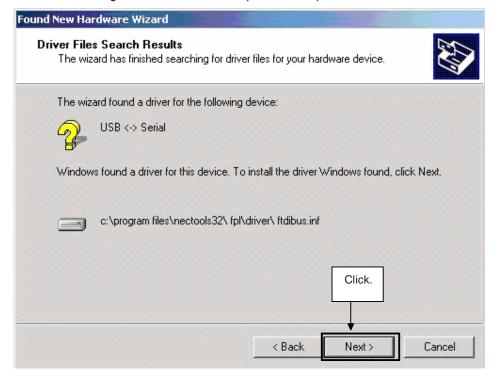

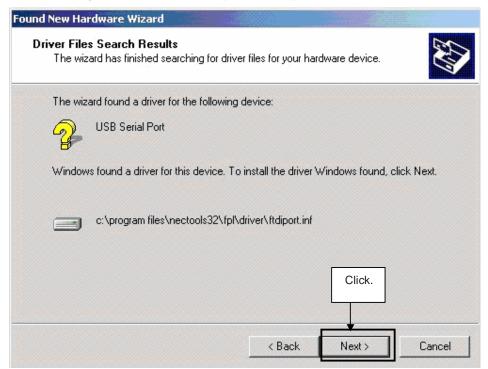

5. Click Next>.

Figure 16: Driver File Search 1 (Windows 2000)

6. Click Finish to complete the installation of the USB driver.

Figure 17: USB Driver Installation Completion 1 (Windows 2000)

7. Proceed to the installation of the USB Serial Port driver. Click Next>.

Figure 18: Found New Hardware Wizard 2 (Windows 2000)

8. The window below is displayed. So, check that "Search for a suitable driver ..." is selected, then click Next>.

Figure 19: Search Method 2 (Windows 2000)

9. Check the "Specify a location" check box only, then click Next>

Figure 20: Driver File Location 2 (Windows 2000)

10. Enter "C:\Program Files\NECTools32\FPL\DRIVER" in the address bar, then click OK.

Figure 21: Address Specification 2 (Windows 2000)

Remark If the installation destination folder is changed at the time of GUI software installation, enter "new-folder\DRIVER".

# 11. Click Next>

Figure 22: Driver File Search 2 (Windows 2000)

12. Click Finish to complete the installation of the USB driver.

Figure 23: USB Driver Installation Completion 2 (Windows 2000)

# 6.4.3 Installation on Windows XP

1. When the *EB-V850ES/HG2-EE* board is connected with the host machine, the board is recognized by Plug and Play, and the wizard for finding new hardware is started. Check that "Install from a list or specific ..." is selected, then click Next>.

Found New Hardware Wizard Welcome to the Found New Hardware Wizard This wizard helps you install software for: USB <-> Serial If your hardware came with an installation CD or floppy disk, insert it now. What do you want the wizard to do? Check that "Install from a list Install the software automatically (Recommended) or specific ..." is selected. Click. Notall from a list or specific location (Advanced) Click Next to continue. < Back Next> Cancel

Figure 24: Found New Hardware Wizard 1 (Windows XP)

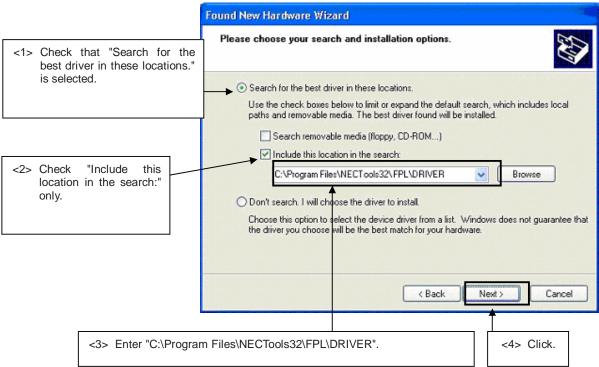

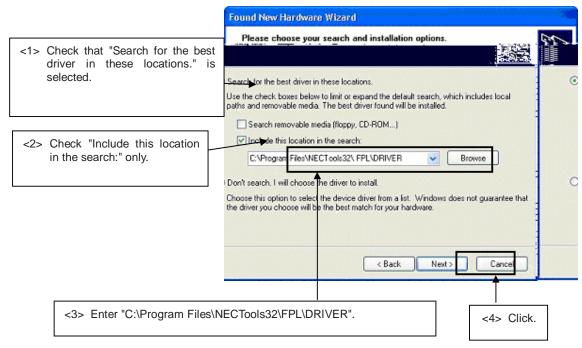

2. Check that "Search for the best driver in these locations." is selected. Check the "Include this location in the search:" check box and enter "C:\Program Files\NECTools32\FPL\DRIVER" in the address bar, then click Next>.

Figure 25: Search Location Specification 3 (Windows XP)

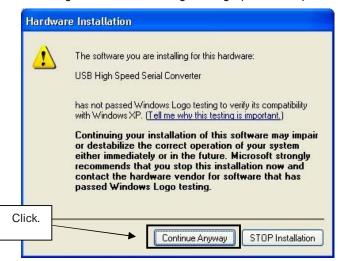

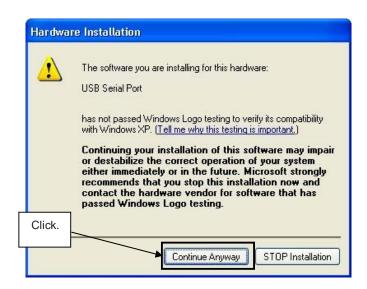

3. As shown below, "has not passed Windows Logo testing to verify its compatibility with Windows XP." is displayed. Click Continue Anyway.

Figure 26: Windows XP Logo Testing 3 (Windows XP)

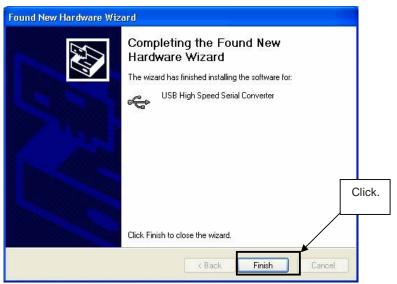

4. When the window below is displayed, the installation of the USB driver is completed. Click Finish.

Figure 27: USB Driver Installation Completion 1 (Windows XP)

5. Proceed to the installation of the USB Serial Port driver. Click Next>

Found New Hardware Wizard Welcome to the Found New Hardware Wizard This wizard helps you install software for: **USB Serial Port** If your hardware came with an installation CD or floppy disk, insert it now. What do you want the wizard to do? Check that "Install from a list O Install the software automatically (Recommended) Click. or specific ..." is selected. Click Next to continue. k Back Next> Cancel

Figure 28: Found New Hardware Wizard 2 (Windows XP)

6. Check that "Search for the best driver in these locations." is selected. Check the "Include this location in the search:" check box and enter "C:\Program Files\NECTools32\FPL\DRIVER", then click Next>.

Figure 29: Search Location Specification 2 (Windows XP)

7. As shown below, "has not passed Windows Logo testing to verify its compatibility with Windows XP." is displayed. Click Continue Anyway.

Figure 30: Windows XP Logo Testing 2 (Windows XP)

8. When the window below is displayed, the installation of the USB driver is completed. Click Finish.

Figure 31: USB Serial Port2 Driver Installation Completion (Windows XP)

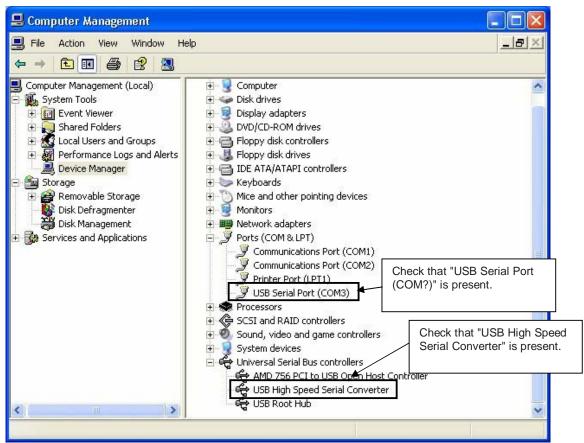

#### 6.5 Confirmation of USB Driver Installation

After installing the two types of drivers, check that the drivers have been installed normally, according to the procedure below. When using the *EB-V850ES/HG2-EE* board in combination with FPL GUI, the information to be checked here is needed.

By clicking the "Device Manager" tab, check that the drivers are installed normally.

Figure 32: Device Manager

For Windows 98SE/Me

Caution Do not select Update and Erase when communicating with the target device.

### For Windows 2000/XP

Caution Do not perform "Hardware Modification Scan" when communicating with the target device.

Remark In the GUI port list box, the same communication port as COM? of USB Serial Port (COM?) needs to be selected.

If the drivers above are not displayed, or the mark " $\times$ " or "!" is prefixed, refer to **CHAPTER 9 TROUBLESHOOTING**.

#### 6.6 Driver Uninstallation

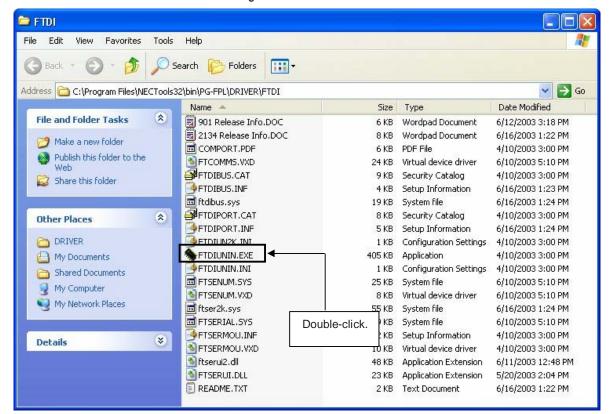

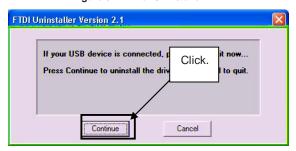

The driver uninstallation program is installed on the host machine when the FPL software is installed. Use the procedure below for driver uninstallation.

- 1. When using Windows XP, log on as the computer administrator. When using Windows 2000, log on as the Administrator.

- 2. Double-click in the order from "My Computer" to "(C:)" to "Program Files" to "NECTools32" to "FPL" to "DRIVER". "Ftdiunin.exe" is displayed. Double-click "Ftdiunin.exe".

Figure 33: Driver Uninstallation

3. Click Continue

Figure 34: Driver Uninstaller

4. Click Finish to complete driver uninstallation.

Figure 35: Completion of Driver Uninstallation

Caution If the GUI software is uninstalled earlier, "Ftdiunin.exe" is also deleted. At this time, delete "USB Serial Port (COM?)" and "USB High Speed Serial Converter" from Device Manager manually.

# 7. FPL FLASH programming software

### 7.1 Introduction

The parameter file of the V850ES/HG2 device is installed automatically during installation of FPL GUI, folder <FPL install-path>\PRM. Nevertheless, newest version of parameter file for the µPD70F3707 device can by download from the NEC Electronics Web site.

Download the parameter file for the PG-FP4 from the following NEC Electronics Web site:

### http://www.eu.necel.com/updates

Copy the parameter file downloaded from the NEC Electronics Web site into sub-directory <FPL.EXE-install-path>\PRM created during GUI software setup (refer to **CHAPTER 6 SOFTWARE INSTALLATION**).

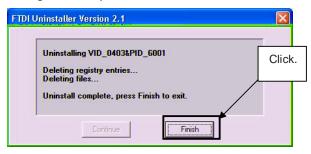

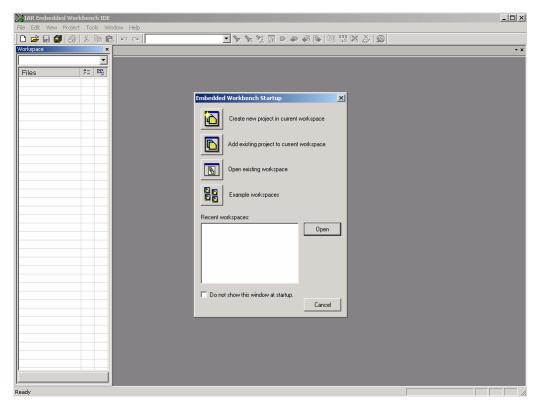

### 7.2 Starting up the GUI Software

GUI software startup

Select FPL.EXE from the start menu to start the FPL GUI software.

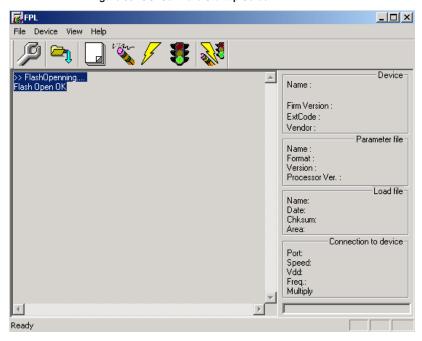

When the GUI software is started normally, the following screen appears.

Figure 36: GUI Software Main Window

This window consists of the following items:

| Name                                      | Display Information                   |

|-------------------------------------------|---------------------------------------|

| Menu bar                                  | Displays menu items executable by the |

| (displayed at the top)                    | FPL.                                  |

| Toolbar                                   | Displays frequently used commands as  |

| (displayed under the menu bar)            | icons.                                |

| Action log window                         | Displays an FPL action log.           |

| (displayed under the toolbar)             |                                       |

| Programmer parameter window               | Displays programming parameter        |

| (displayed to the right of the action log | settings.                             |

| window)                                   |                                       |

| Status bar                                | Displays status.                      |

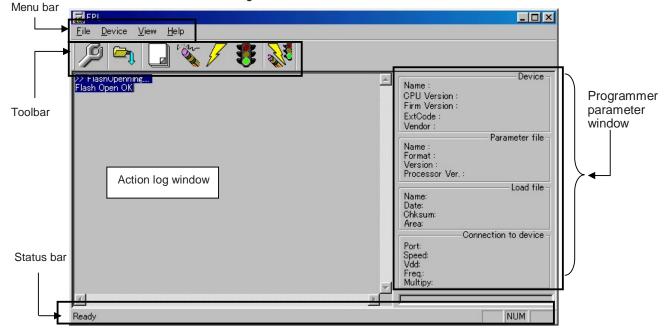

### 7.3 Toolbar

The toolbar contains buttons for starting the important procedures of the FPL.

Figure 37: Toolbar Buttons

#### 7.4 Menu Bar

Depending on the actual device status and device type, some menu items may be enabled or disabled.

### 7.4.1 [File] menu

Clicking the [File] menu displays the pull-down menu as shown below. This menu mainly contains commands related to file operation.

Figure 38: [File] Menu

### (1) [Load] command

The [Load] command allows you to select a program file.

The selected program file is programmed into the flash memory of the device by executing the [Program] command or [Autoprocedure(EPV)] command.

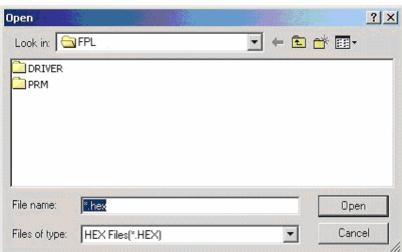

Figure 39: HEX File Selection Window

The file selection window for program loading displays the most recently used directory to which a user program has been loaded. After a user program is loaded, a checksum calculation is made and the result is displayed in the programmer parameter window.

[ Open button]

Selects a user program as a program to be written to the target device.

[ Cancel button]

Closes the window without selecting a program.

### (2) [Quit] command

The [Quit] menu is the command for terminating the FPL GUI software. Clicking  $\times$  on the right side of the task bar also terminates the FPL GUI software.

User settings are saved in the FPL.INI<sup>Note</sup> file, so that the GUI software starts up next time with the same settings.

Note FPL.INI is created in the Windows folder when Windows 98SE, Windows Me, or Windows XP is used.

When Windows 2000 is used, FPL.INI is created in the Winnt folder.

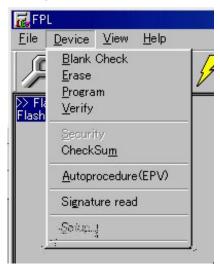

## 7.4.2 [Device] menu

Clicking the [Device] menu displays the pull-down menu as shown below.

This menu mainly contains commands for programming operations such as deletion, programming, and verification on the target device.

Figure 40: [Device] Menu

# (1) [Blank Check] command

The [Blank Check] command allows you to make a blank check on the target device connected to the FPL. If the flash memory of the target device is erased, a blank check is terminated normally. If the flash memory is not completely erased, the indication "not blank" is provided. Before starting programming, erase the flash memory of the target device.

# (2) [Erase] command

The [Erase] command erases the flash memory of the target device connected to the FPL. While the flash memory is being erased, the progress status is displayed in the action log window to indicate programmer operation.

The execution on the [Blank Check] command before the [Erase] command is executed follows the setting of 'Command options' of the Advance tab displayed by selecting [Device]  $\rightarrow$  [Setup].

Upon completion of [Erase] command execution, the GUI software displays the result of executing the command on the target device.

### (3) [Program] command

The [Program] command sends a specified user program to the target device and writes the program to the flash memory.

The execution of Verify operation for detecting an error in user program communication from the FPL to the target device after the execution of the [Program] command follows the setting of the 'Command options' on the Advance tab displayed by selecting [Device]  $\rightarrow$  [Setup].

During programming, the progress status is displayed in the action log window to indicate programmer operation. This progress status display window displays the progress status on target device programming by percentage.

Upon completion of [Program] command execution, the GUI software displays the result of executing the command on the target device.

### (4) [Verify] command

The [ $\underline{V}$ erify] command sends a specified user program to the target device connected with the FPL, and performs verification against the data written to the flash memory of the target device.

During verification, the progress status is displayed in the action log window to indicate programmer operation. This progress status display window displays the progress status of target device verification by percentage.

Upon completion of [Verify] command execution, the GUI software displays the result of executing the command on the target device.

### (5) [Security] command

This command is not supported.

# (6) [Checksum] command

The [Checksum] command reads the checksum value of the target device connected with the FPL.

This value differs from the value displayed in the parameter window of the main window.

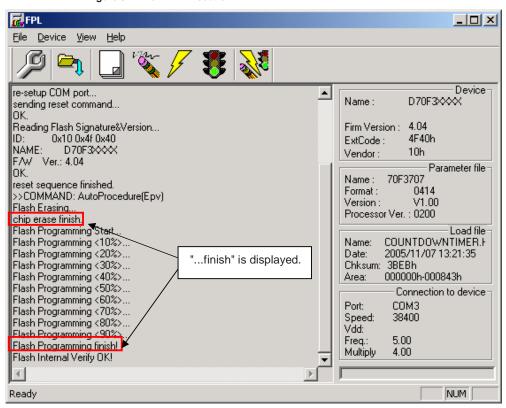

### (7) [Autoprocedure(EPV)] command

The [Autoprocedure(EPV)] command executes the [Erase] command, [Program] command and [Verify] command in succession.

When a user program is to be resent to the target device for comparison with the data written to the flash memory of the target device because of a user program communication error, execute the [ $\underline{P}$ rogram] command by selecting [ $\underline{D}$ evice]  $\rightarrow$  [ $\underline{S}$ etup] and specifying 'Command options' on the Advance tab, then set the automatic execution of the [Verify] command.

During EPV execution, the progress status is displayed in the action log window to indicate programmer operation. For a selected command, its execution operation, and messages, refer to **CHAPTER 8 HOW TO USE FPL**.

Upon completion of [Autoprocedure(EPV)] command execution, the GUI software displays the result of executing the command on the target device.

#### (8) [Signature read] command

The [Signature read] command reads the signature information (device name, flash memory information, and so forth) of the target.

### (9) [Setup] command

The [Setup] menu allows you to make settings related to flash memory rewriting according to the user environment and to set command options. Each time the GUI software is started, the most recently used parameter file (.PRM) is read and the settings are displayed. The [Setup] menu allows you to modify the settings of items other than those items consisting of shadowed characters according to the user environment.

### (a) Standard setup

This menu is used to set the environment for rewriting the flash memory of the target device.

The mode of communication with the target, the operating clock, and so forth differ depending on the device used. For details, refer to the manual of the device used, when making settings.

The window shown below is opened.

Figure 41: Device Setup Window - Standard

This window shows all basic options that can be set in accordance with the user environment and target device.

[OK] button]

Clicking the OK] button saves the settings on the Standard and Advance menus and closes the window.

[Cancel] button]

Clicking the Cancel button closes the window without saving the settings on the Standard and Advance menus.

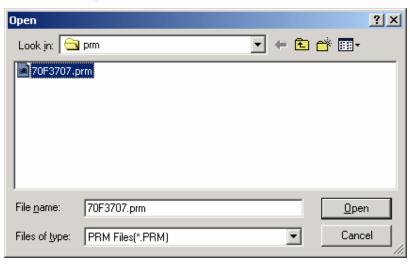

### <1> Parameter file

This file holds parameters and timing data required to rewrite the flash memory of the target device. Do not modify the data in the parameter file because the data is related to the guarantee of rewrite data.

The parameter file is protected by the checksum function. If the checksum result indicates an error, the FPL does not accept the parameter file.

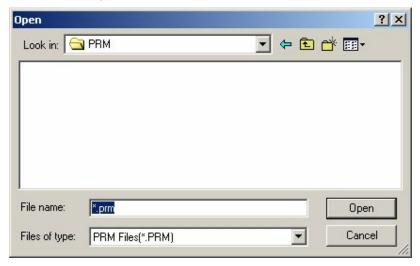

Figure 42: Setup Window - Parameter File Selection

Figure 43: Parameter File Selection Window

[ PRM File Read button]

A window for specifying a parameter file is displayed. Specify a desired file then click Open.

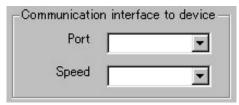

### <2> Communication interface to device

"Communication interface to device" is used to select a channel for communication between the *EB-V850ES/HG2-EE* board and host machine.

Figure 44: Setup Window - Communication interface to device

#### [Port list box]

Select a channel for communication between the *EB-V850ES/HG2-EE* board and host machine.

COM1 to COM16

Remark Selectable ports can be checked using Device Manager. For details, refer to CHAPTER 6.5 Confirmation of USB Driver Installation.

### [Speed list box]

Select a communication rate for the selected communication channel from the following:

- 9600 bps

- 19200 bps

- 38400 bps

Remark For selectable communication rates, refer to the user's manual of the device used.

# <3> Supply oscillator

"Supply oscillator" is used to select a clock that determines programming, data transfer, and a transfer rate.

### <4> Operation Mode

The setting of "Operation Mode" may divide the flash memory of some target devices into blocks or areas.

This menu is used to select an operation mode of the flash memory. Some devices do not have the block and area division modes, and some devices have only one of the modes. In these cases, a nonexisting mode is unchoosable.

Figure 46: Setup Window - Operation Mode

### [When Chip is selected]

The entire flash memory area of the target device is subject to rewrite processing.

### [When Block is selected]

Specify the Block number range subject to rewrite processing by using Start/End. The Start/End list boxes display the Block numbers where the flash memory of the target device is configured.

### [When Area is selected]

Specify the Area number range subject to rewrite processing by using Start/End. The Start/End list boxes display the Area numbers where the flash memory of the target device is configured.

### [Show Address check box]

Specify whether numbers or addresses are displayed in the Start/End list boxes.

If this check box is checked, addresses are displayed.

If this check box is not checked, numbers are displayed.

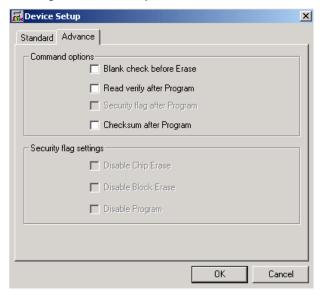

### (b) Advance setup

The Advance setup menu is used to specify the command options and security flag settings.

When "Advance" is clicked, the following window is displayed:

Figure 47: Device Setup Window - Advance

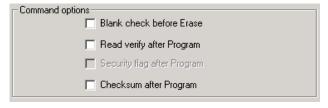

### <1> Command options

This dialog box is used to specify the FPL flash processing command options.

Figure 48: Setup Window - Command options

[Blank check before Erase check box]

If this check box is checked, blank check is made before the Erase command or EPV command is executed.

If the result of a blank check indicates OK, erase processing is not executed.

### [Read verify after Program check box]

If this check box is checked, write data is sent from the programmer after execution of the Program command and EPV command, then the data is verified against the data written to the flash memory.

[Security flag after Program check box] Not usable

# [Checksum after Program check box]

If this check box is checked, the flash memory checksum value of the target device is read from the target device after execution of the Program command and EPV command.

This value differs from the value displayed in the parameter window of the main window.

#### <2> Security flag settings Not usable

# 7.4.3 [<u>V</u>iew] menu

Clicking the [View] menu displays the pull-down menu shown below.

This menu contains commands for setting whether to display the toolbar and status bar.

# (1) [Toolbar] command

Checking the  $[\underline{\mathsf{T}}\mathsf{oolbar}]$  command displays the toolbar. Unchecking the command hides the toolbar.

# (2) [Status Bar] command

Checking the [Status Bar] command displays the status bar. Unchecking the command hides the status bar.

# 7.4.4 [Help] menu

Clicking the [Help] menu displays the following pull-down menu:

Figure 50: [Help] Menu

# (1) [About FPL] command

The [ $\underline{A}$ bout FPL] command opens the program entry window as shown below and indicates the version.

Clicking OK terminates the display.

Figure 51: About FPL Window

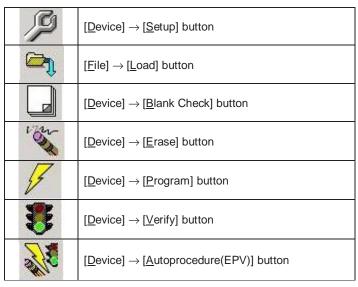

# 7.5 Programmer Parameter Window

This window displays the settings of the programming parameters.

Figure 52: Programmer Parameter Window

### [Device]

Updated after communication with the target device to display information about the target device.

### [Parameter file]

Updated after [Setup] command execution to display information about a read parameter file.

#### [Load file]

Updated after [Load] command execution to select information about a selected program file.

# [Connection to device]

Updated after [Setup] command execution to display information about the connection with the target device.

# 8. How to use FPL FLASH programming software

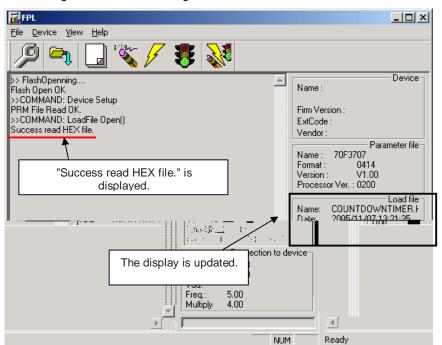

This chapter explains the basic operations of the FPL GUI for programming the *EB-V850ES/HG2-EE* board. This chapter covers how to start the system, execute the EPV command, and program the target V850ES/HG2 device.

The conditions of the series of operations described in this chapter are as follows:

### Hardware configuration of EB-V850ES/HG2-EE:

Board : EB-V850ES/HG2-EE

CPU : V850ES/HG2 Target device : μPD70F3707 Clock : 5 MHz

Clock : 5 MHz Voltage level : 5 V

### Software configuration of FPL:

Parameter file: 70F3707.PRM

Clock setting : 5 MHz Multiplied by 4 Port : COM3 (38400 bps)

Operation mode: Chip

Write HEX : CountDownTimer.hex

Option setting : Blank check before Erase

### (1) Installing the FPL GUI software

Install the FPL GUI software on the host machine you are using, by referring to **CHAPTER 6 SOFTWARE INSTALLATION** (if the software has not been installed yet).

### (2) Installing the driver

Install the USB driver on the host machine you are using, by referring to **CHAPTER 6 SOFTWARE INSTALLATION** (if the driver has not been installed yet).

#### (3) Installing the parameter file

The parameter file for the V850ES/HG2 device is installed automatically during installation of FPL GUI, folder <FPL install-path>\PRM. Nevertheless, newest version of parameter file for the uPD70F3707 device can by download from the NEC Electronics Web site.

Download the parameter file for the PG-FP4 from the following NEC Electronics Web site:

#### http://www.eu.necel.com/updates

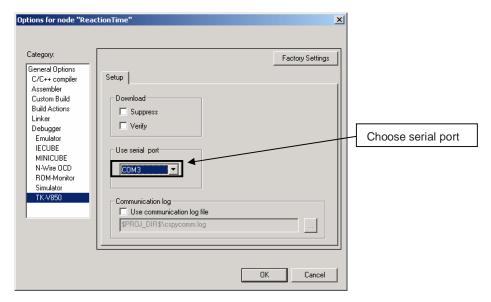

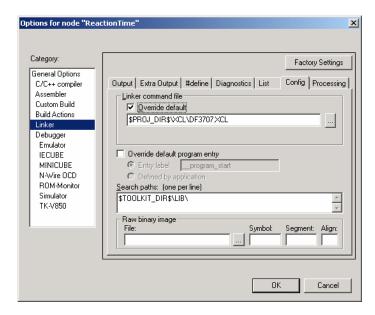

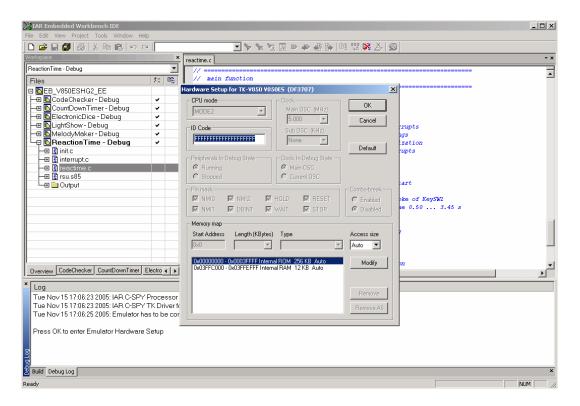

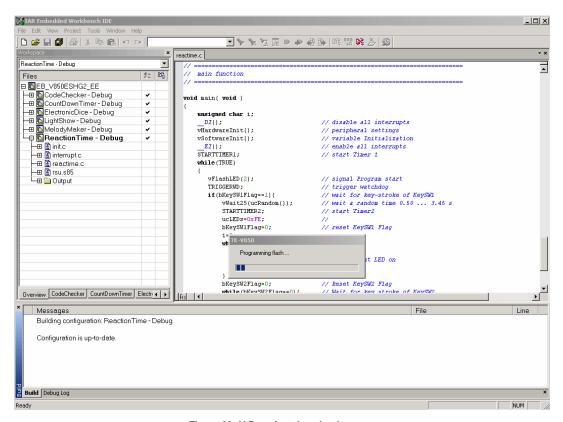

Copy the parameter file downloaded from the NEC Electronics Web site into sub-directory <FPL.EXE-install-path>\PRM created during GUI software setup (refer to **CHAPTER 6 SOFTWARE INSTALLATION**)..